Other Parts Discussed in Thread: AM5748

Hi, we are designng a board using 66AK2G12 and we want to implement a QSPI.

I found this answer K2G PCB Guidlines for QSPI (https://e2e.ti.com/support/processors/f/791/t/541174) and tried ti simulate what you suggest.

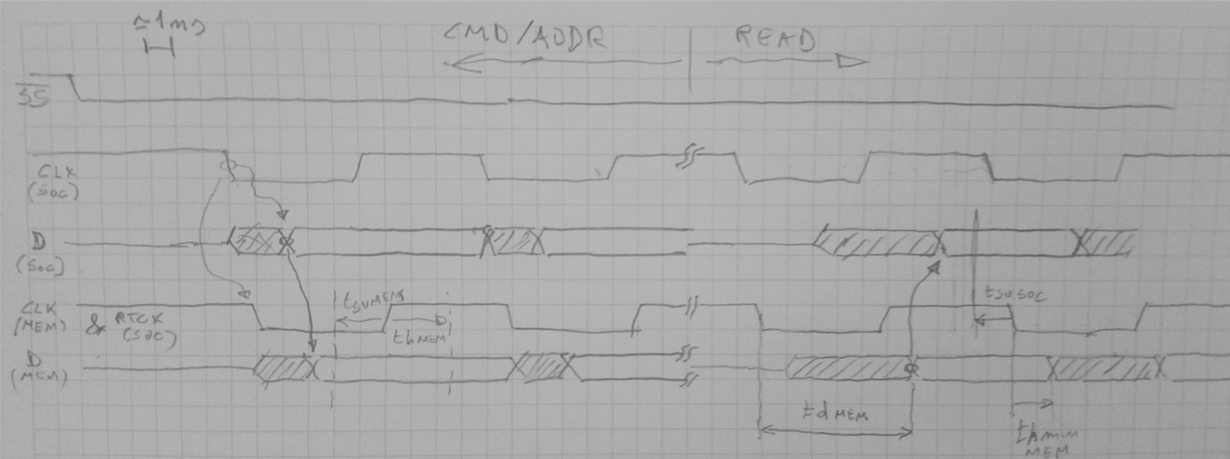

The problem is that while the 66AK2G12 QSPI_RCLK signal is beautiful the memory CLK input is horrible.

What should I do?

Regards,

Roberto Vigliarolo