Tool/software: Code Composer Studio

HI

I want to configure a shared memory(MSMCRAM) .

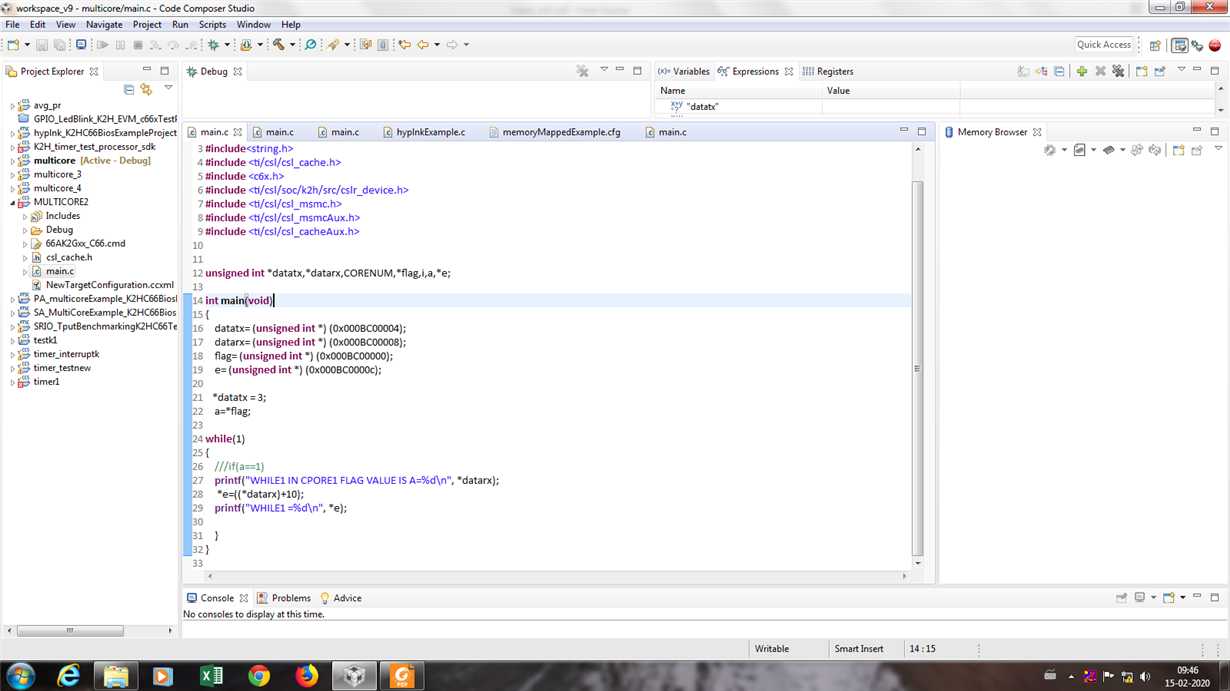

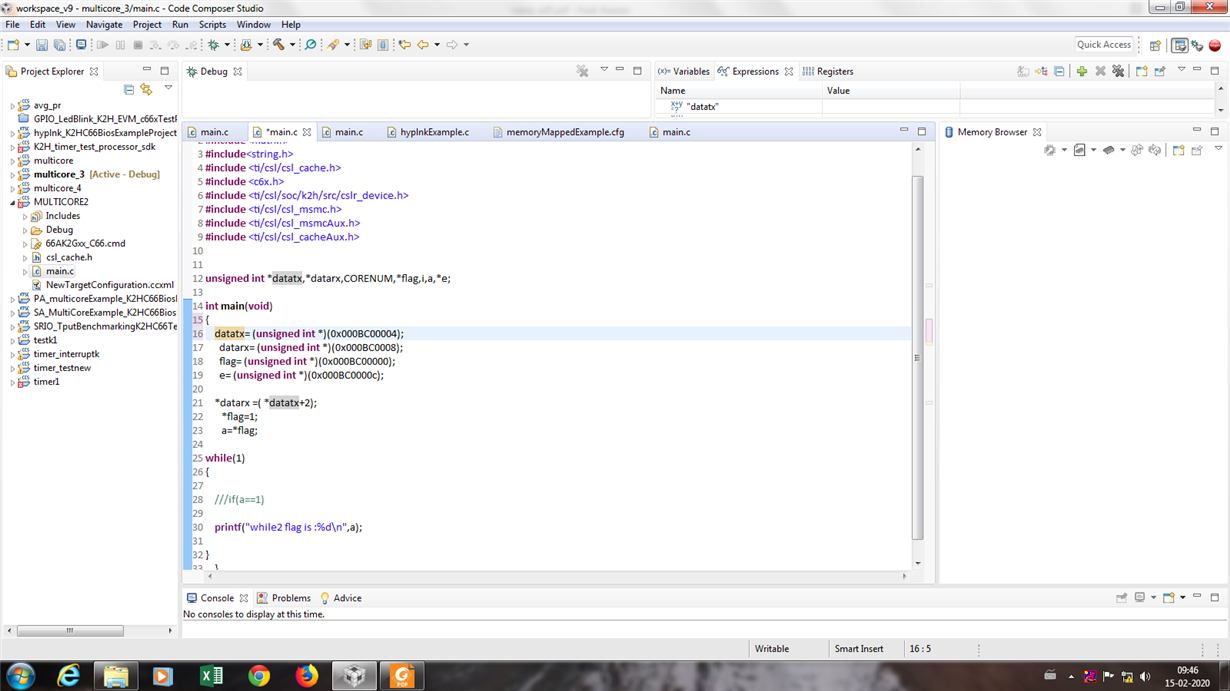

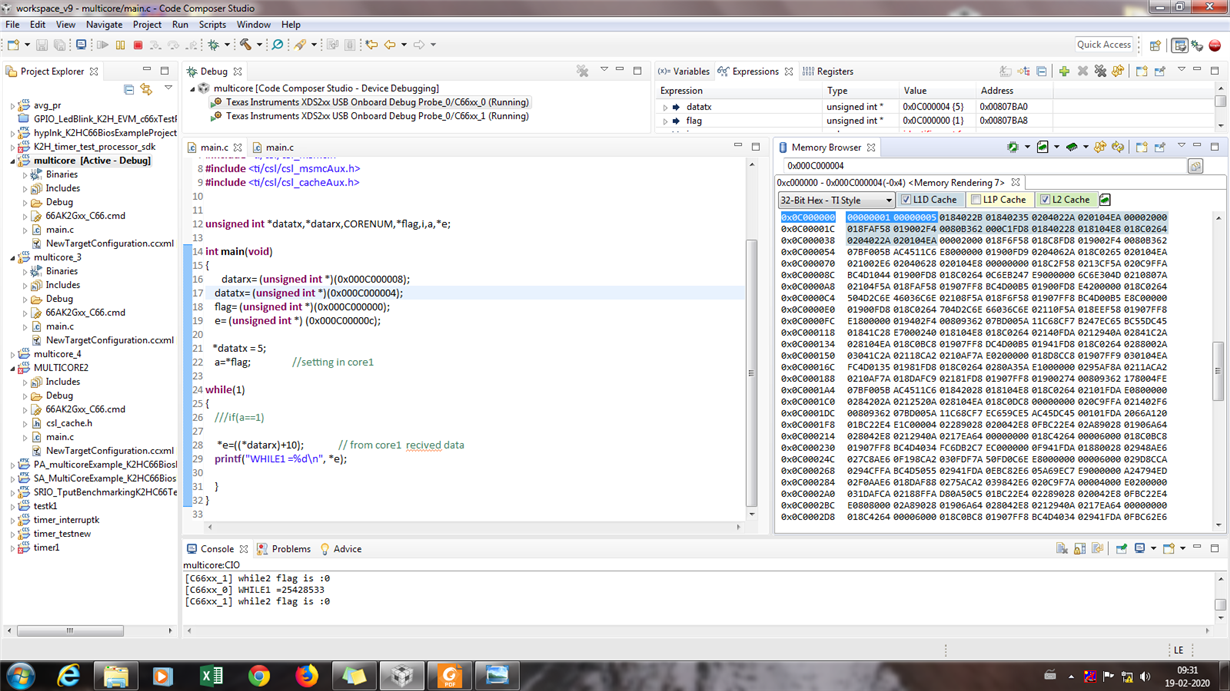

1. I am using multi core processor i.e, i want to use two cores I have two different projects one project in core_0 and another in core_1, in core_0 have some data that data should be used in core_1 and again that data is used by core_0 for that I am using MSM RAM to access the data from both the processor.

2. The address is defined in data sheet for MSMRAM from 0XC000000 to C5FFFFF can I use this memory by using pointers ? OR I should configure any other register ?

3. I am using the address directly but that data is not fetched by that address in both the cores, should I configure any memory of MSM in .cfg file? and .c fie?

Can anyone suggest me how to configure MSMRAM and share any example projects if you have to refer .

THANKS AND REGARDS

KAVYA M U