Tool/software: TI C/C++ Compiler

Hi TI members:

For project request, we are studying how to enable PCIE internal clock output function.

There is some code about pcie0 in k3-j721e-main.dtsi

974 pcie0: pcie@2900000 {

975 compatible = "ti,j721e-pcie";

976 reg = <0x00 0x02900000 0x00 0x1000>,

977 <0x00 0x02907000 0x00 0x400>,

978 <0x0 0x02905000 0x0 0x00000400>;

979 reg-names = "intd_cfg", "user_cfg", "vmap";

980 #address-cells = <2>;

981 #size-cells = <2>;

982 ranges;

983 ti,syscon-pcie-ctrl = <&pcie0_ctrl>;

984 max-link-speed = <3>;

985 num-lanes = <2>;

986 power-domains = <&k3_pds 239 TI_SCI_PD_EXCLUSIVE>;

987 clocks = <&k3_clks 239 1>;

988 clock-names = "fck";

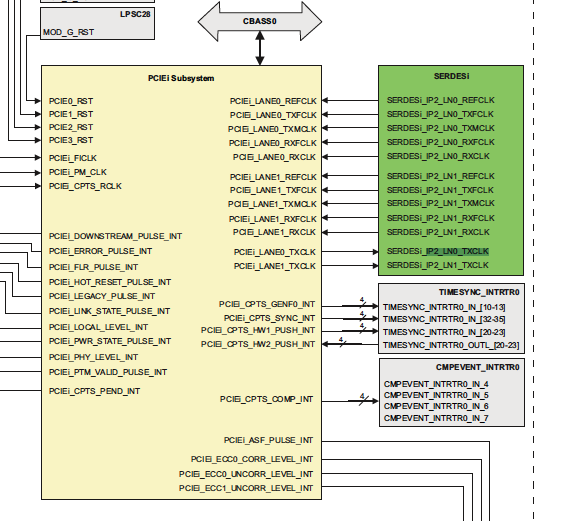

I am not sure is this "clocks = <&k3_clks 239 1>;" just mean below clock pin

So I have a few questions,

Q1: Is my understand about the clocks k3_clks right?

Q2: is there any document to explain what means of the number parameters(239 1) in clocks?

Q3: how to set PCIE_REFCLK1 is output?

if my description is not clean,

please let me know,

Thanks a lot!!!

BR

Sentinen Chen