Hello all!

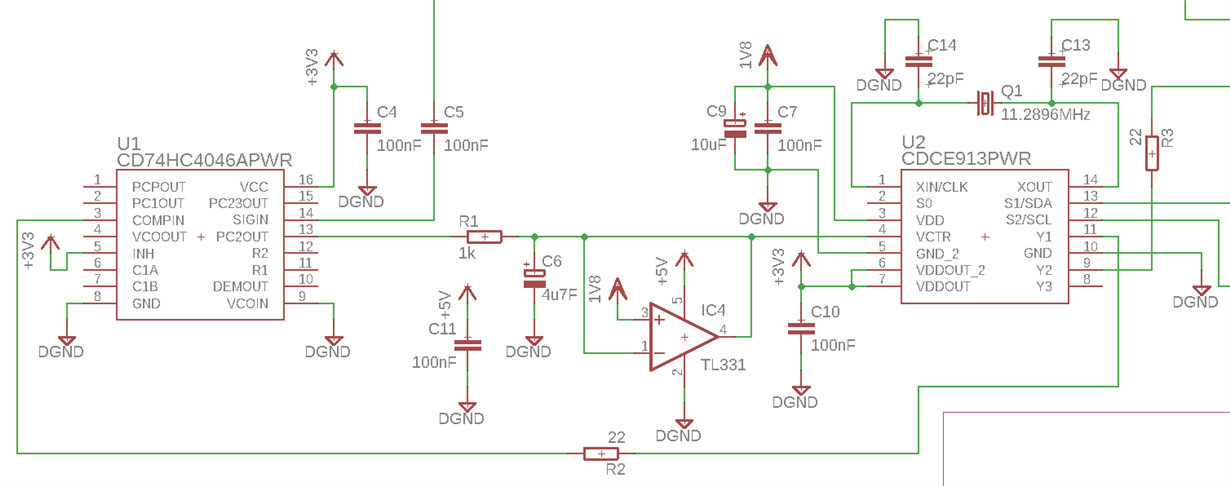

I'm trying to implement Application Note SCAA088 to generate a master clock from a I2S source (from a CD player). But I'm having some troubles getting it to work as the PLL is not locking (and thus the output is running freely and not in sink with the input source). This is my schematic:

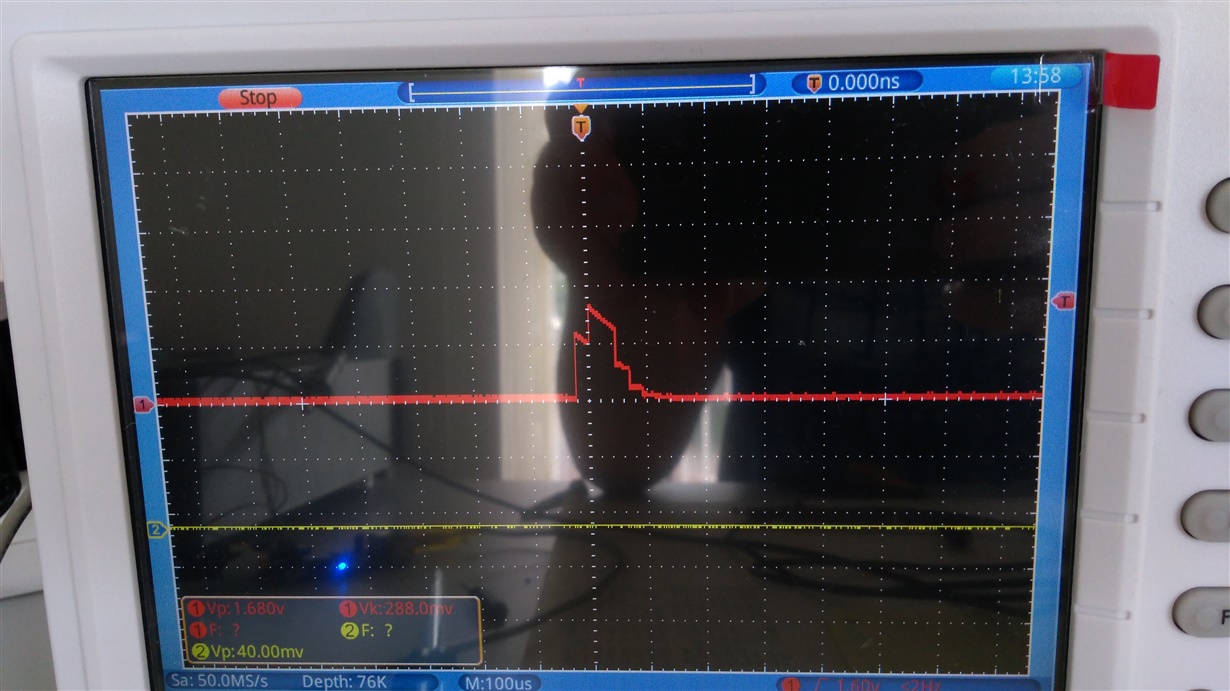

I've set the output dividers properly to the desired values (Y1 outputs a clock of 44.1KHz, Y2 has half the crystal frequency) and the CDCE913 is configured to operate in VCXO mode. But it seems like the signal from the phase comparator is not arriving properly at the CDCE913. (it's flat zero). when removing the RC-filter, this is what I see on the oscilloscope:

Still no difference in the locking of the PLL however... Does anyone have some pointers for my to try?