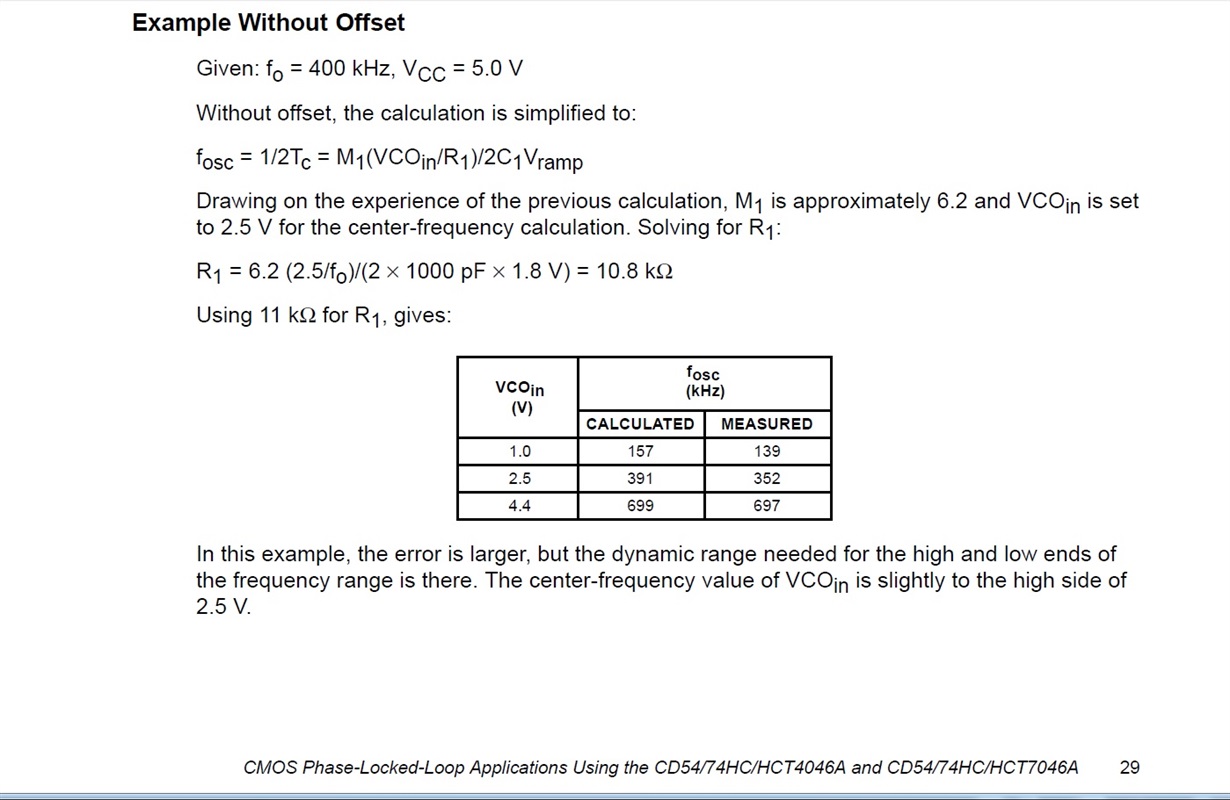

Good day. I don't know if its the right forum to post this question. I am designing a PLL for my specific application with a lock in range of 20kHz-200kHz. I am referring to your application report SCHA003B - September 2002 for guidelines on designing external components on CD4046. I am currently using the CD4046B CMOS PLL chip. This design example provided, can someone show the Test Circuit of this example which I can get the same result as in the table shown. Thank you for the help.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.