Hi everyone,

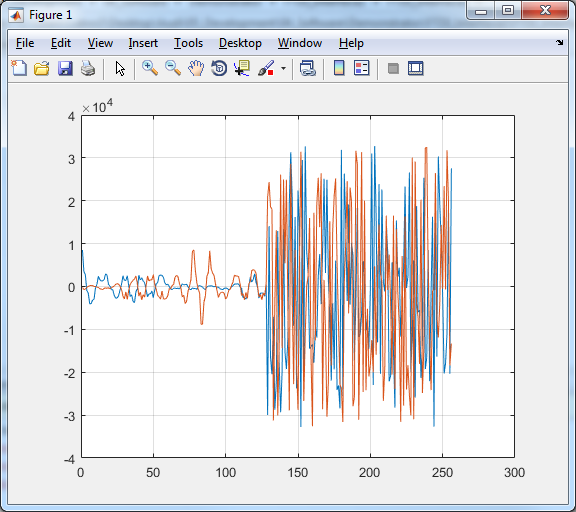

I seem to have a very strange effect on my board using the AWR1243. It seems that reading data from the LVDS lanes into the PC works fine. When I look at the samples they seem to be quite similar between the antennas - I guess that is ok as the scenario is quite similar for all antennas. However, there is a random shift in the samples. For example when I see a certain "peak" in the time domain, for one antenne it is at the beginning, for one other it is at the end, and a third one has it somwhere in the middle of the stream.

I cannot give much more information as I don't know what may cause that issue. I am not allowed to publish the source code of the project here. I am just askinig for hints where I may have a look at.

I guess I am initalizing the ADC/Lane settings wrong. But is there some miss-configuration where he migh drop bunches of samples? Can I detect if he dropped samples?

It took me quite some time to figure out a "working" configuration if ADC/Lane settings. I am using the COMPLEX_1X mode (2X does not work, what is the difference anyway?). I set the number of samples to 256 in rlProfileCfg_t, but I had to set the number of samples to 512 in radar_setFrameConfig. Why? Is that wrong? The documentation does not seem to make a difference between them.