Hi,

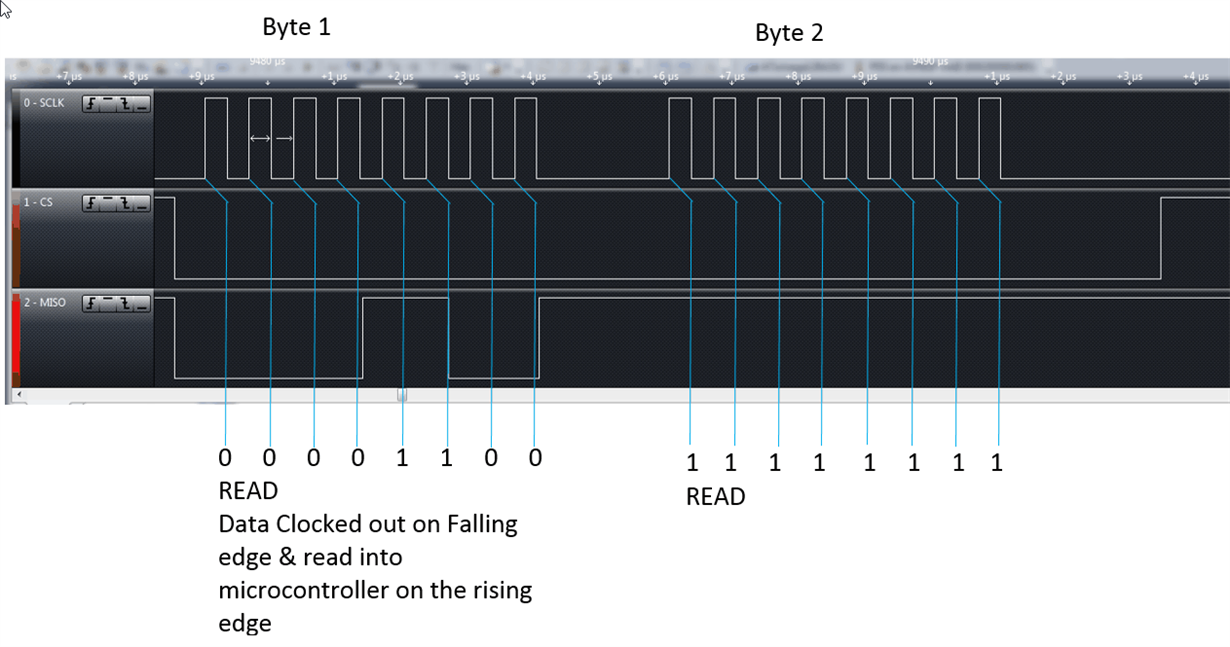

LM70 data sheet shows timing diagrams where CS is driven from High to Low to select the device. In these diagrams the clock is shown as LOW at the time CS is driven low.

There is a warning:

"This should not be done when SC is changing from a low to high state".

BUT

What happens if the CLK is HIGH at the time CS is driven low.

One obvious thing is that the first CLK edge that the LM70 will see is HIGH to LOW whereas if CLK is LOW at the time CS is driven low then the first CLK edge the LM70 will see is a LOW to HIGH.

BUT what is the effect of this?

The problem we are experiencing is that the device is somehow getting into the power down state. It always reads as 1000 0001 0000 00XX. According to the data sheet, this is the manufacturer’s ID. XX is tristate. Just ignore that.

Any help on resolving this would be appreciated.

Thanks, Frank