Other Parts Discussed in Thread: TMP101

I've by now successfully integrated a TMP007 but I can't seem to find any info on power-on reset and software reset timing in the datasheet and the device only works propely when long delays are introduced - which doesn't feel right.

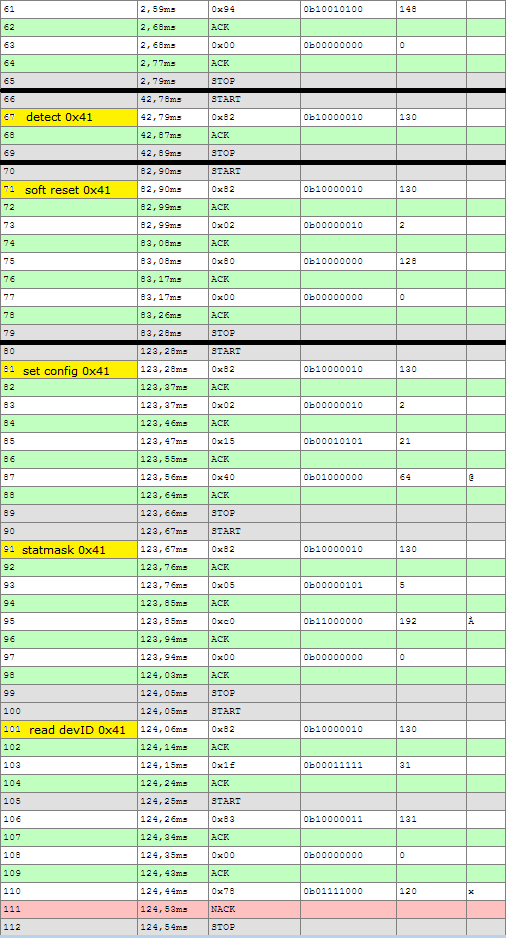

Our device firmware does some I/O testing to detect stuck high, low and shorted I2C lines, ends with a stop condition, then proceeds with attempted read / write operations to detect other devices (MCP4827, TMP101) and initializes those. I2C clock is 100kHz.

TMP007 devices are scanned by sending address + write and a test for ACK, followed by a stop condition.

bool TMP007Device::detect(void)

{

i2c_c_write_start(_addr );

bool ack = i2c_c_getAck(TW_MT_SLA_ACK);

i2c_stop();

return ack;

}

Some of the preceding bus transactions, the detection itself or the issuing of a software reset cause the device to NACK further immediate commands. None of these contain bus errors. Only when delays (e.g. 40ms) are introduced between the stop and subsequent start conditions this behavior is no longer seen.

What am I missing?