Hi,

We have a PCB with two AFE5818, both have the same electrical schematic configuration and share the same power supplies.

One of them is not responding to our SPI communication.

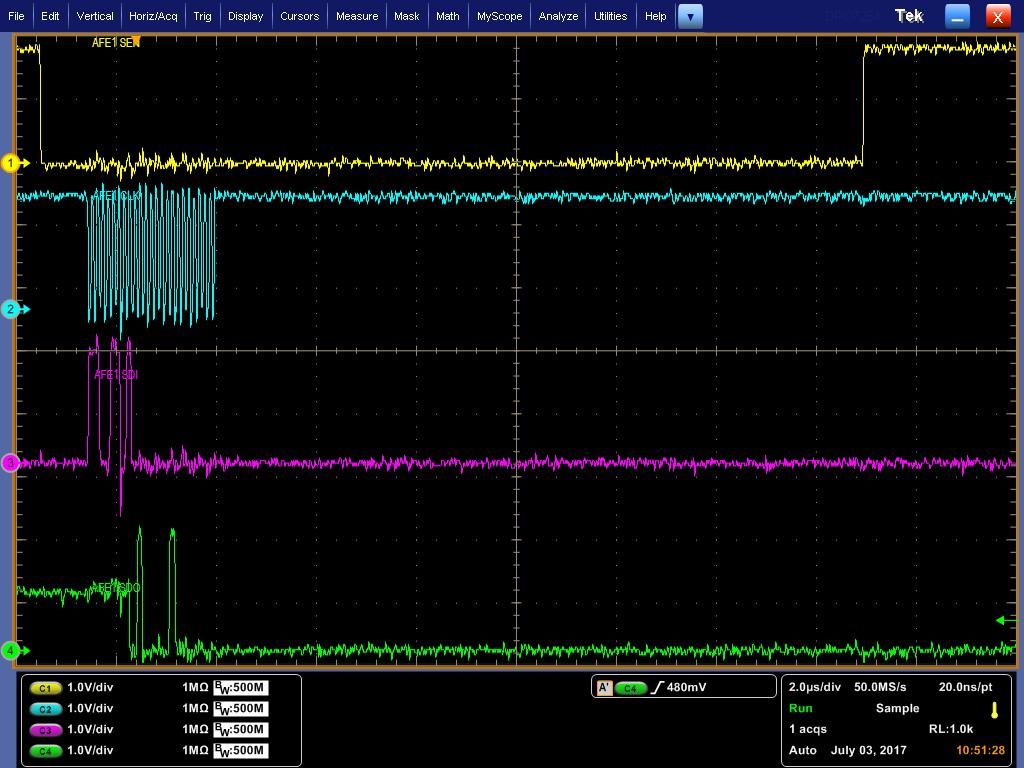

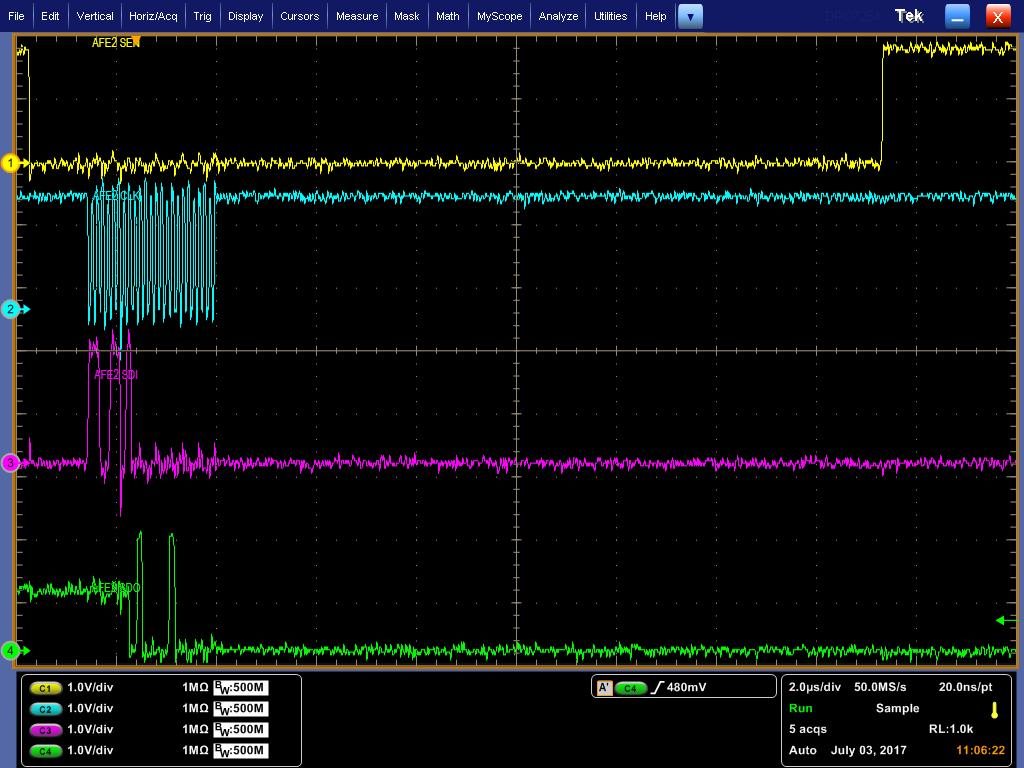

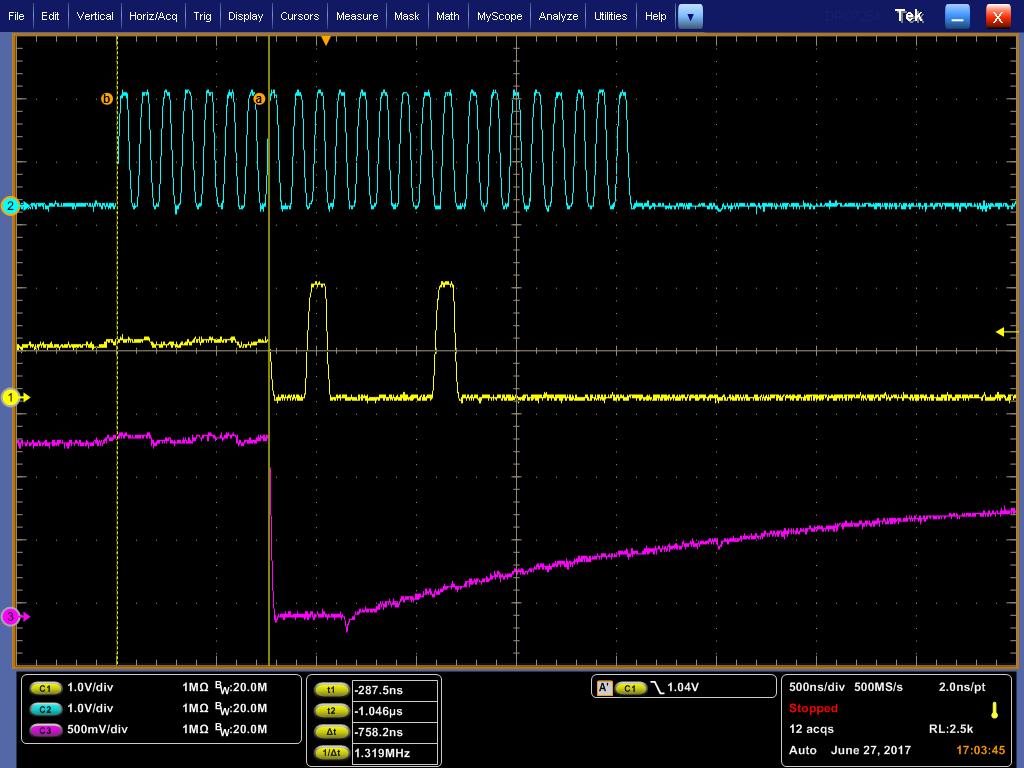

- All SPI signals are the same on both AFE’s

- I/O’s are configured correctly

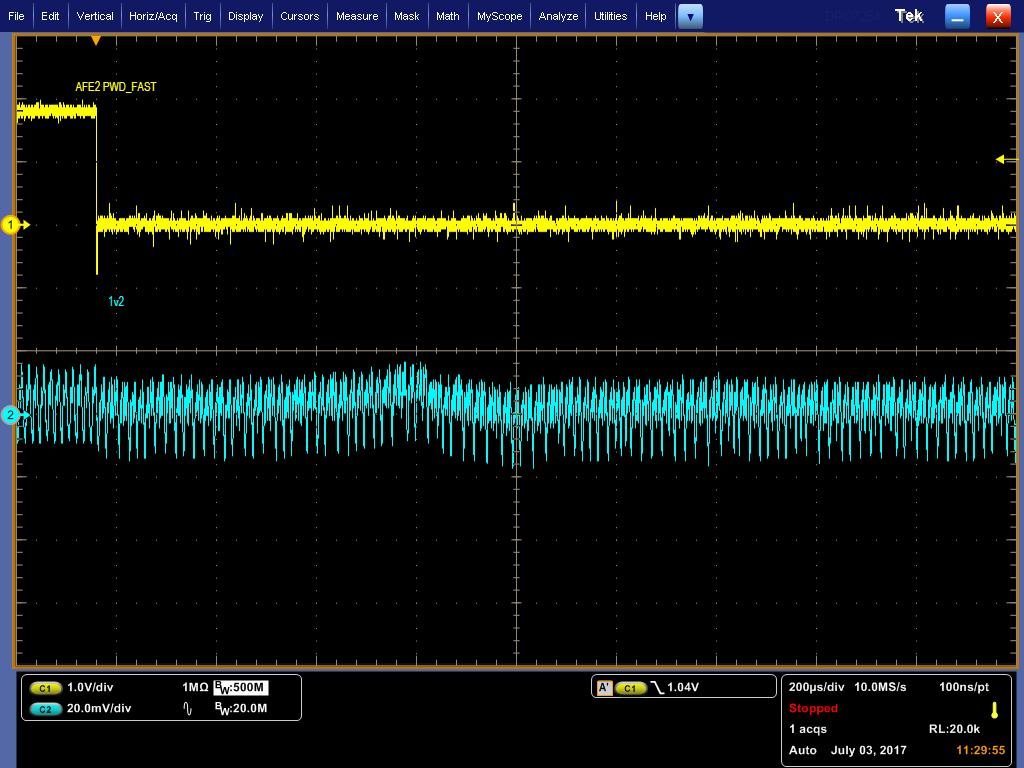

- power supply ripple on all rails is <20mV

- No power drop was detected on all rails after configuration and Power Down pin release.

- Clock seems to behave the same on both AFE’s

- We tried connecting all AFE2 to AFE1 signals (except for their SDO)

- AFE1 SDO on power-up measure approx. 0.3v while the BAD AFE2 SDO is 1.8v

Attached plot screen shot and layout & schematics.

I would appreciate your help with this issue, or even a hint on what could make the 2nd AFE act the way it does (drops as the 1st is doing, and immediately release the line)

Best Regards,

Rotem

Edit: Design files removed as per customer request.