Part Number: TDC1000-TDC7200EVM

Hi, team

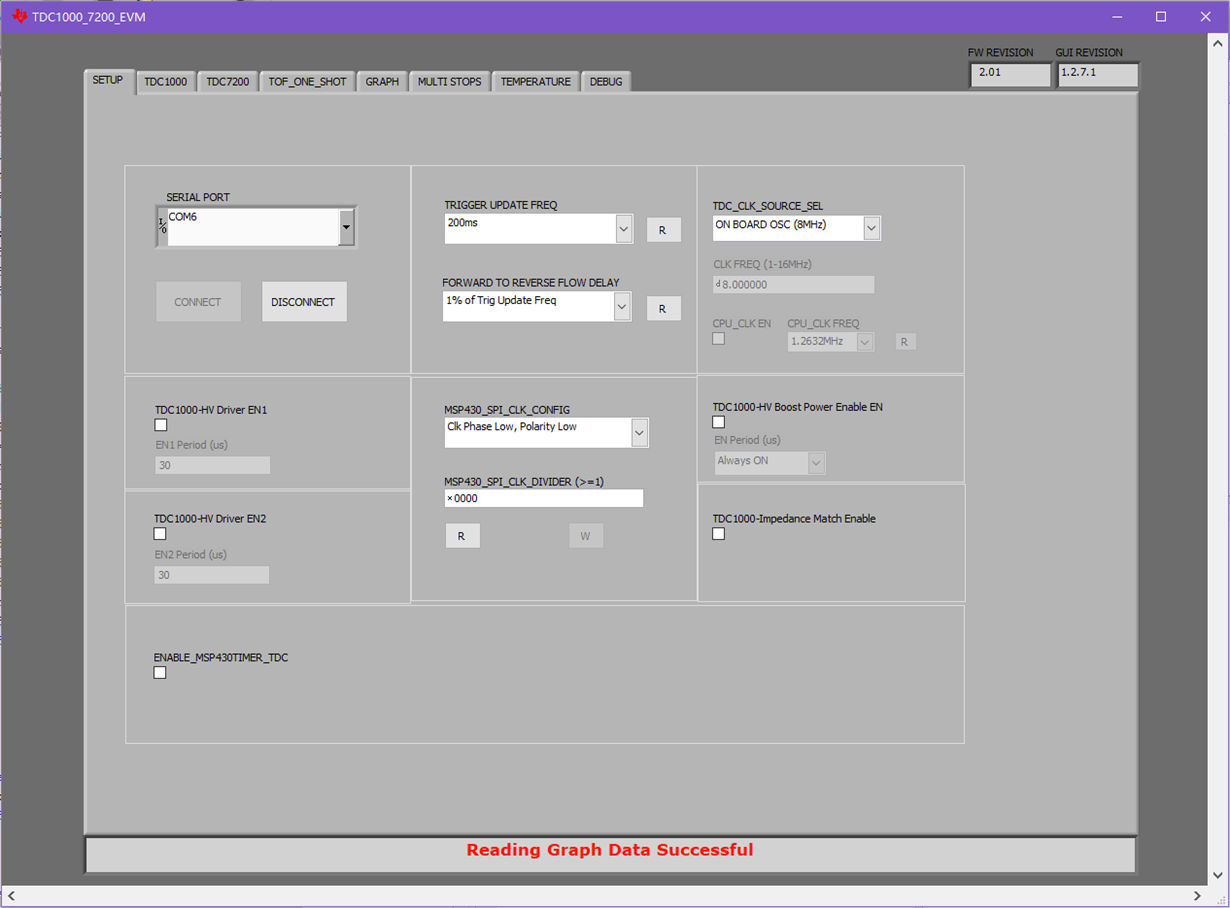

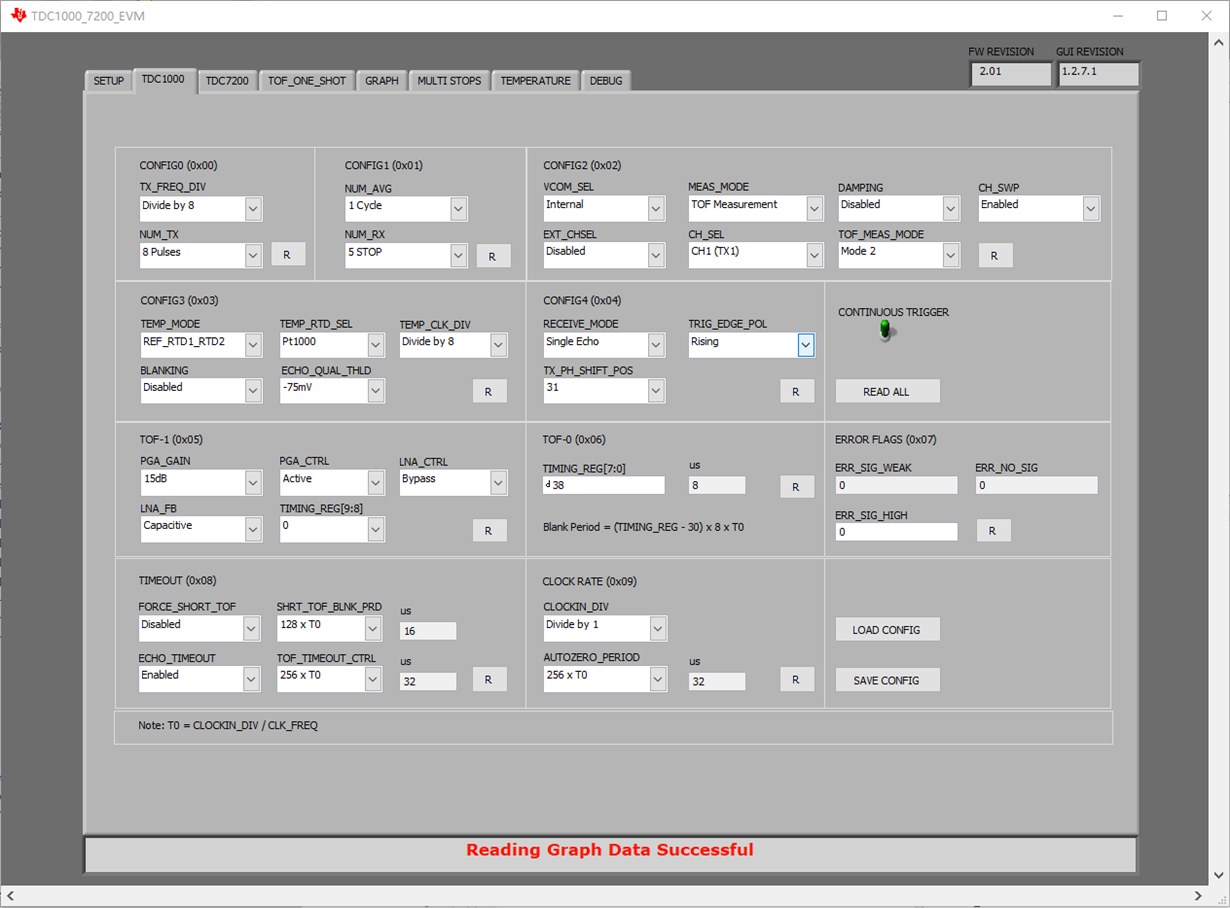

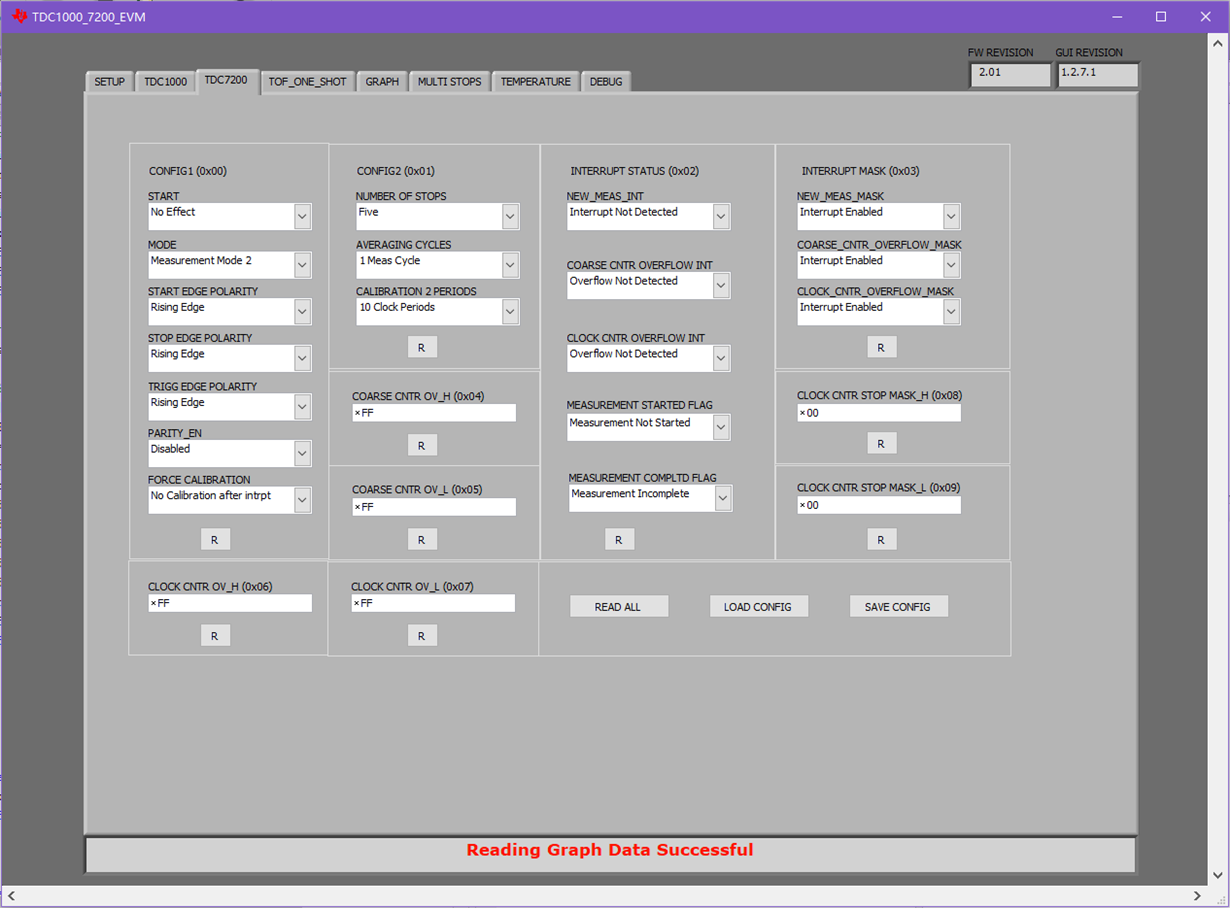

I bought a TDC1000-TDC7200EVM last week and it showed a great performance in zero flow test.

I also designed a TDC based board months ago, which uses a TDC-GP21 as stop watch and TDC1000 as AFE. But test result is even worse than our early design with separate anlog circuits, as my workmate described in  .

.

My design with TDC1000 is showed in the attach. Main difference with EVM is the stop watch, while TDC-GP21 also has a resolution up to 50ps. So I don't think this will cause that large error. I have concluded some probable problems as following:

1. TDC-GP21 has a external 4MHz osillator while TDC1000 uses a 4MHz clock from MCU;

2. TDC1000 was supplyed by two 3% linear regulators(3V and 5V);

3. Perhaps PCB layout problem?

Problem 1 I have conducted various tests, but still found nothing. I wonder if you can find any vital problem through the design or have any recommended solutions.

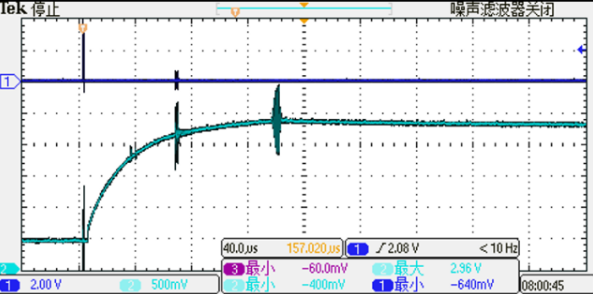

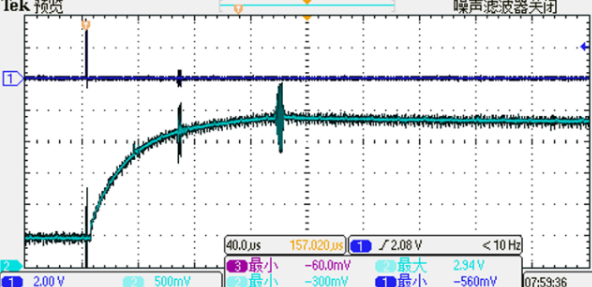

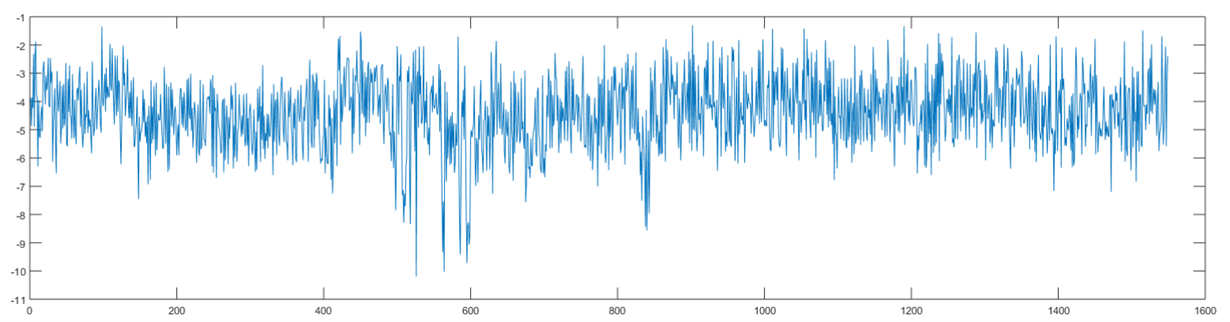

I also have some problems with the signal. I found that the COMP-IN signal in my own design showed a fall down trend in a measurement cycle, as shown in the figure:

Problem 2 Why does VCOM (or COMP-IN) falls down before the end of the test? BTW, why I can't even see the charging process when using the EVM?

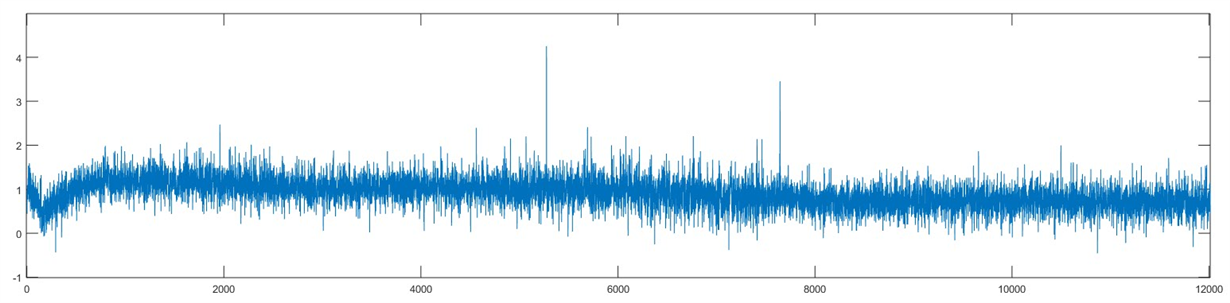

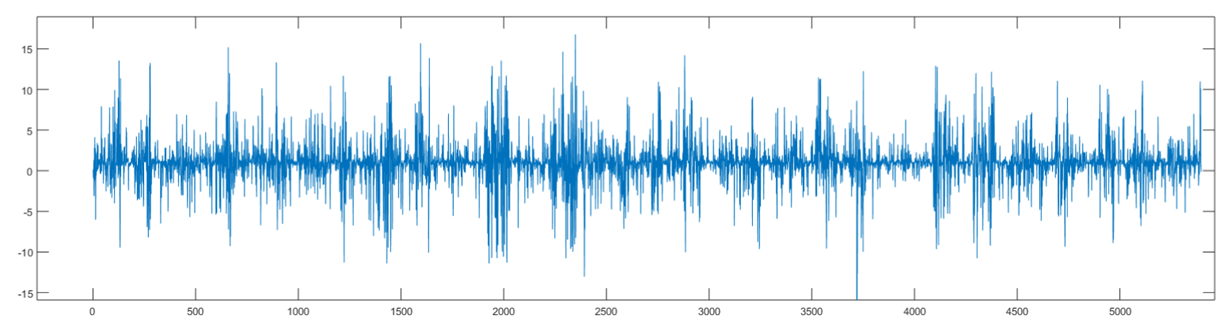

Another problem is that, when I connect UART pins of my board to a TTL-to-RS232 converter(especially the supply pin), the noise on COMP-IN signal will be much larger than before, as shown in the figure:

Problem 3 I have found that the noise comes from VCOM pin, but I cant understand why. Could you please explain that?

Best wishes!