Hi Sirs,

Sorry to bother you.

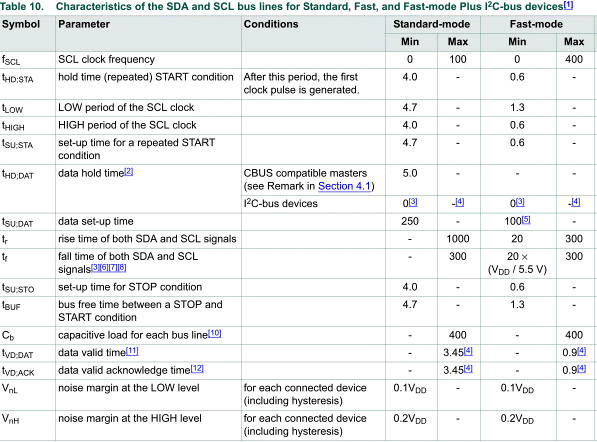

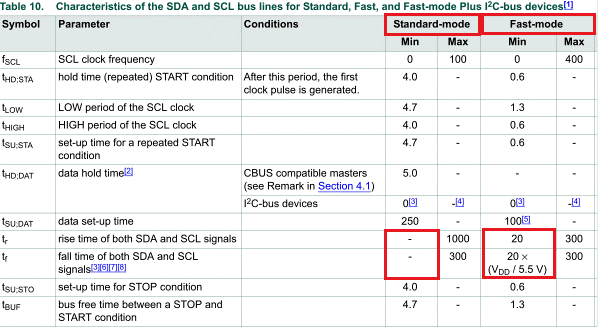

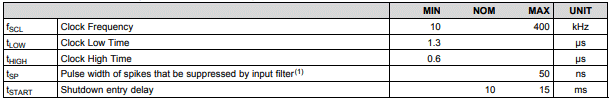

Because HDC2010 I2C datasheet timing requirements information are not clearly.

So could you help confirm HDC2010's I2C is compliant with the I2C standard spec (UM10204) and is backward compatible with Standard-mode (100bits/s)?

Thanks!!