Other Parts Discussed in Thread: LP87702-Q1,

Hi,

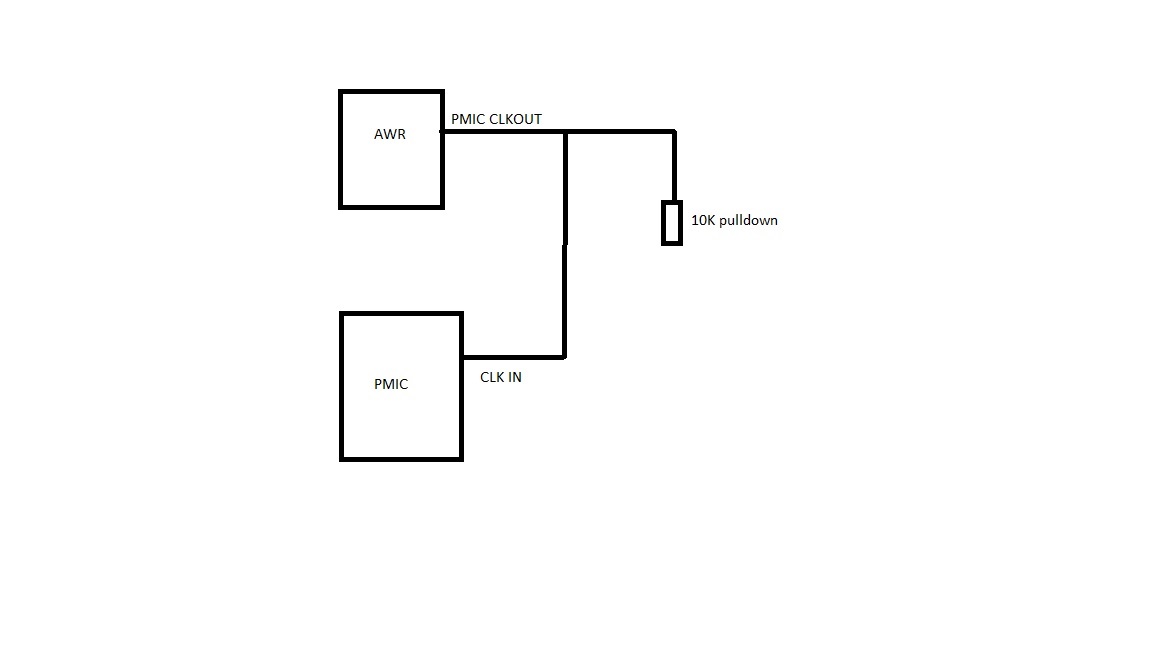

The reference design has the signal, AR_PMIC_CLKOUT_SOP2 pulled down for "FUNC" mode and could be connected to the PMIC_CLK (to the LP87702-Q1's CLKIN) via R97, but this function, "PMIC_CLK' is disabled on the EVM.