Hi BU Experts,

My customer is using MUX508.

They found an issue about the break-before-make delay.

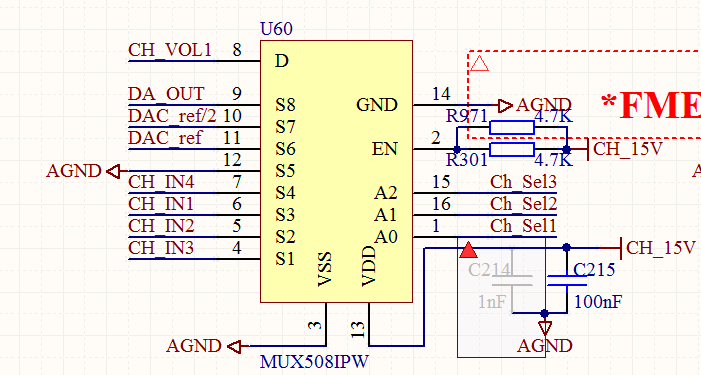

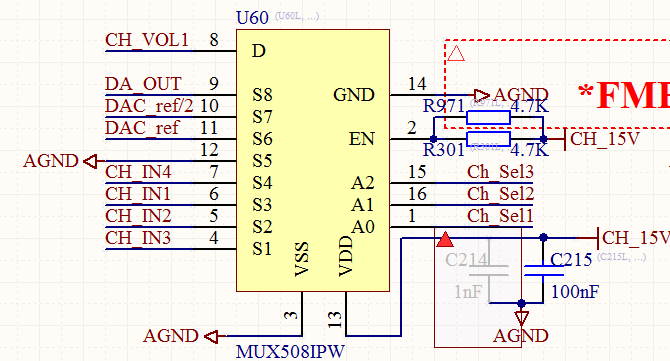

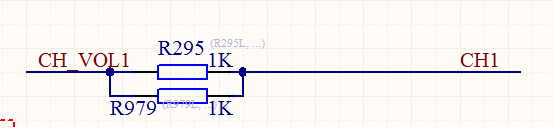

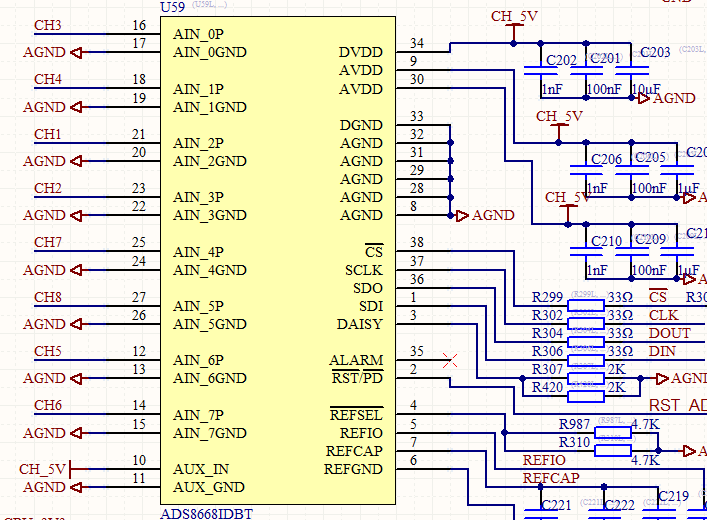

Below is the SCH. VDD=15V, S3=15V, S4=0.76V.

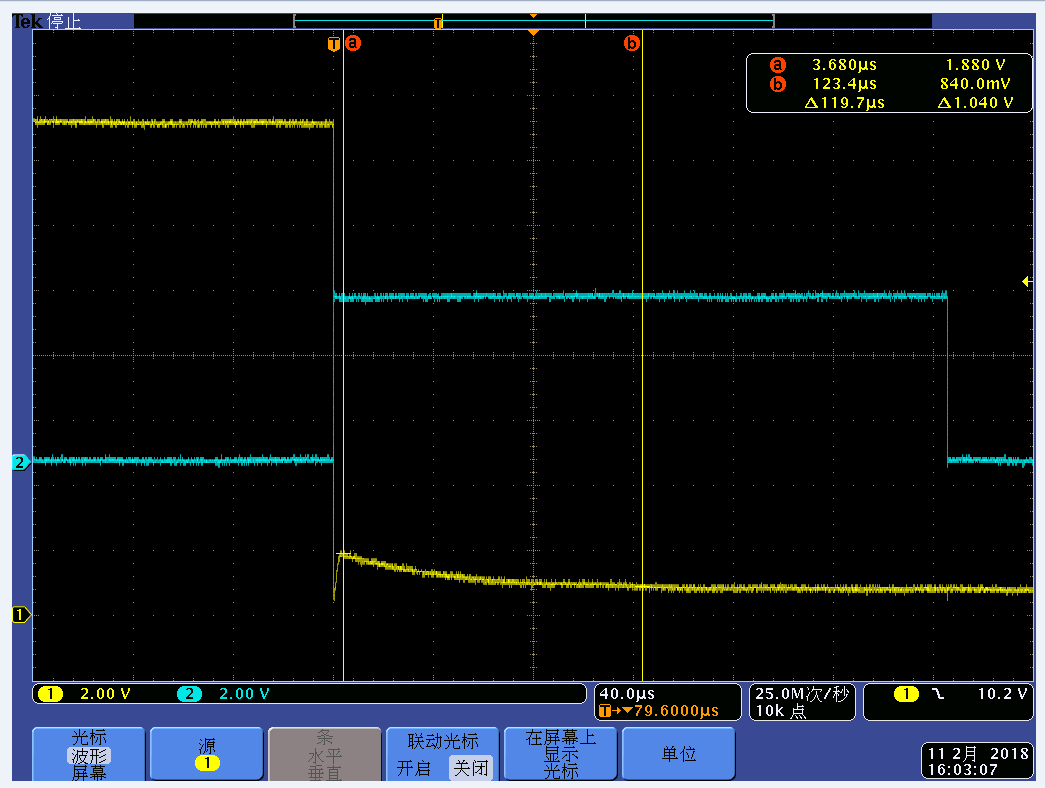

when the S3 is switched to S4 (A0 from 0 to 1), there will be ~120us delay in which the output (S8) will drop to 0.6V first, and then rise to 1V, and go back to target 0.76V finally. You can refer to the waveform attached (CH1: OUTPUT S8, CH2:A0).

When the input S3 voltage is lower, the delay can be shorter.

I can't find the break-before-make delay data when input is close to VDD.

Customer can't accept so long delay.

Could you let me know the reason and what actions can do to improve it?