Other Parts Discussed in Thread: SN74CBT3306

Switch Gurus:

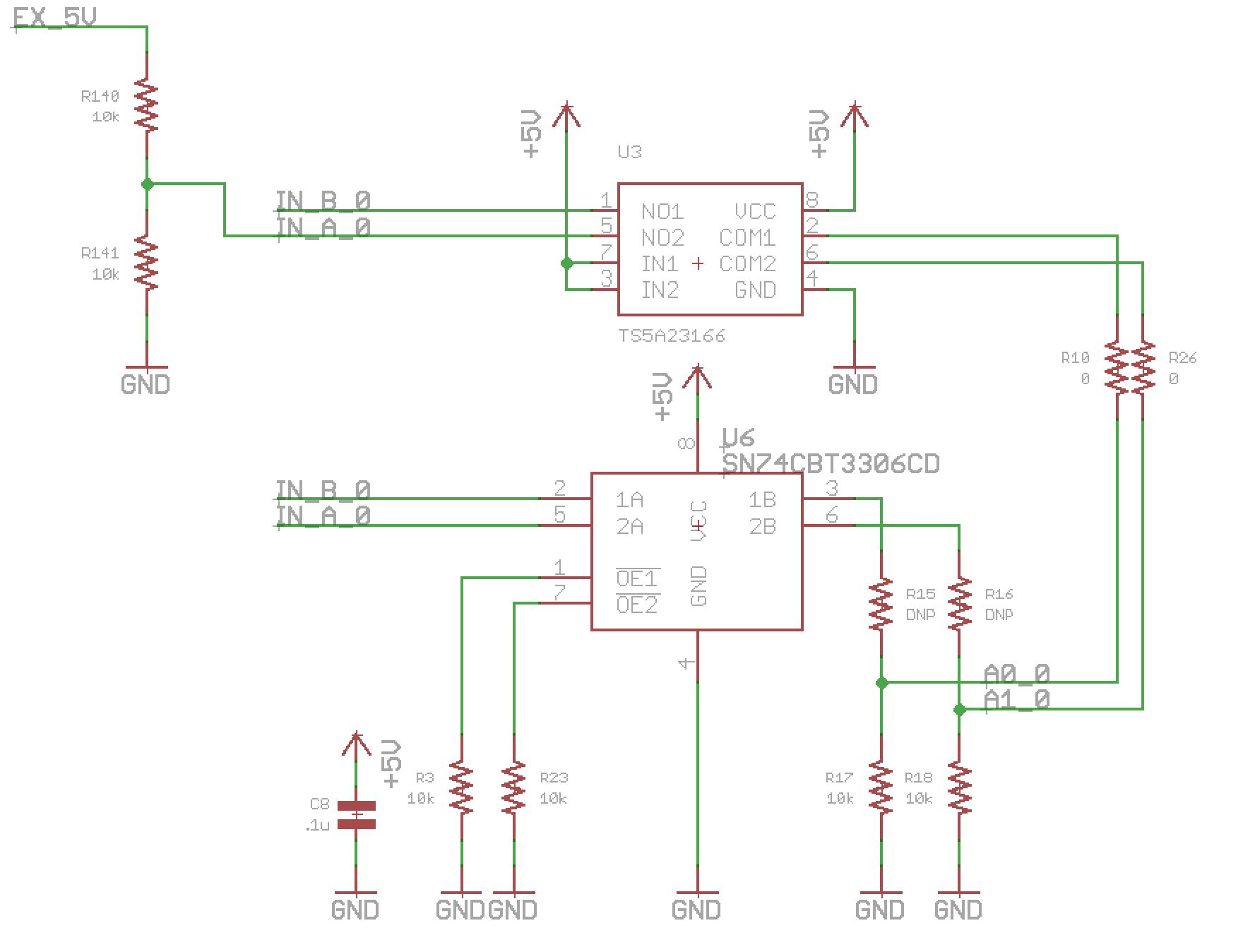

I designed in this device at the recommendation of Dakotah:

https://e2e.ti.com/support/switches_multiplexers/f/388/t/618079

However my client is seeing signals at the NO terminals sink current when the device is unpowered. I was told this device had IOFF protection. Is this not the case?

Best,

Trey