Hi,

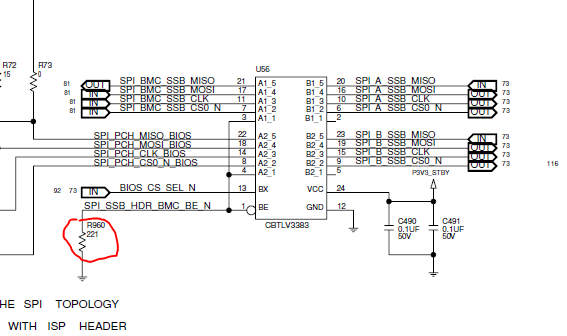

See the schematic excerpt below for reference.

Data corruption is occurring on the A1-B2 path when A1 is connected to B2 and A2 is connected to B1.

- Simple burst reads will yield bad bits, but on re-read correct can be recovered

- Issue manifests as fail to boot (cannot read BIOS) or fail to update (cannot correctly program BIOS)

- Device is being used to access flash

- There does not appear to be any temperature dependency (issue occurred at 25C).

- PCH and BMC are both masters and are both on "A" side

- BMC access is at 20MHz nominal and sometimes up to 25MHz

- PCH access is at 30MHz nominal and sometimes up to 40MHz

- Vil/Vih issues does not seem to be a possible reason for failure.

- two vendors of SPI flash is used, both are expected to have same Vih / Vil

Two experiments tested thus far:

- When stopping data transmission on the A2-B1 path, the problem goes away. This reliable stops the failure

- They will switch back to 221 ohm to see if the issue returns

- Note: There was a reported case where the "issue fixed itself" after they simply tried probing the lines