hai,

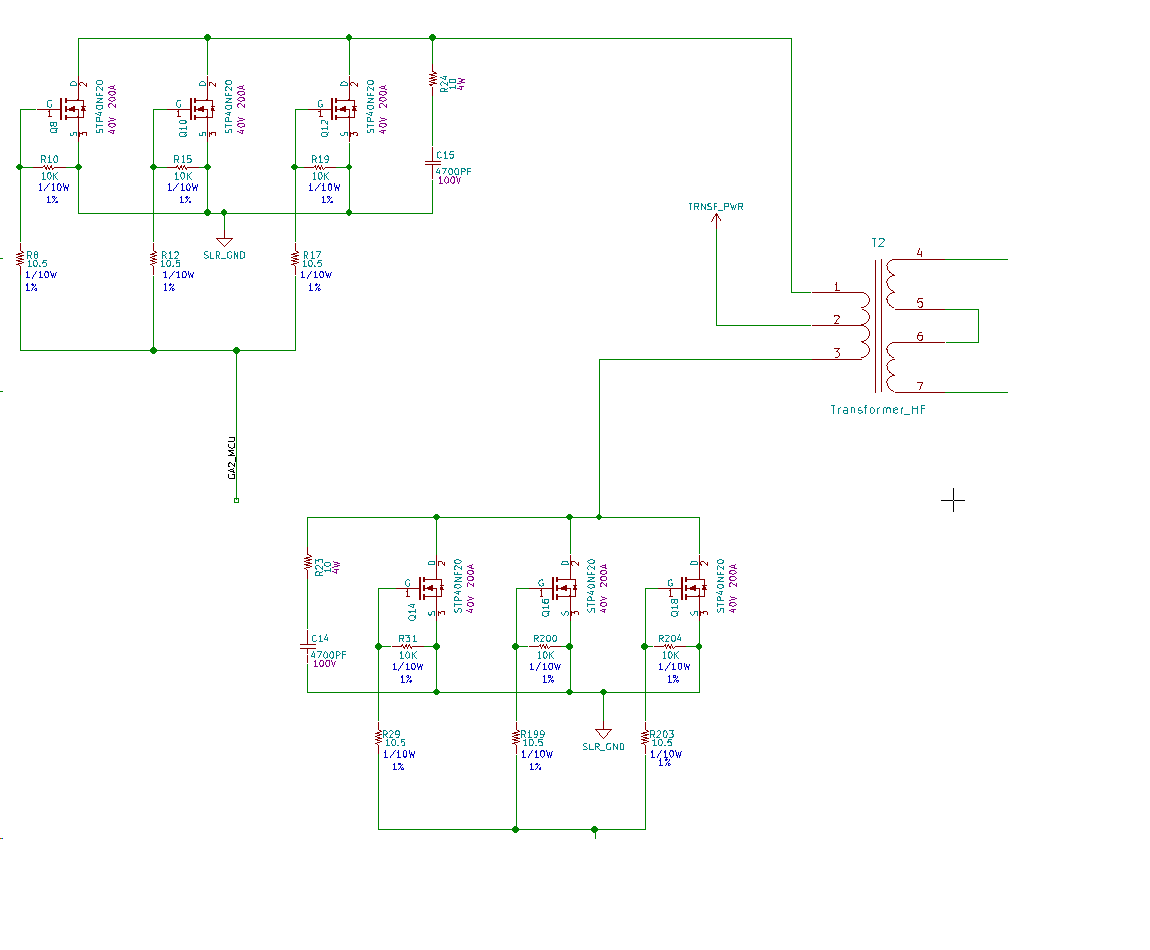

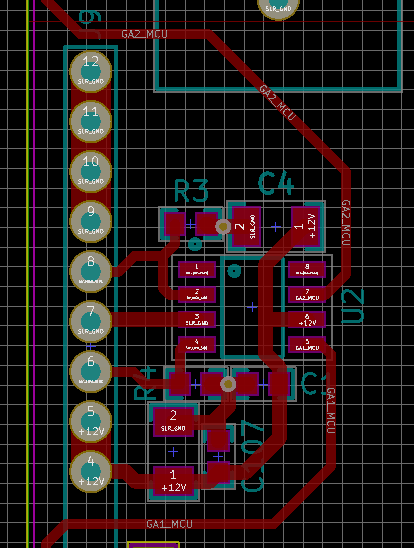

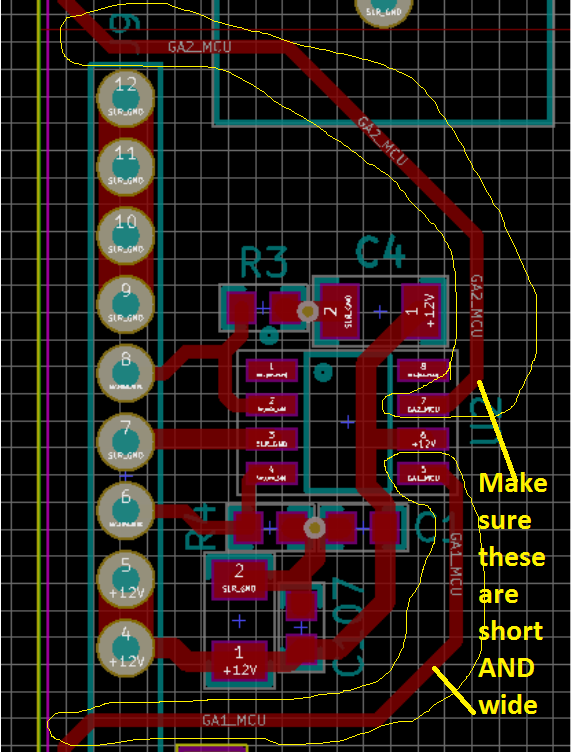

i am presently designing an inverter using pushpull topology.I am using IXX4427NTR as my gate driver.i have mosfets attached on two coils of my push pull transformer driving my configuration.I am giving square pulses at the input of the gate driver but happen to see that the waveform is distorted.What could be the reason for the shape change of the input waveform.I have routed the board in such a way that , the trace connects all mosfets on a single line but the shape of the gate signals varies from nearest mosfet to the mosfet at the far end why is that so?