I want to use the RSSI value to identify the distance of RF signal from, i try to set the MAX_DVGA_GAIN and MAX_LNA_GAIN value, only MAX_LNA_GAIN can affect the RSSI value, but the MAX_DVGA_GAIN seems nothing to do with the RSSI value, is it normal? if it's not, what do I miss?

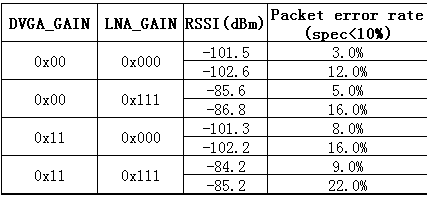

i use the SmartRF Studio doing the test, and the test result as below: