Recently added control on the TPS62730 to my project. With this I had expected some current reduction during advertising which would allow me to use +4dB for TX and atleast be on par with 0dB without the TPS62730. However my observation is as follows:

@ TX: 0dB, No TPS62730, TX = 29.2mA which is around what the datasheet specs (+2mA)

@ TX: +4dB, w/ TPS62730, TX = 32.8mA which is over +8mA greater than expected.

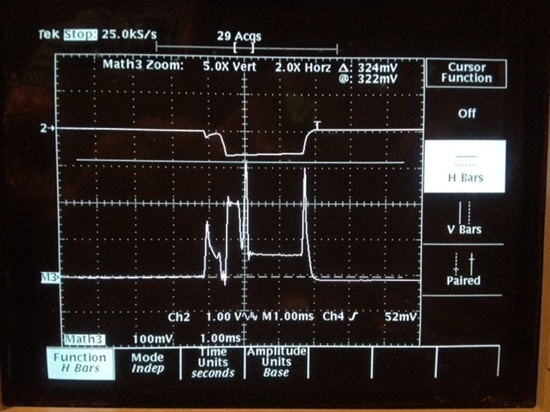

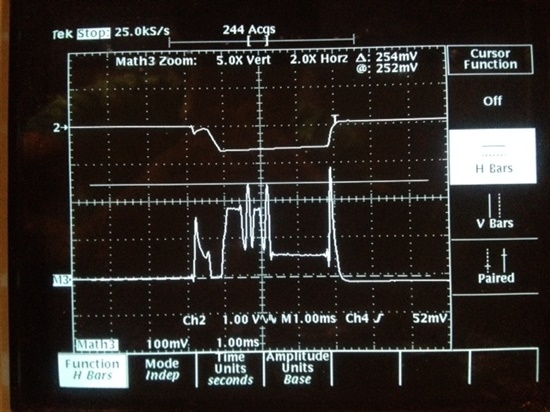

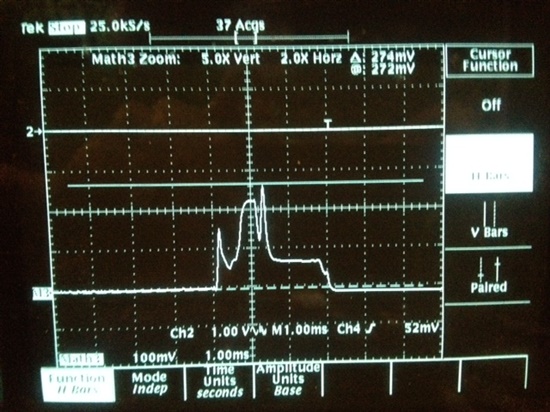

I have scoped the board to verify that the TPS62730 is enabled properly and brings the rail down to 2.1V within the expect Advertising window. Therefore I am concerned as to why I am not seeing any of the expected current savings. The consequence of this unexpected high current is that the hardware will POR reset much sooner as the battery depletes and IR increases, vastly reducing expected lifetime on the battery. Is there anything else besides

HCI_EXT_MapPmIoPortCmd( HCI_EXT_PM_IO_PORT_P1, HCI_EXT_PM_IO_PORT_PIN2 );

that must be set to observe the expected current savings? Anyone else run a similar issue? Thanks guys.