Hi,

I have a problem with Write Single Block (both sending and not sending UID)

The command works fine and I am able to write a block but I do not receive expected IRQ so I am not able to understand if the write is correct.

I am using Plus tags of any sizes

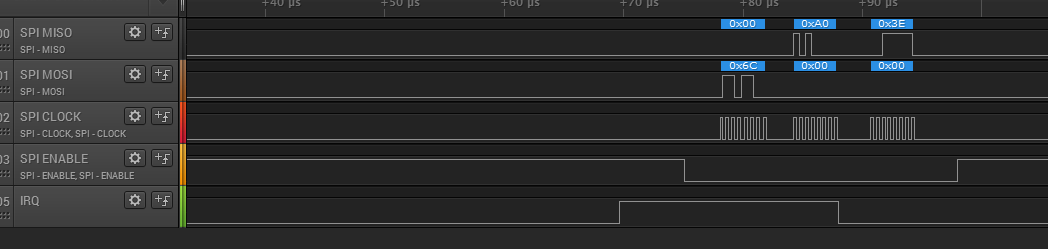

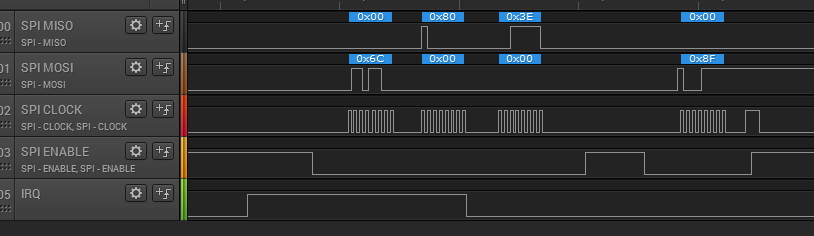

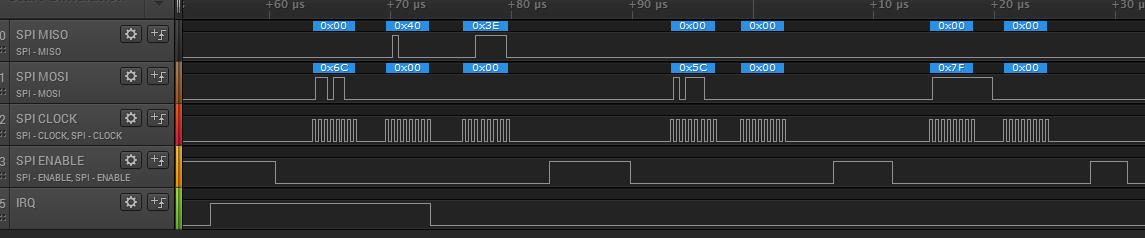

This is the sequence:

- Send command (option flag active)

- 0xA0 irq received (do nothing and wait next irq)

- 0x80 irq received. Wait 70ms and "TransmitNextSlot" (waiting less than 70ms results in a collision). I get the same result if I do not "TransmitNextSlot"

- No other irq are received (I expect a 0x40 irq)... .but data is written correctly.

The code to send the command is:

uint8_t buffer[12+UID_LEN];

uint16_t data_size = 7;

uint8_t flags = TRF_FLAG_OPTION;

if (uid)

{

data_size += UID_LEN;

flags |= TRF_FLAG_ADDRESS;

}

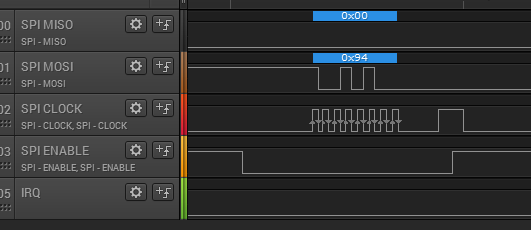

buffer[i++] = 0x8f; // Reset FIFO

buffer[i++] = 0x91; // Send with CRC

buffer[i++] = 0x3d; // Continuous write starting from 1D (transmission length)

buffer[i++] = (uint8_t)(data_size >> 8); // Data size (high byte)

buffer[i++] = (uint8_t)(data_size << 4); // Data size (low byte)

buffer[i++] = flags; // Flags

buffer[i++] = command; // Command

if (uid)

{

for (uint8_t j=0; j<UID_LEN; j++) // Copy UID (inverted)

{

buffer[i++] = uid[UID_LEN-1-j];

}

}

buffer[i++] = block_address; // Address

buffer[i++] = command_buffer[dataIndex+0]; // Data

buffer[i++] = command_buffer[dataIndex+1];

buffer[i++] = command_buffer[dataIndex+2];

buffer[i++] = command_buffer[dataIndex+3];

SPI_WriteBuffer(buffer, 0, i);

Any ideas? Thank you.

Best Regards

Alessandro