Other Parts Discussed in Thread: MSP-FET, TRF7960

Hello,

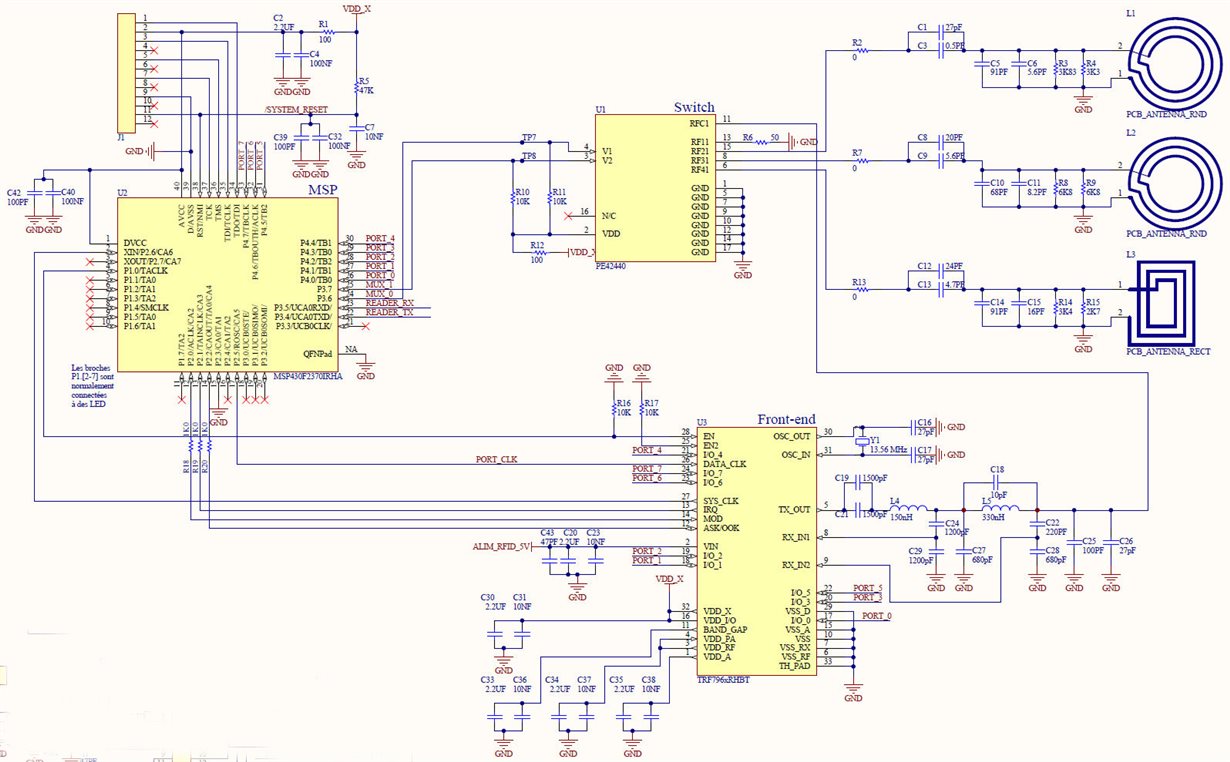

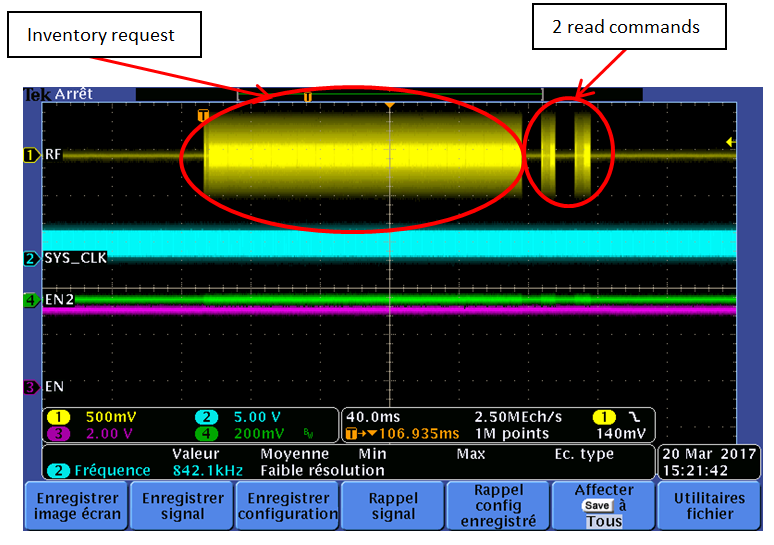

We implemented an RFID reader with a TRF7960A to read and write ISO15693 tags.

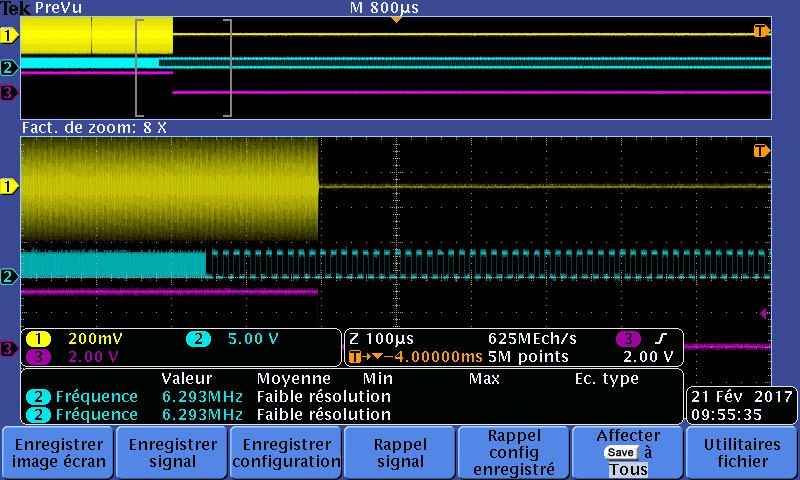

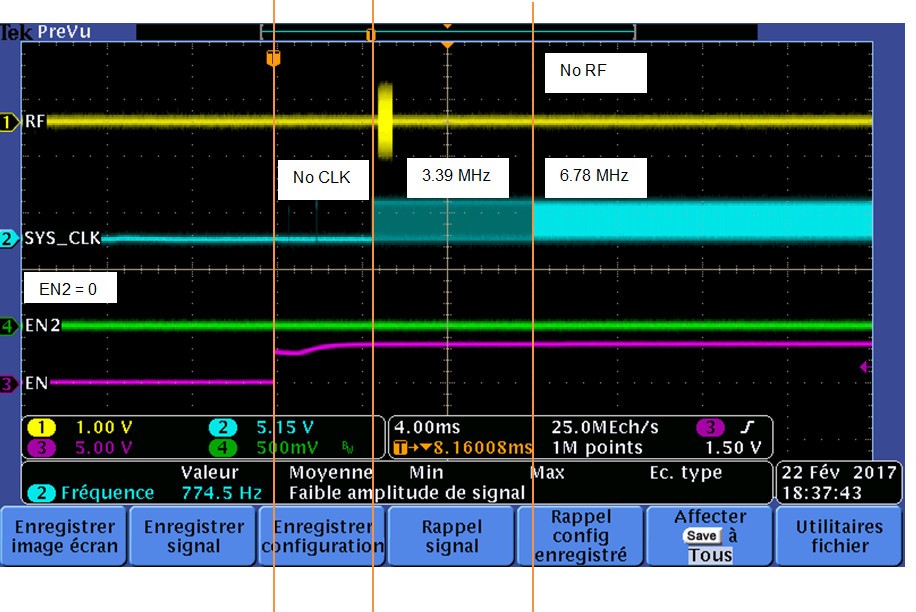

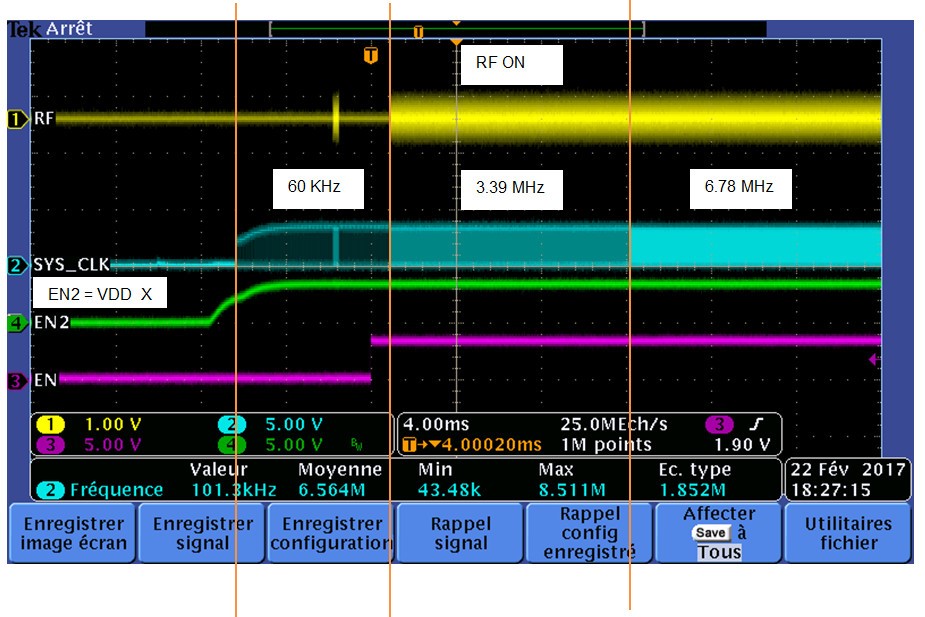

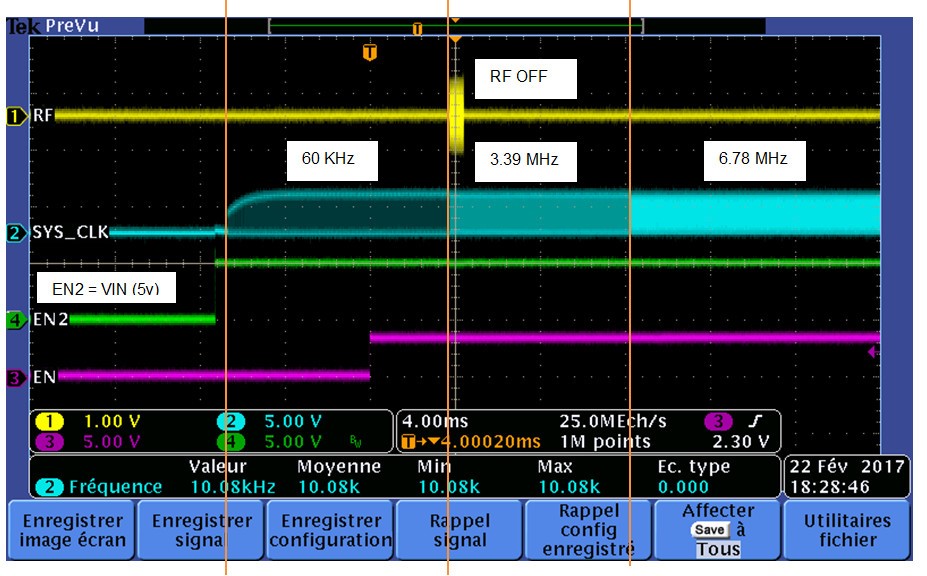

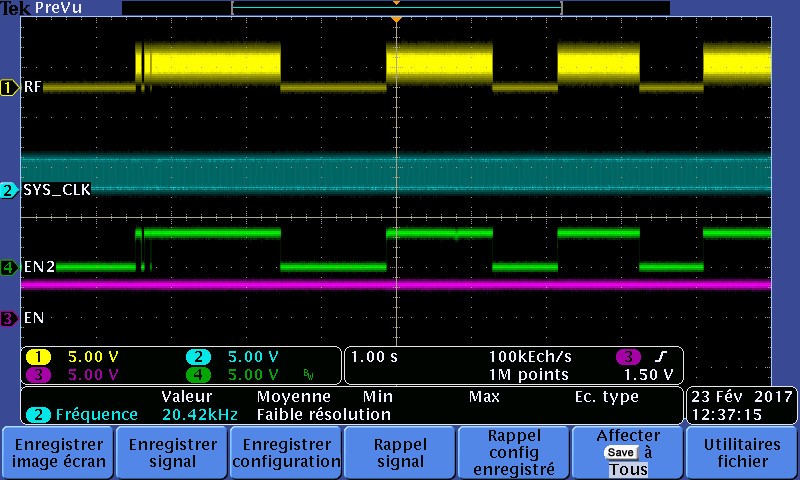

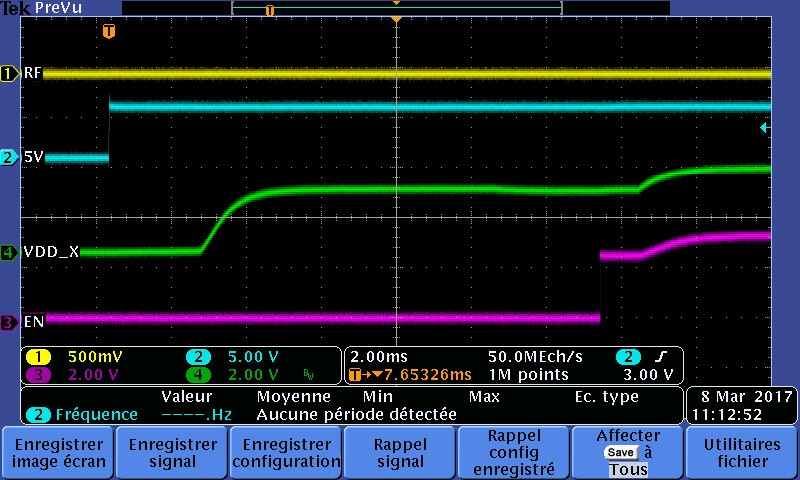

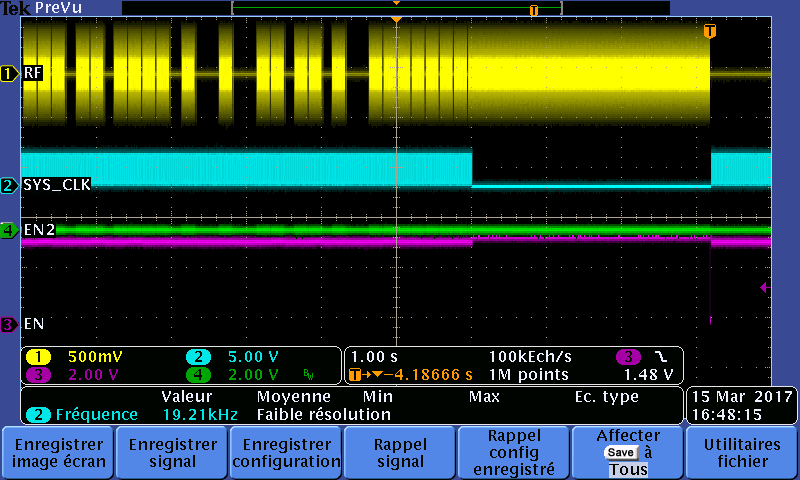

Sometimes, the reader doesn't reply to the MCU (MSP430) during Inventory request. After investigations, we found that SYS_CLK from the front-end has switched from 6.78 MHz to 60 KHz.

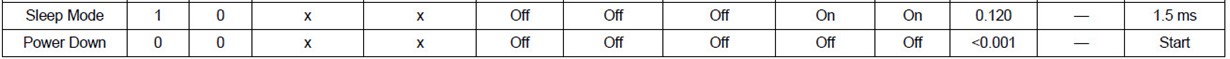

This state is documented in the datasheet as a "sleep mode", given by EN = 0 and EN2 = 1:

But, in our design, the EN2 pin is connected to VIN and EN is set to 1 by the MCU during the boot.

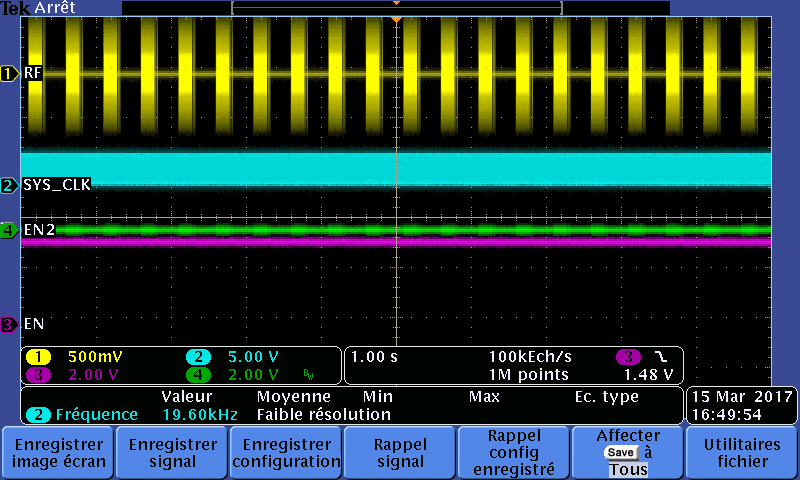

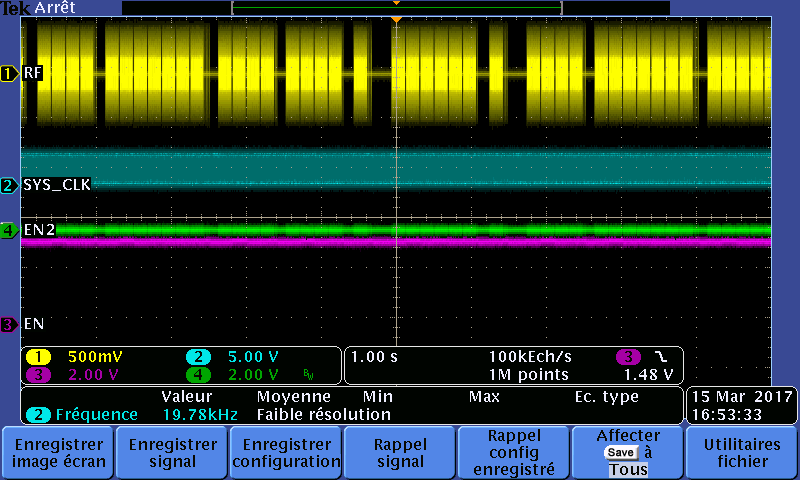

Here is a screenshot to describe what happen : Yellow = Antenna signal. Blue = SYS_CLK. Pink = EN.

You can see that SYS_CLK is 60 KHz before EN = 0. (EN go to 0 after, because we initialize an interruption to reboot the MCU when the clk is missing)

Is it possible to go to this state for another reason, like oscillator unstable for instance?

Is someone meet this kind of issue ? Is it a known problem by TI?

Thanks for your attention.

Pat.