Other Parts Discussed in Thread: TRF7970A

Hello,

I´m working with the TRF7960A with the MCU STM32F101RB, and my program follows this steps.

1- Enable the TRF EN=0 -> EN=1

2- Delay 10ms

3- Send to TRF de command 0x03 with the format 0x83. (I do this because I want all register be in default mode)

4-Delay 5ms

5-Send to TRF the single slot inventory 0x8F 0x91 0x3D 0x00 0x30 0x26 0x01 0x00, as the datasheet explains

6-Write in register 0x00, 0x20

7-Write ISO control

7.1- Write in register 0x01, 0x02

7.2- Write in register 0x0D, 0x3E

7.3- Write in register 0x09, 0x31

7.4- Write in register 0x06, 0x80

7.5- Write in register 0x07, 0x14

7.6- Write in register 0x08, 0x1F

7.7-

7.7.1- Read register 0x0A, 0xYY

7.7.2- 0xYY &= 0x0F

7.7.3-0xYY |= 0x40

7.7.4- Writte register 0x0A, 0xYY

7.8-

7.8.1- Read register 0x10, 0xYY

7.8.2-0xYY |= 0xEF

7.7.3- Writte register 0x10, 0xYY

7.9- Write in register 0x14, 0x0C

8- Send to TRF the single slot inventory 0x8F 0x91 0x3D 0x00 0x30 0x26 0x01 0x00, as the datasheet explains

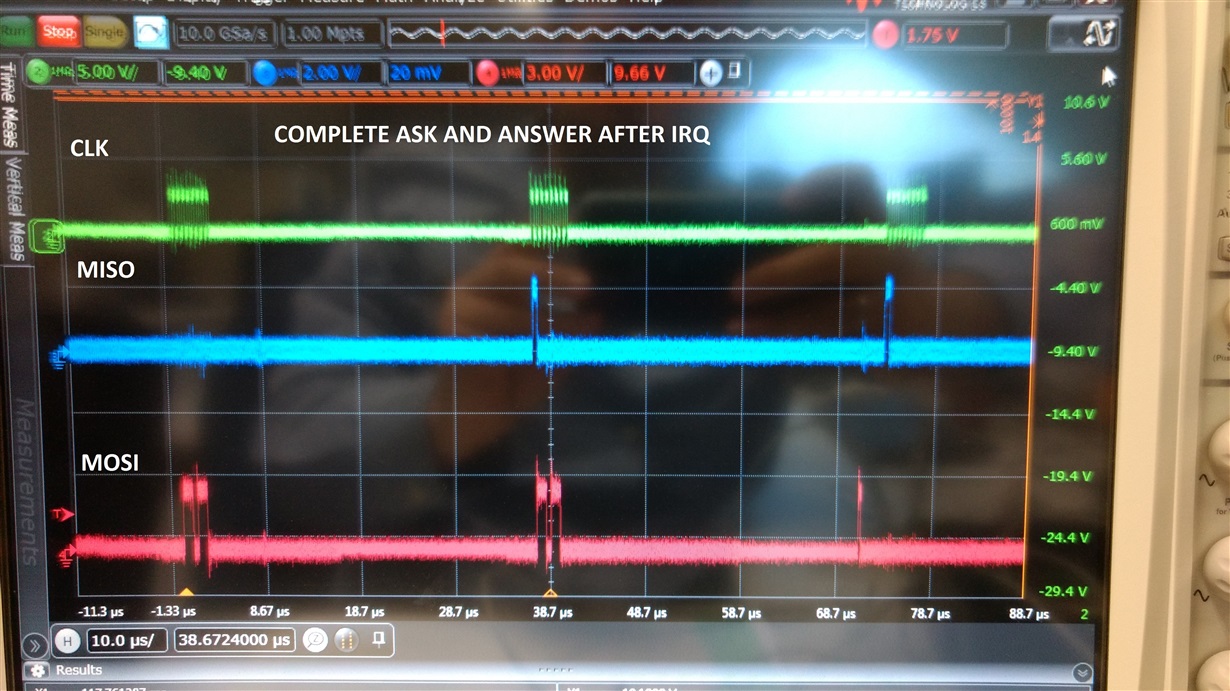

9- Wait an IRQ,

10- Receive an IRQ

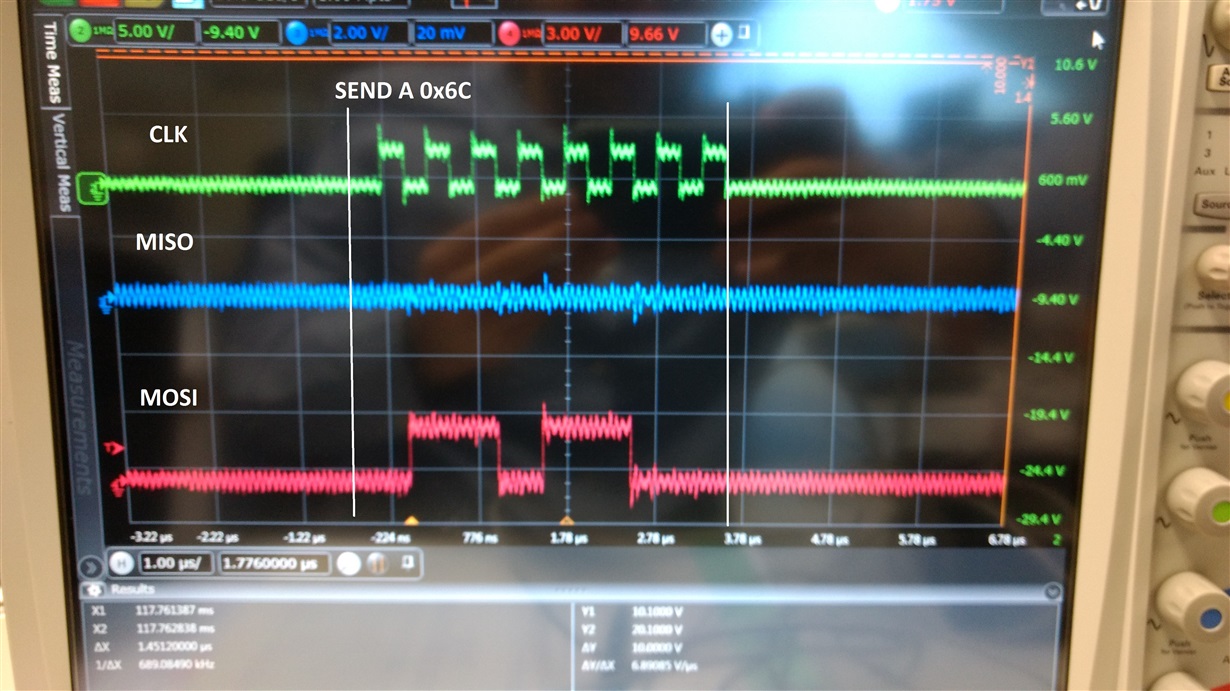

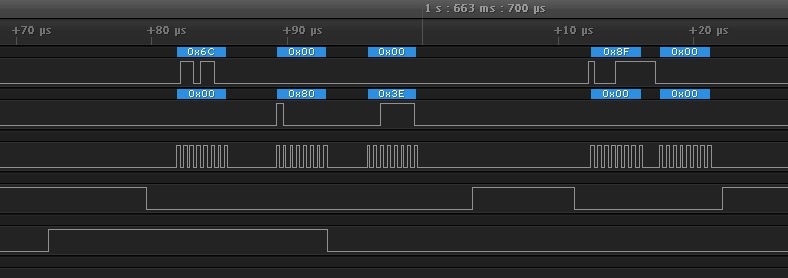

11- Ask with 0x6C and dummy clock

12-Recive a 0x80

13- Receive an IRQ

11- Ask with 0x5C

12-Recive a 0x23, here is the problem

I should receive a 0x60, and I don´t Know how manage this data and what is its meaning. Could yo help me?