Tool/software: Linux

Hey There,

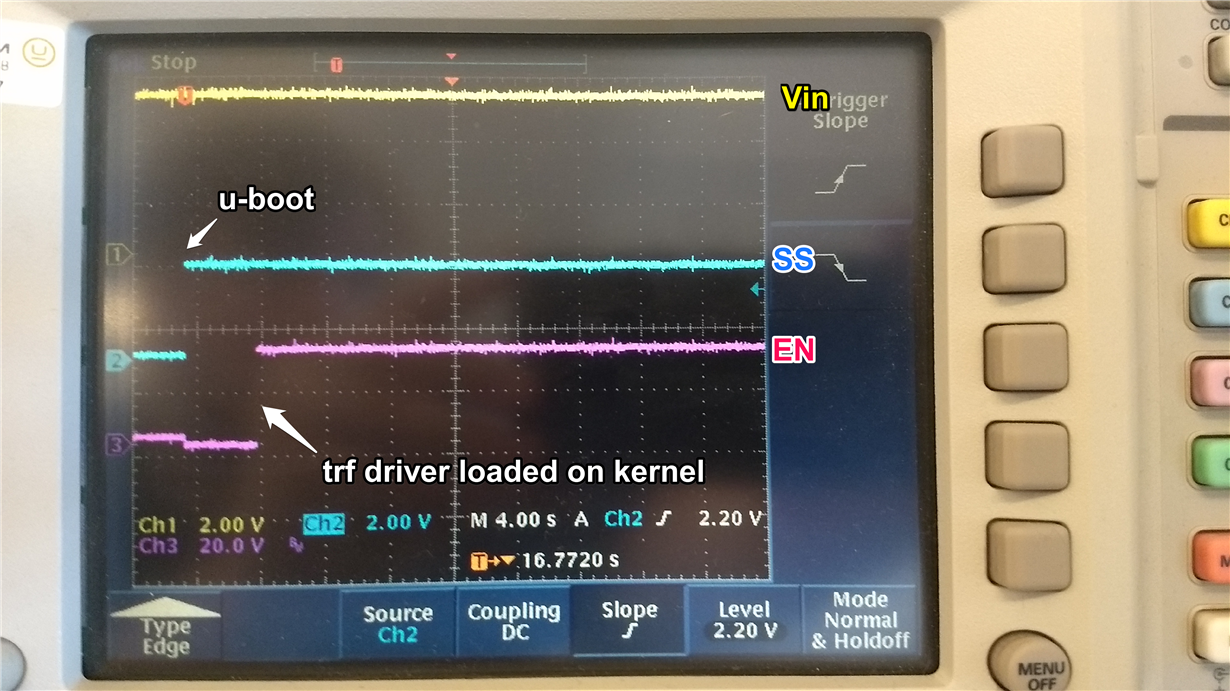

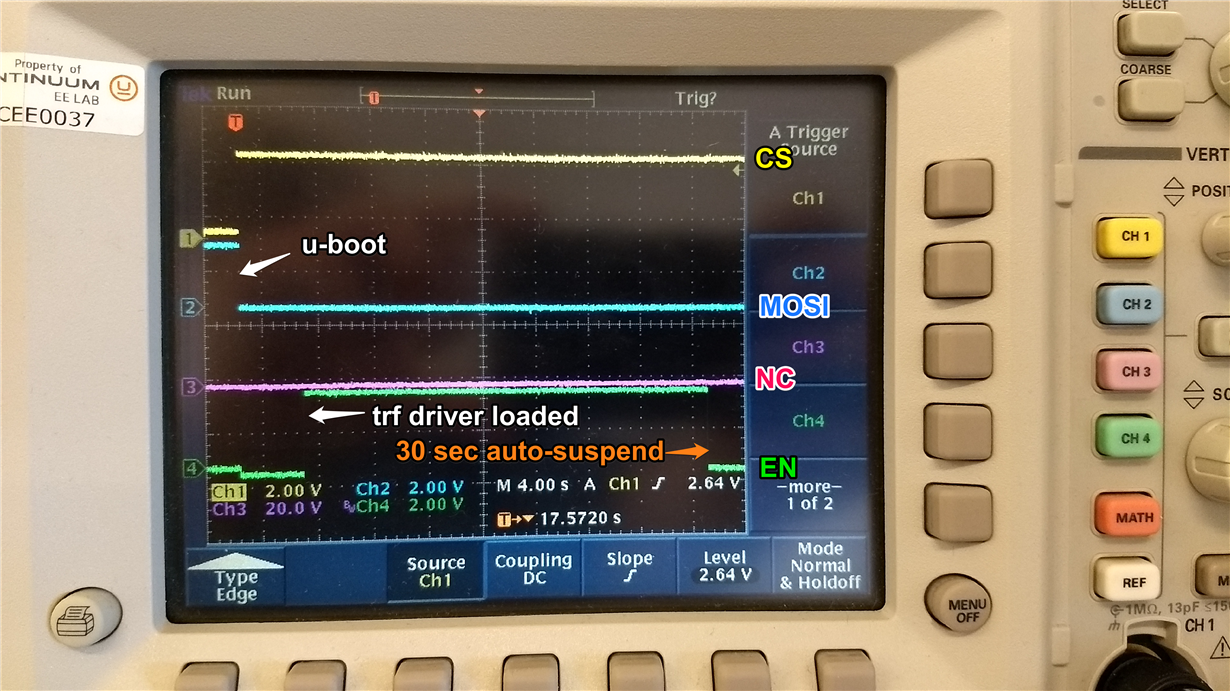

I'm working on developing an RFID driver for an embedded product. Right now I'm using the TRF7960TB EVM board with a TRF7970A chip installed. It is communicating via SPI with a MittySOM-5CSX SoC. There is one other SPI device on the same bus. The Vin line is a 5V signal from the power supply, EN is attached to a GPIO on the processor, and EN2 is tied directly to ground. The EN signal is getting set high when the drivers perform the power on function.

I have compiled the TI trf7970a drivers for my device as well as the neard stack which I'm using to interface with the low level drivers. I'm trying to get a "hello world" working with the chip as an Initiator. I've built the TI drivers with debug enabled and am using the neard example code to get running (the test-adapter python script inside the 'test' folder of the neard source).

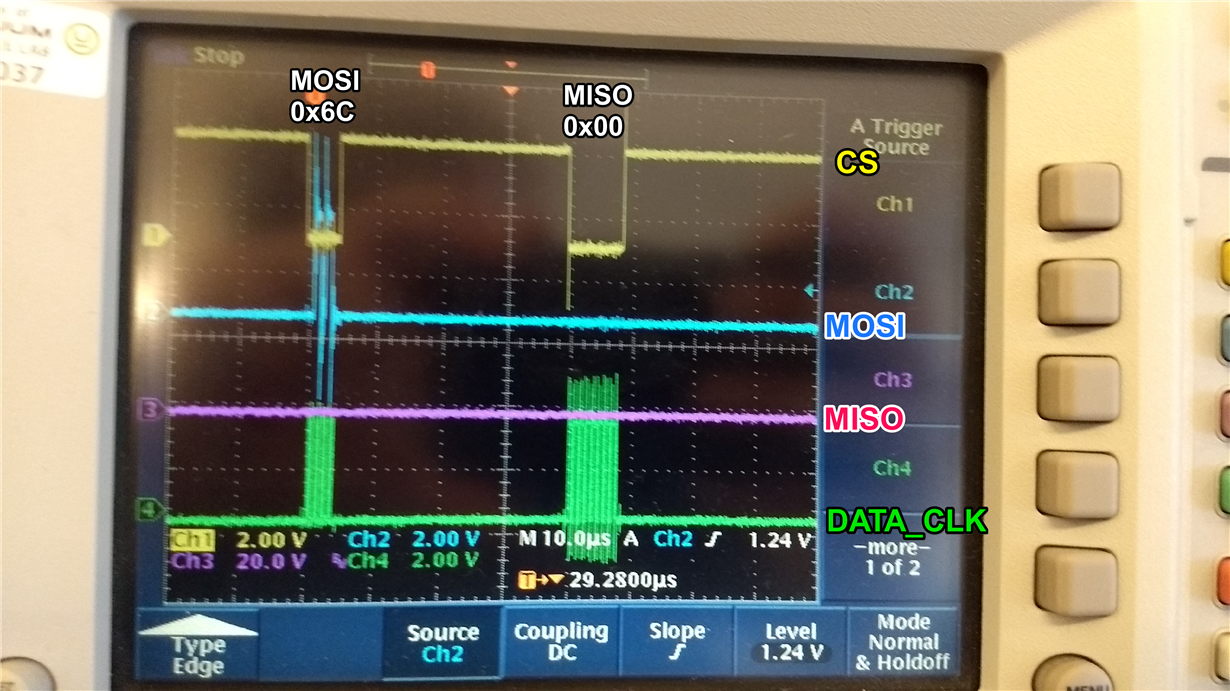

The device appears to be powering up fine, but when it goes through it's initial anti-collision process (command 0x19) the RSSI status register returns as 0xFF. This doesn't make much sense to me as B7 of the RSSI register is unused, and the default value for it is 0x40. Not only is it unlikely that those 3 LSB should be high, but why is the MSB also being set high? I've added the debug log below. Has anybody experienced this before? Any suggestion for which direction I should be heading next?

Best,

Ben

Relevant lines from /var/log/debug:

May 23 13:45:45 mitysom-5csx-h6-4ya_4 kernel: [ 4.226456] trf7970a spi32766.0: IRQ - state: 0, status: 0x0 May 23 13:45:45 mitysom-5csx-h6-4ya_4 kernel: [ 4.236283] trf7970a spi32766.0: Powering up - state: 0 May 23 13:47:15 mitysom-5csx-h6-4ya_4 kernel: [ 95.922212] trf7970a spi32766.0: Switching RF - state: 1, on: 1 May 23 13:47:15 mitysom-5csx-h6-4ya_4 kernel: [ 95.922233] trf7970a spi32766.0: Switching rf on May 23 13:47:15 mitysom-5csx-h6-4ya_4 kernel: [ 95.925726] trf7970a spi32766.0: Initializing device - state: 1 May 23 13:47:15 mitysom-5csx-h6-4ya_4 kernel: [ 95.925738] trf7970a spi32766.0: cmd: 0x83 May 23 13:47:15 mitysom-5csx-h6-4ya_4 kernel: [ 95.925844] trf7970a spi32766.0: cmd: 0x80 May 23 13:47:15 mitysom-5csx-h6-4ya_4 kernel: [ 95.927948] trf7970a spi32766.0: write(0x9): 0x0 May 23 13:47:16 mitysom-5csx-h6-4ya_4 kernel: [ 95.941173] trf7970a spi32766.0: write(0x14): 0xf May 23 13:47:16 mitysom-5csx-h6-4ya_4 kernel: [ 95.953323] trf7970a spi32766.0: write(0x10): 0x0 May 23 13:47:22 mitysom-5csx-h6-4ya_4 kernel: [ 101.986406] trf7970a spi32766.0: Configure hw - type: 0, param: 0 May 23 13:47:22 mitysom-5csx-h6-4ya_4 kernel: [ 101.991890] trf7970a spi32766.0: rf technology: 0 May 23 13:47:22 mitysom-5csx-h6-4ya_4 kernel: [ 101.991911] trf7970a spi32766.0: write(0x18): 0x0 May 23 13:47:22 mitysom-5csx-h6-4ya_4 kernel: [ 102.013012] trf7970a spi32766.0: Configure hw - type: 1, param: 0 May 23 13:47:22 mitysom-5csx-h6-4ya_4 kernel: [ 102.017635] trf7970a spi32766.0: framing: 0 May 23 13:47:22 mitysom-5csx-h6-4ya_4 kernel: [ 102.028861] trf7970a spi32766.0: write(0x0): 0x3 May 23 13:47:22 mitysom-5csx-h6-4ya_4 kernel: [ 102.045335] trf7970a spi32766.0: cmd: 0x99 May 23 13:47:22 mitysom-5csx-h6-4ya_4 kernel: [ 102.050421] trf7970a spi32766.0: read(0x4f): 0xff May 23 13:47:22 mitysom-5csx-h6-4ya_4 kernel: [ 102.055294] trf7970a spi32766.0: write(0x0): 0x1 May 23 13:47:22 mitysom-5csx-h6-4ya_4 kernel: [ 102.093169] trf7970a spi32766.0: Switching RF - state: 2, on: 0 May 23 13:47:22 mitysom-5csx-h6-4ya_4 kernel: [ 102.093184] trf7970a spi32766.0: Switching rf off May 23 13:47:22 mitysom-5csx-h6-4ya_4 kernel: [ 102.093197] trf7970a spi32766.0: write(0x0): 0x1