Hi, we have a case where a CC1350 is powered from a small battery. At low temperatures, the impedance of the battery may be quite high. To work with this, we have a capacitor in parallel to lower the impedance of the power supply, and then put CC1350 in Standby most of the time. We make sure to recharge the capacitors enough between bursts of activity such that in theory, the system should not go in brown-out.

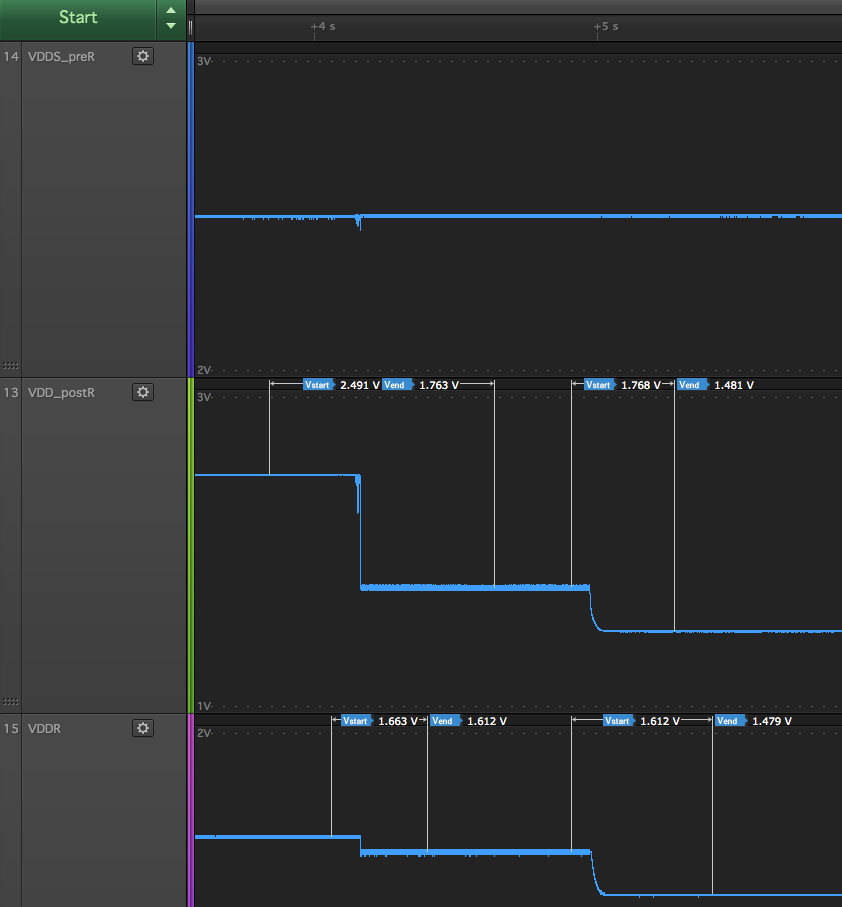

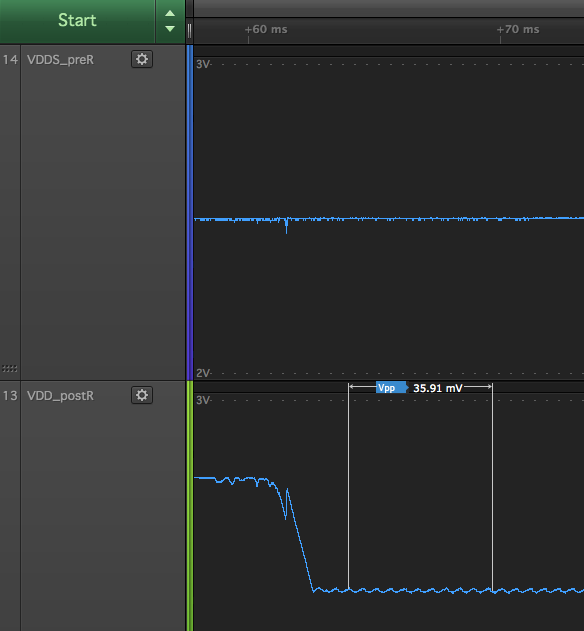

However, for various reasons like corner cases not handled properly by our firmware, the chip may try to use more charge than can be delivered from the capacitor and go into brownout. This would be OK if we could recover from it, however, the chip seems to get stuck in an infinite reset loop where it draws large amounts of current, quickly draining the battery beyond salvage. It seems that brownout triggers a reset that allows the voltage to rise a bit, but that the chip immediately after releases reset and tries booting, causing the power to drop again etc.

Is there a way to configure a reset delay? Such that when a brown-out occurs, reset is held for some time to allow the power system to recover? Or other suggestions for how to work around this problem?

Thanks, Pål Øyvind