Hi all,

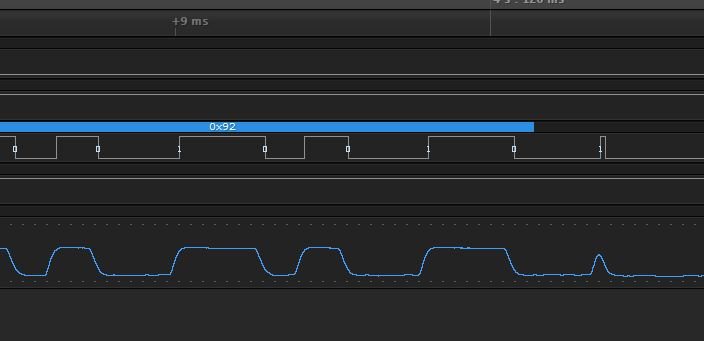

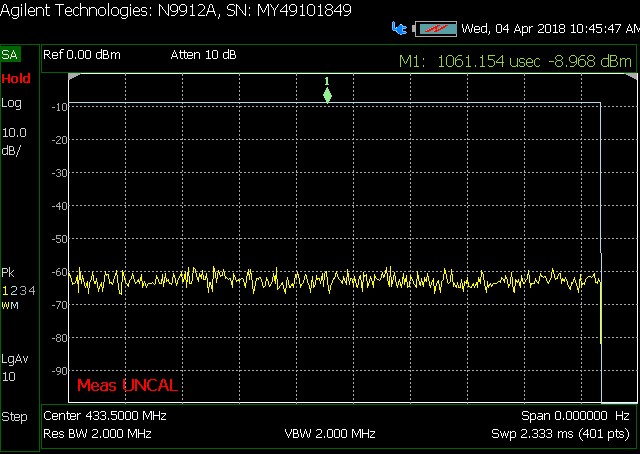

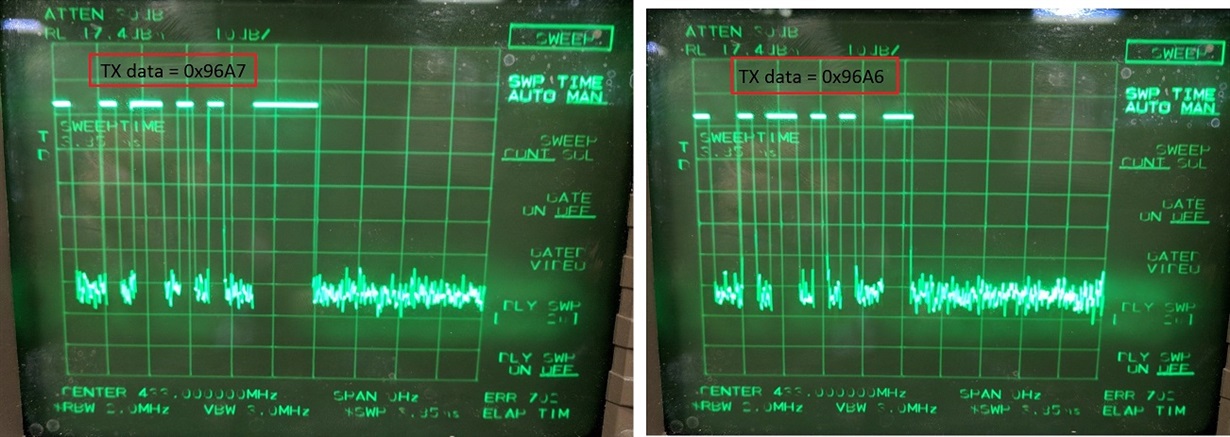

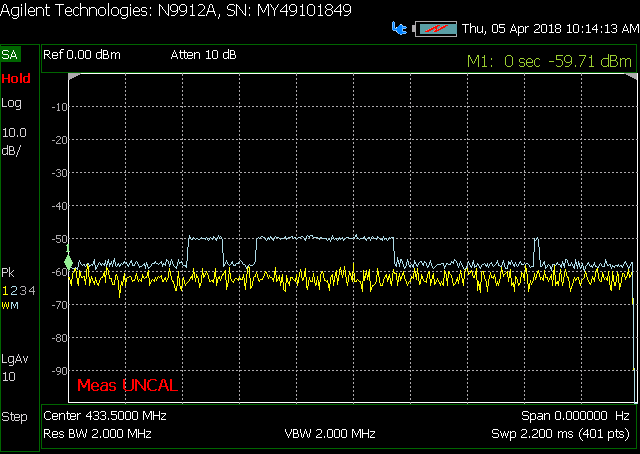

We have a product based on the CC1101 radio at 433 MHz that we are altering to use with a client installation. We are using an OOK setup. They have noted that, with their receiver, they have approximately 50% packet loss, and have been able to trace the source of their issue to packets ending with a 0 bit. Their demodulation shows what we are calling a 'burp' after the packet. I've attached an image showing this.

Is there a way we can eliminate this behavior from the CC1101?

Thank you,

Don