Hello,

We are using the Jorjin module WG7801-D0 based on the WL1801MOD WiLink8 chip from TI. It is hooked up with a Sitara AM3352BZCZ100 on MMC2. We are running linux kernel 3.14.19 and using wl18xx-build-utilities-R8.5. Buildroot is the build system.

We are seeing a kernel hang approximately 2.5% of the time on boot up whenever we bring up the WiFi interface as an access point using:

/usr/local/bin/hostapd -B /opt/configs/hostapd.conf -P /var/run/hostapd.pid

After investigation, the kernel hangs when it tries to grab a mutex when the udhcpc client is bringing the Ethernet interface up (ifconfig eth0 up). The mutex was previously locked by hostapd when trying to load the WiFi module’s firmware and was never released. The system was unable to load the firmware and got stuck endlessly waiting for a response from the module. Here is the call stack when the module fails to respond following the call to hostapd:

[…] (previous calls from the kernel omitted because deemed irrelevant)

drv_add_interface (net/mac80211/drivers_ops.h)

wl1271_op_add_interface (drivers/net/wireless/ti/wlcore/main.c)

wl12xx_init_fw (drivers/net/wireless/ti/wlcore/main.c)

wl18xx_boot (drivers/net/wireless/ti/wl18xx/main.c)

wl18xx_pre_upload (drivers/net/wireless/ti/wl18xx/main.c)

wlcore_read_reg (drivers/net/wireless/ti/core/io.h)

wlcore_raw_read32 (drivers/net/wireless/ti/core/io.h)

wlcore_raw_read (drivers/net/wireless/ti/core/io.h)

wl12xx_sdio_raw_read (drivers/net/wireless/ti/wlcore/sdio.c)

sdio_memcpy_fromio (drivers/mmc/core/sdio_io.c)

sdio_io_rw_ext_helper (drivers/mmc/core/sdio_io.c)

mmc_io_rw_extended (drivers/mmc/core/sdio_ops.c)

mmc_wait_for_req (drivers/mmc/core/core.c)

mmc_wait_for_req_done (drivers/mmc/core/core.c)

wait_for_completion (kernel/sched/completion.c)

[…] (further calls from the kernel omitted because deemed irrelevant)

The module hangs always at the same place, when trying to read the REG_CHIP_ID_B register (see wl1271_op_add_interface function). Further investigation using a logic analyzer showed that the module does not indeed respond. Here are relevant snapshots.

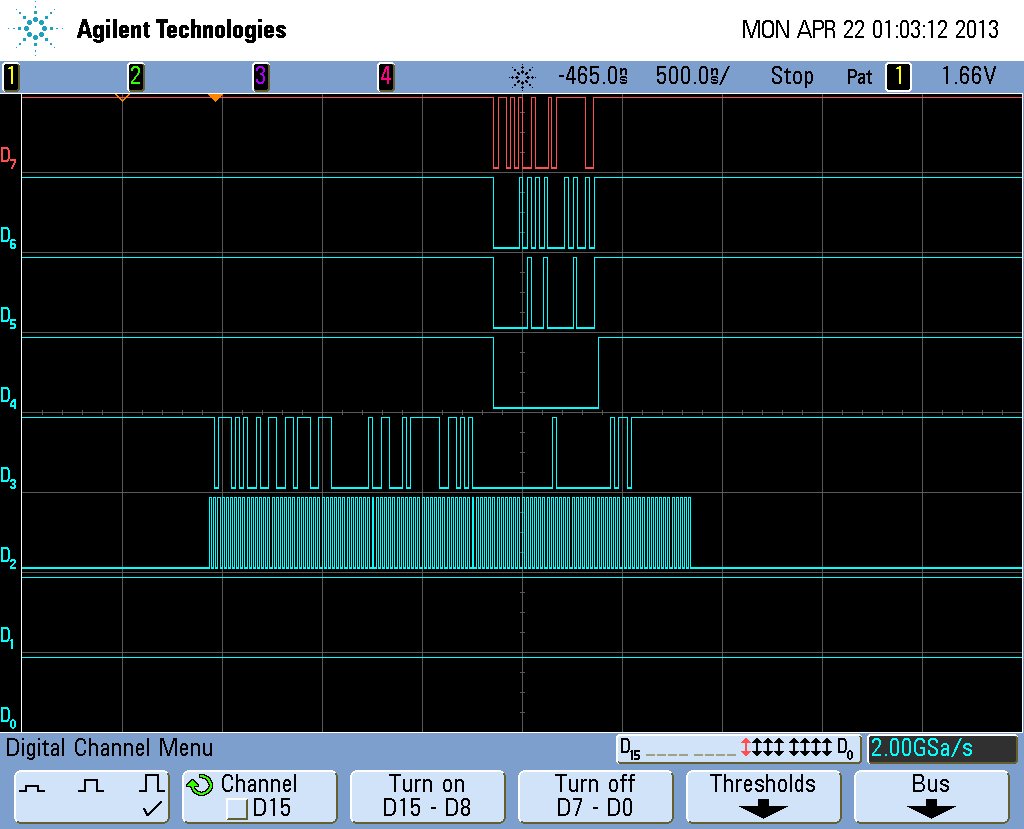

When everything is working as expected:

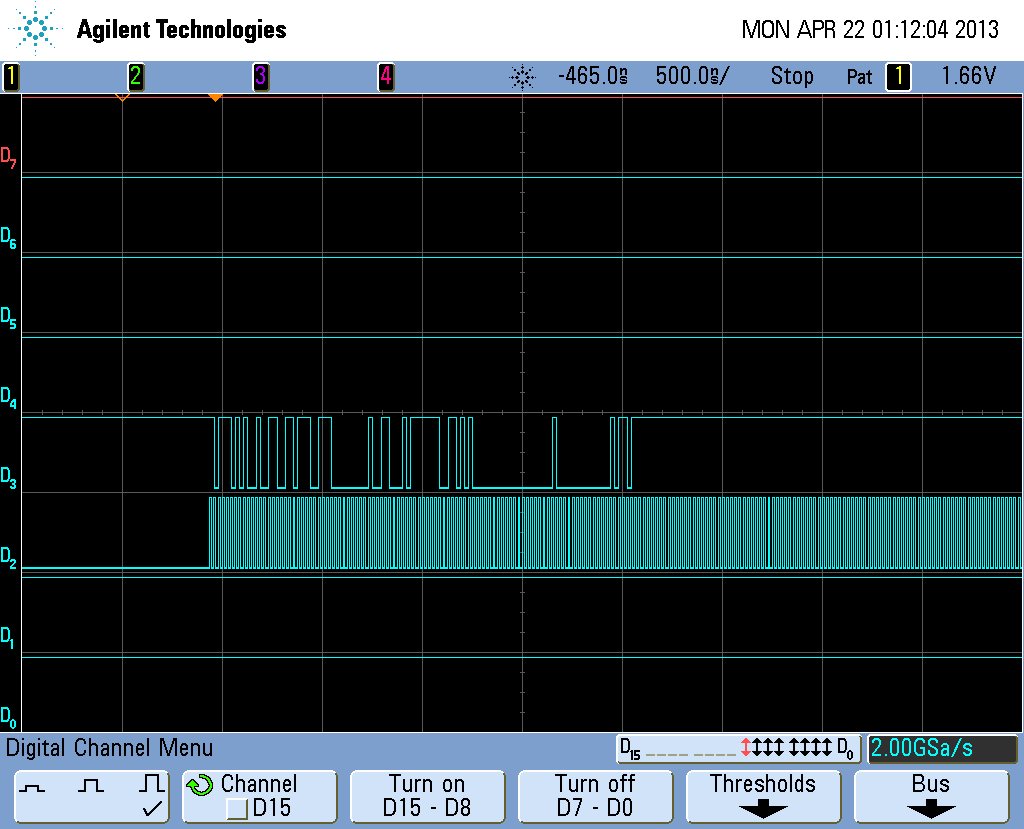

When the module fails to respond:

In both snapshots:

- D1 is the enable signal

- D2 is the clock

- D3 is CMD

- D4, D5, D6, D7 are the data lines

- (D0 is unused)

Please note that other SDIO transactions are going through just fine before this problematic one. Just to be clear, the system powers up, some transactions are done on the SDIO bus, the module responds fine and then this IO_RW_EXTENDED command is sent on the SDIO bus to read register REG_CHIP_ID_B. It is this command that never gets responded although previous ones were.

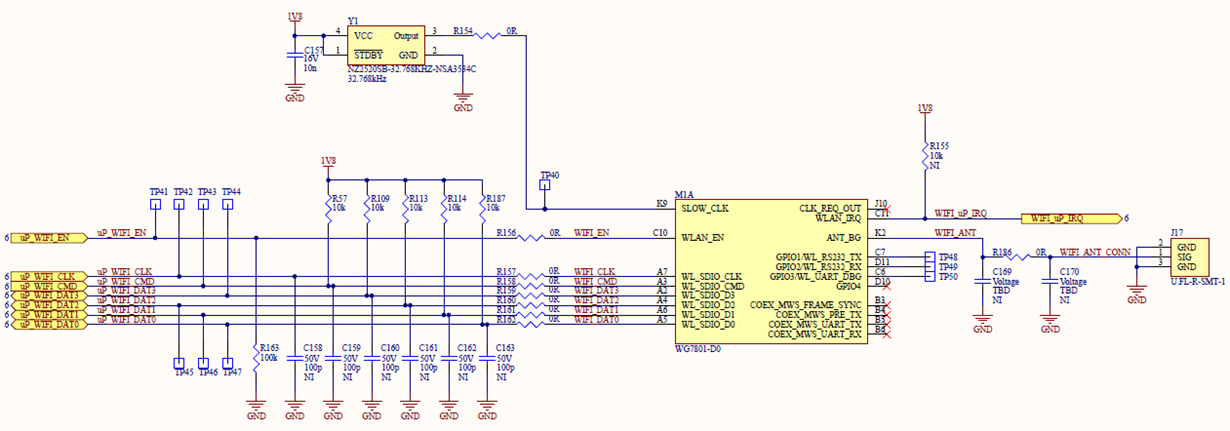

Here are the schematics for the WiFi module:

All signals going to/coming from page 6 are connected directly on the AM3352 without any passive or active parts.

HW-wise, I have probed the power rails of the module, looked at the setups and holds, applied heat or cold to change setups and holds, probed the enable signal for possible glitches, looked at the input clock, etc. without seeing anything suspicious.

We followed the WL18xx module integration checklist and the Jorjin datasheet. As far as I can tell, everything was implemented as suggested.

Any help would be greatly appreciated.

Guillaume Fournier

Brioconcept Consulting Inc.