Part Number: TPS7A20

Other Parts Discussed in Thread: TPS7A26

Tool/software:

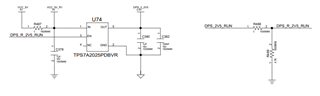

hello. In this project, the circuit was constructed using TPS7A20.

The current consumption of the load connected to the TPS7A20 does not exceed 10mA.

I am trying to turn the TPS7A20 output ON/OFF by controlling the VEN on the FPGA.

When VEN=0, Vout is output as an abnormal voltage instead of 0V(1.55V)

I would like to know why this phenomenon occurs and what solutions might be available.

Due to internal security policies, I cannot provide the complete circuit. Therefore, I am attaching a portion of the schematic that includes the TPS7A20.

The attached oscilloscope capture shows the state of the board when power is applied. (Green = VIN(5V), Blue = VOUT(1.55V), Yellow = VEN).

I suspect that the issue might be that, despite VEN being 0, the output is showing 1.55V, which seems to be the UVLO voltage being connected to the output. Please review this as well.

For additional information, when VEN is High, the output is 2.5V (normal operation).