毎日のように新しい技術が出現するなかで、より高速な高電圧信号の生成の必要性はますます高まっています。また、必要な条件もエンド機器によって頻繁に変化しています。これらのエンド機器は、任意波形ジェネレータ(AWG)や高電圧クロック・ジェネレータの速度の向上から、パワー電界効果トランジスタや半導体試験機器の入力の駆動まで、あらゆるものである可能性があります。

高電圧や高電流からの速度増加の要件によって、動作の温度制限を維持しながら高周波正弦波信号に歪みが発生しないようにするには、最終段の出力駆動アンプに非常に大きな圧力がかかります。低抵抗、または大容量の負荷駆動が必要な場合、出力アンプでは高電圧、高周波信号生成がさらに困難になります。高周波で高電圧スイングが必要なアンプは、最大リニア出力電流駆動が制限されることがあります。スルー・レート制限によって出力信号の歪みが増加し、アンプは高い周波数で必要な出力電流をソースまたはシンクできません。

この記事では、低抵抗または高容量の負荷を駆動する際の、高電圧、高周波正弦波信号の歪み性能の改善に注目します。

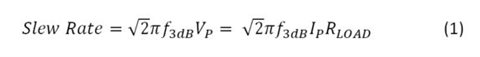

スルー・レート制限について理解するため、式1に示すように、ピーク出力電流(IP)の観点から、大信号帯域幅のスルー・レートの式を少しだけ変更しています。

ここで、f3dBは所定のピーク出力電圧(VP)に対するアンプの-3 dB帯域幅で、RLOADは、アンプの出力の総抵抗負荷です。

一定のスルー・レートを維持するには、IPは、RLOADが低い場合はIP を高くする必要があります。RLOADに応じて、このリニア出力電流の要件は極めて重要になります。これは、高周波動作を制限しながら、アンプの出力電流の駆動機能を自動的に厳しく制限します。容量負荷に対しては、周波数の増加に伴うインピーダンスの低下によって、リニア出力電流の低下の影響が非常に顕著になります。

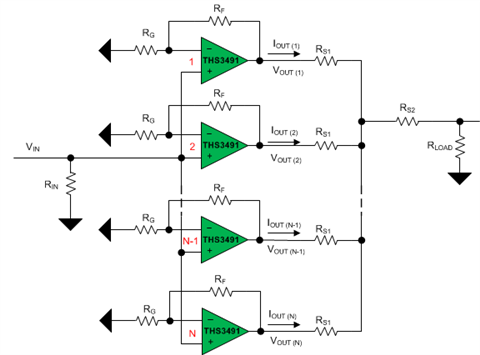

このような出力駆動の制約に効果的に対応するには、負荷分散を用いて駆動をブーストします。図1で示しているように、負荷分散の考え方として、共有されている出力負荷を複数のパラレル・アンプで駆動させます。それぞれのアンプが同じ入力ソース(VIN)によって駆動されます。共有されている出力負荷を複数のパラレル・アンプで駆動させると、各アンプ出力電力の要件は1/Nだけ低下します(Nは、パラレル・アンプの総数)。各パラレル・アンプの出力は同じ電圧です。これは、各パラレル・アンプが同じVINから駆動されているためです。

図1:負荷分散構成におけるN台のパラレル『THS 3491』アンプ

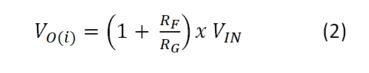

帰還(RF)、ゲイン(RG)、出力直列抵抗(RS1)が完全に一致していると仮定すると、式2は個々のアンプの出力VO(i)での入出力の伝達関数を示します。

ここで、iは、負荷分数構成の1~N個のアンプです。

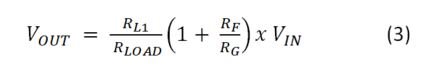

式3は、負荷抵抗(RL1)のVOUTにおける入出力間の伝達関数を表しています。

RL1は負荷分散構成におけるN台のアンプの合計出力負荷です。

式4は、負荷分散構成におけるN台のアンプに対する個々のアンプの出力電流駆動を計算しています。

1台の『THS 3491』アンプを使用して、20 VPPで20 ΩのRLOADを駆動する例を見てみましょう。このシナリオでの必要な出力電流駆動は±500 mAです。±7 V~±15 Vで動作する『THS 3491』は100 MHzで20 VPPの出力電圧振幅を実現し、100 ΩのRLOADを駆動しながら900 MHzの帯域幅を提供します。『THS 3491』は±500 mAの最大出力電流に対応できますが、その出力はスコープ上で歪んで(三角形に)見えます。これは、高周波での必要な出力電流のソースやシンクの機能がスルー・レートによって制限されるからです(このような周波数による出力電流の低下は、どのような高出力電流オペレーショナル・アンプ [オペアンプ] にも当てはまります)。2台の『THS 3491』アンプを負荷分散構成で使用すると、出力電流駆動は±250 mAで2台のアンプの間で均等に分割されます。その結果、周波数全体にわたり出力波形の歪みが少なくなります。

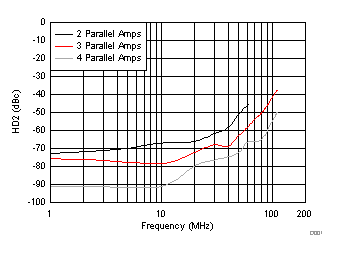

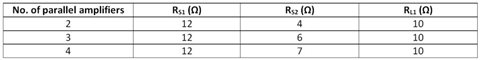

図2と図3は、第2高調波(HD2)および第3高調波(HD3)の測定結果を示したものです。それぞれ、2台、3台、4台の『THS 3491』パラレル・アンプのケースを比較しています(20 VPPで20 ΩのRLOADを駆動する場合)。表1は、それぞれの台数と、20 ΩのRLOADを生成するために使用された各直列抵抗とシャント抵抗の値が一覧になっています。歪みのプロットからわかるように、負荷分散構成における歪み性能の改善のメリットが明らかになっています。高調波歪みは、2台のパラレル・アンプによって60 MHzで-30 dBcを超えて劣化します。ただし、3台または4台のパラレル・アンプでは、出力電流駆動の強度は同じ20 VPPの出力スイングに対して100 MHzを超えています。

図2:HD2対パラレル『THS 3491』アンプの周波数。試験条件:VO = 20 VPP、RLOAD = 20 Ω

図3:HD3対パラレル『THS 3491』アンプの周波数。試験条件:VO = 20 VPP、RLOAD = 20 Ω

表1:『THS 3491』パラレル・アンプ構成でRLOAD = 20 Ωを生成するための出力抵抗値

この負荷分散のアプローチから、2つのことを推測できます。

・それぞれの追加したアンプは、同じ電圧スイングに対して少ない電流を出力する必要があり、f3dBの点を超える動作の周波数が拡張されます

・パラレル・アンプの数を増��すと、同じ��力スイングと動作周波数に対してより大きな出力負荷を回路で駆動できるようになります。これは、パラレル・アンプによって出力電流ブーストが増幅されるためです。

1つの注意点として、負荷分散構成を使用すると安定性が低下するというデメリットがあります。これは、プリント基板(PCB)の入出力信号が長くなることによって容量負荷が増加するためです。システムの電力消費の増加による出力プッシュ/プル電流の不一致も、このアプローチの副作用です。最終的に、これらすべての要因によって追加できるパラレル・アンプの最大数が決まります。

参考情報

・データシート:「THS 3491 900MHz、500mA高出力電流帰還アンプ」

・リファレンス・デザイン:「大信号アプリケーション向けロード・シェアリング・コンセプト実装のリファレンス・デザイン」

・TIの高速オペアンプ製品の詳細

※すべての商標および登録商標はそれぞれの所有者に帰属します。

※上記の記事はこちらのBlog記事(2018年10月30日)より翻訳転載されました。

※ご質問はE2E Support Forumにお願い致します。