高分解能信号チェーン設計における基本的な課題の1つは、対象の信号をアナログ/デジタル・コンバータ(ADC)で分解できるように、システムのノイズ・フロアを十分に低く抑えることです。例えば、低ノイズの24ビット・デルタ-シグマADCであるTIの『ADS1261』を選択した場合、2.5SPSと128V/Vのゲインで、最小6nVRMSで入力信号を分解できます。

しかしシステム上で配慮が必要なのはADCのノイズだけではありません。アンプ、電圧リファレンス、クロック、電源などの構成要素すべてがノイズの原因となります。システムのノイズに与えるデバイスの累積的な影響は何でしょうか?さらに重要な点として、システムは対象の信号を分解できるようになるのでしょうか?

システムのノイズを十分に理解し、設計に活かせるよう、最近「信号の分解」シリーズという技術記事を書きました。このシリーズでは、代表的な信号チェーンの一般的なノイズ源を考察するとともに、ノイズを低減して高精度測定を維持する手法を解説しています。

高精度ADCを用いた設計にむけて、このシリーズで取り上げている最も重要な疑問と答えを10個見ていきましょう。

①ADCではどのような種類のノイズが予想されますか?

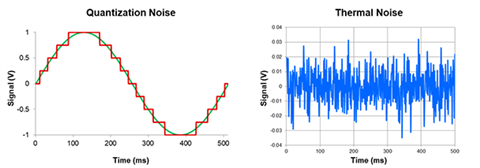

ADCの総ノイズには、量子化ノイズと熱ノイズという2つの主なノイズ源があります。量子化ノイズは、無諧調のアナログ電圧を有限な諧調のデジタル・コードにマッピングするプロセスから発生します(図1の左図)。そのため、1つのデジタル出力は、最下位ビット(LSB)の1/2だけ異なる複数のアナログ入力電圧に対応します。

熱ノイズはすべての電子部品に固有の現象であり、導電体内部の電荷の物理的な動きによって生じます(図1の右図)。ADCの熱ノイズは、ADC設計の結果であり、エンド・ユーザーがこの熱ノイズを左右することは、残念ながらできません。

熱ノイズと量子化ノイズは、低分解能ADCと高分解能ADCに対して同じように影響するのでしょうか?その答えは“信号の分解:デルタ-シグマADC内のノイズの概要(第1部)”をご覧ください。

②ADCのノイズをどのように測定、定義するのですか?

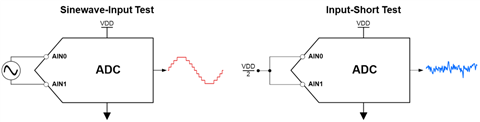

ADCメーカーがADCノイズの測定に使用する方法は2つあります。1つ目の方法では、ADCの入力同士を短絡させて、熱ノイズによる出力コードのわずかな変動を測定します。2つ目の方法では、決められた振幅と周波数(1kHzで1VPPなど)を用いて正弦波を入力し、ADCで正弦波をどのように量子化したかを示します。図2は、これらのノイズ測定方法を示したものです。

どのADCにどの種類の測定方法を用いるかは、Part 2のノイズ測定方法と仕様をご覧ください。

③システムのノイズ分析に最善のノイズ・パラメータは何ですか?

ADCノイズ分析では、入力換算ノイズを使用することを推奨します。ADC性能の定義に入力換算ノイズを使用することは一般的ではないため、この用語を太字で表しました。実際、エンジニアは、有効分解能やノイズフリー分解能などの相対パラメータの件について発言しており、これらの値を最大化できない場合を非常に気にかけています。16ビットの有効分解能を実現するために24ビットのADCを使う必要がある場合、活用しきれていないADC性能があるとも言えます。

しかし、16ビットの有効分解能で、ADCがFSR(フルスケール範囲)をどれくらい使用することになるかは必ずしもわかりません。16ビットの有効分解能しか必要ないかもしれませんが、最小入力信号が50nVの場合、16ビットのADCでは信号を分解できません。したがって、高分解能のデルタ-シグマADCの本当の利点は、このADCが提供する低レベルの入力換算ノイズです。有効分解能が重要でないのではなく、システムをパラメータ化するベストな方法ではないだけです。

Part 3では、システムのノイズ・パラメータを定義するためにノイズフリー分解能と入力換算ノイズの両方を使用する設計を例にして、この主張にさらに踏み込んでいます。どちらの方がより簡便で、最も適応可能なソリューションを実現できるでしょうか?その答えはPart3の記事をご覧ください。

④ENBWとは何ですか?なぜENBWが重要なのでしょうか?

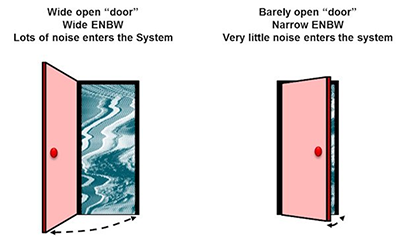

一般的な信号処理の用語として、フィルタの有効ノイズ帯域幅(ENBW)とは、ノイズ電力が元々のフィルタのノイズ電力(H(f))とほぼ同じである理想的なブリックウォール・フィルタのカットオフ周波数fCのことです。

日常に置き換えて考えてみます。家の中を暖かく保つためには、入ってくる冷たい空気の量を制限するために、ドアと窓をなるべく大きく開けないようにする必要があります。この場合、家がシステム、ドアと窓がフィルタ、冷たい空気がノイズ、ENBWはドアと窓をどれくらい開けているか(あるいは閉めているか)の測定値です。図3に示すように、開き方(ENBW)が大きいほどたくさんの冷気(ノイズ)が家(システム)の中に入ってきますし、開き方が狭いと冷気があまり入ってきません。

図3:ENBWが広いと侵入するノイズが多くなり(左)、ENBWが狭いと侵入するノイズが少ない(右)

図3:ENBWが広いと侵入するノイズが多くなり(左)、ENBWが狭いと侵入するノイズが少ない(右)

ENBWの要因となるシ��テム構成要素は何でしょうか?詳しくはPart 4をご覧ください。

⑤システムのノイズ帯域幅の算出方法は?

信号チェーンにフィルタ部品が複数ある場合、信号チェーンの中の下流にあるフィルタをすべて組み合わせて各部品のENBWを算出しなければなりません。フィルタを組み合わせるには、大きさ(デシベル単位)と周波数の対応をプロットし、ポイントごとに合計します。

例えば、図4のアンプのノイズ要因を計算するには、アンプの帯域幅をアンチエイリアス・フィルタ、ADCのデジタル・フィルタ、後処理フィルタと組み合わせる必要があります。この場合、電磁干渉(EMI)フィルタはアンプの上流にあるため、無視できます。

これは複雑になることがあるため、分析を簡素化するENBW近似法についてPart 5をご覧ください。

⑥ADCの入力に外部アンプを付け加えると、システムのノイズ特性にどう影響しますか?

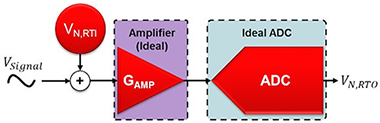

ADCとアンプを両方ともそれぞれのノイズ源から離すことで、ノイズ解析がより容易になります。この場合、図5に示すように、両方の入力換算ノイズに等しい電圧源が前段にある、ノイズのないアンプとノイズのないADCとしてシステムをモデル化できます。

図5:入力換算総ノイズが前段にある「ノイズなし」ADCおよびアンプ

図5:入力換算総ノイズが前段にある「ノイズなし」ADCおよびアンプ

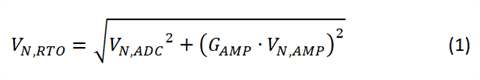

ほとんどのADCデータ・シートでは入力換算ノイズが仕様として使われるため、測定される出力ノイズを入力に換算しなければなりません。アンプとADCのノイズに相関がないと仮定すると、合計出力換算ノイズを求めるには、両方の値の二乗和平方根を取ります。また、アンプ・ノイズをアンプのゲインGAMPで逓倍する必要があります。式1は、その結果の出力換算ノイズを示すものです。

これを入力換算ノイズに変換するにはどうすればいいのでしょうか?また、ゲイン係数GAMPの効果は何でしょうか。その答えはPart 6をご覧ください。

これを入力換算ノイズに変換するにはどうすればいいのでしょうか?また、ゲイン係数GAMPの効果は何でしょうか。その答えはPart 6をご覧ください。

⑦ゲインが大きすぎるといったことはあるのでしょうか?

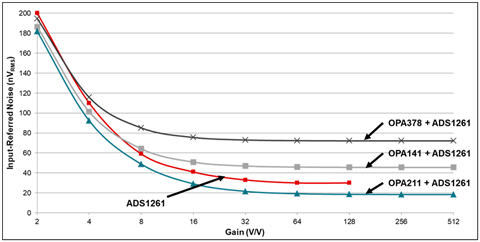

シリーズのPart 7では、複数の外部アンプを『ADS1261』の入力に付け加えた例を取り上げ、その結果のノイズ特性を測定しました。次に、この組み合わせと『ADS1261』のベースラインのノイズ特性を、その内蔵プログラマブル・ゲイン・アンプを使用して比較しました。簡単に比較できるようにするために、各組み合わせについて異なるゲイン設定でのノイズをプロットしました。これにより、高精度ADCに外部アンプを付け加えることで性能にどう影響するかと、ゲインにより性能がどう変化するかについて、いくつかの知見を得ました。図6はそのプロット図です。

図6:『ADS1261』を複数のアンプと組み合わせたときのノイズ特性をゲインの関数として比較

図6:『ADS1261』を複数のアンプと組み合わせたときのノイズ特性をゲインの関数として比較

この例と図6のプロット図からわかる重要なポイントは何でしょうか?詳しくは"Resolving the Signal Part 7: The Effects of Amplifier Noise on Delta-Sigma ADCs"をご覧ください。

⑧システムに侵入してくるリファレンス・ノイズの量を算出する方法は?

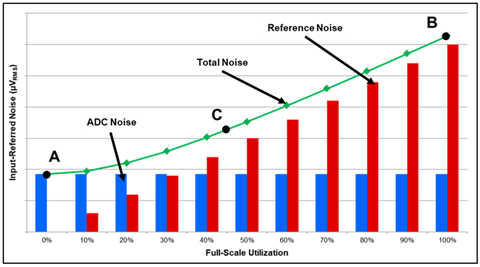

リファレンス・ノイズの最も面白い特性の1つが、使用するADCのFSRの大きさに対して直線的に変化することです。入力信号が非常に小さい場合は、リファレンス・ノイズはほとんど見られません。そのため、ノイズの多いリファレンスを使用できる可能性があります。また、入力信号がミッドスケールより大きい場合は、リファレンス・ノイズが支配的になると想定できます。この場合、必ずADCノイズとリファレンス・ノイズを比較できるようにしてください。図7は、FSR使用率の関数としてリファレンス・ノイズ、ADCノイズ、総ノイズを定性的にプロットしたものです。

図7:FSR使用率の関数としてのリファレンス・ノイズ、ADCノイズ、総ノイズ

図7:FSR使用率の関数としてのリファレンス・ノイズ、ADCノイズ、総ノイズ

この図でA、B、Cのキーポイントが表すものは何でしょうか?また、入力信号の変化とシステム・ゲインの変化はリファレンス・ノイズにどう影響するでしょうか?この問いの答えはPart 8をご覧ください。

⑨システムに侵入するリファレンス・ノイズの量を抑える方法は?

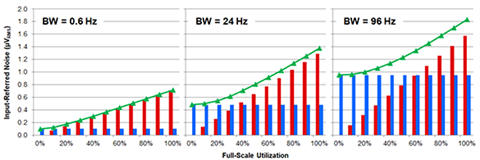

システムに侵入するリファレンス・ノイズの量を減らすための一般的な方法の1つは、システムの全体的なENBWを制限することです。そのためには、ADCの出力データ・レートを落とします。図8に、ADCの出力データ・レートを落とすと、ADCノイズとリファレンス・ノイズの両方が同時にどう減少するかを示します。例えば、ENBW = 0.6Hz(左)からENBW = 96Hz(右)の間で、100%使用率の際のリファレンス・ノイズは2.3倍減少し、ADCノイズは10倍減少します。その結果総ノイズが大幅に減少します。

図8:0.6Hz(左)、24Hz(中央)、96Hz(右)とENBWを制限することで総ノイズが減少

図8:0.6Hz(左)、24Hz(中央)、96Hz(右)とENBWを制限することで総ノイズが減少

リファレンス設定により同様にシステムに侵入するリファレンス・ノイズの量を減らす方法については、Part 9をご覧ください。

⑩クロックがADCのノイズ特性に影響することはありますか?

ADCのサンプリング周期が完全に一定だと期待できたとしても、必ず理想からは幾分のずれがあります。「クロック・ジッタ」とは、ある周期から次の周期までのクロック波形のエッジの変動量を意味します。すべてのADCがクロック・エッジを使ってサンプリング点をコントロールするので、クロック・エッジの変動によりサンプリングされるものにずれが生じます。このずれの結果、サンプリング周波数が一定でなくなり、新たなノイズ源として変換結果に現れます。図9は、正弦波入力信号上にクロック・ジッタにより生じたサンプリング・エッジの変動を表したものです。

図9:ジッタによるサンプリング・エッジの変動を示すクロック信号

図9:ジッタによるサンプリング・エッジの変動を示すクロック信号

クロックがさらなるエラーをどのように引き起こすかと、クロックに起因するシステム・ノイズを抑える方法については、Part 10をご覧ください。

これらは「信号の分解」シリーズでお答えした最も重要な疑問の一部ですが、お使いの高分解能デルタ-シグマADC信号チェーンから最高のノイズ特性を引き出せるように、さらに 多くのトピックや例も取り上げています。より深く理解するために本シリーズをお読みください。

※すべての登録商標および商標はそれぞれの所有者に帰属します。

※上記の記事はこちらのBlog記事(2019年1月17日)より翻訳転載されました。

※ご質問はE2E Support Forumにお願い致します。