多くのデータ収集(DAQ)システムで、低レベル入力信号の正確な測定が設計上の課題になることがよくあります。例えば、ファクトリ・オートメーションのアプリケーションの多くは、プログラマブル・ロジック・コントローラ(PLC)を使用し、温度センサや負荷セルの値を基に決定を下します。同様に、石油掘削施設では産業用差圧流量計を使用し、ミリリットルの精度で、油田から取り出した石油の量を判断します。

このような工程内の変化を測定するために、さまざまな種類の最終製品で、測温抵抗体(RTD)や、熱電対、抵抗性ブリッジなどのアナログ・センサが用いられています。通常これらのセンサからの信号レベルは非常に低いため、信号をDAQシステムのノイズ・フロア以上に増幅する必要があります。さらにエンジニアは、アナログ/デジタル・コンバータ(ADC)のフルスケール範囲(FSR)を最大限利用することで、ゲインによりダイナミック・レンジを増加させます。どちらの場合でも、アナログ・システムにゲインを追加するには通常、アンプが必要になります。このアンプは、ディスクリート部品のこともあれば、ADCといったシグナル・チェーン部品のどれかに内蔵されている場合もあります。

電子システムに何かしら部品を導入するときと同じく、これらのアンプはノイズの原因になります。このノイズはシステムにどう影響するでしょうか。「信号の分解」シリーズの第6部と第7部では、アンプのノイズと、これが標準的なシグナル・チェーンに与える影響について理解を深めることで、この疑問に対する答えを探っていきます。

第6部では、アンプ・ノイズに関連して次のトピックを主に扱います。

- 出力換算ノイズと入力換算ノイズ

- ADCの入力にアンプを追加

- 低分解能ADCと高分解能ADCの比較

第7部では、市販のADCとアンプを使用した詳細な設計例を用いて、この記事で考察する理論を補完し、さらに発展させていきます。

出力換算ノイズと入力換算ノイズ

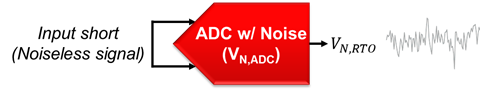

出力換算ノイズ(VN,RTO)は、出力基準のノイズとも呼ばれ、名前が示すとおりADCの出力で測定するノイズのことです。本シリーズの第2部を振り返ってほしいのですが、ADCのメーカーがADCのノイズ特性評価に利用する手法の1つが、図1に示すようにデバイスの入力同士を短絡して出力でのADCノイズを測定し、ADCの固有ノイズを判定することです。

図1:出力換算ノイズの測定

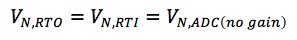

しかし、実際にデータシートで示される値は通常、入力換算値です。出力換算ノイズと同じく、入力換算ノイズ(VN,RTI)は入力基準のノイズとも呼ばれ、ADCの入力でのノイズです。ただし出力換算ノイズと異なり、入力換算ノイズは測定ではなく計算で求めます。ゲイン段が内蔵されていないADCでは、式1で示すように入力換算ノイズは出力換算ノイズと等しくなります。

では、なぜADCのメーカーは出力換算ではなく入力換算でノイズを規定するのでしょうか。図2に示すように、ADCとそのノイズとを切り離した「ノイズのない」ADCと、その前段にADCの入力換算ノイズと等しい電圧源を置いた、等価回路ノイズ・モデルを作成するのが有効です。

図2:ノイズのないADCと、ADCの入力換算ノイズと等価な前段のノイズ源

これで、実際の信号をADCに入力するとき、入力換算ノイズとしてADCのノイズ特性を評価したくなるのが簡単に理解できます。なぜなら、この特性によりシステムの分解能が決まるからです。事実上、入力信号は入力換算ノイズと「競い合う」関係にあります。信号の振幅が入力換算ノイズよりも大きい場合は信号を確認できますが、小さい場合は信号がノイズに埋もれて確認できなくなってしまいます。

究極的には、分解が必要な最小の入力信号がわかっていれば、必要な分解能が得られるADCかどうかは入力換算ノイズから素早く簡単にわかります。これは出力換算ノイズが入力換算ノイズと等しいスタンドアロンのADCではそれほど重要ではないですが、信号パスにアンプを追加したらどうなるでしょうか。

ADCの入力にアンプを追加

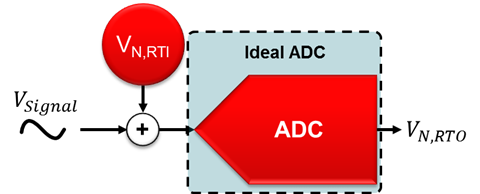

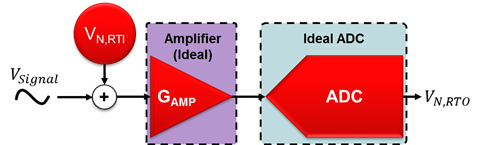

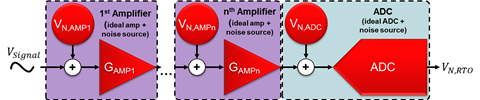

アンプがシステムの全体的なノイズに与える影響を分析するために、ADCと同様にアンプをそのノイズ源から切り離すことができます。この場合、図3に示すように、アンプのノイズ(VN,AMP)と等しい電圧源が前段にある、ノイズのないアンプとしてシステムをモデル化できます。さらに、入力電源(VSIGNAL)にノイズがないと想定できますが、実際ではゲイン段でセンサ・ノイズが増幅されます。

図3:ノイズのないアンプおよびノイズのないADCと、別個の入力基準のノイズ源

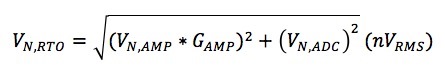

入力換算ノイズを直接測定することはできないため、まず図3に示すシステムの出力換算ノイズを判定する必要があります。アンプとADCのノイズに相関がないと仮定すると、出力換算総ノイズを求めるには、両方の値の二乗和平方根を取ります。

入力信号を増幅する際の残念な副作用は、アンプのノイズも増幅してしまうことです。そのため、まずアンプ・ノイズをアンプのゲインGAMPで逓倍する必要があります。式2は、その結果の出力換算ノイズを示すものです。

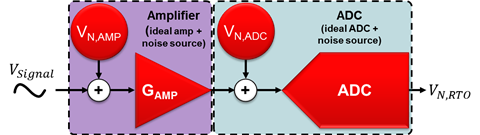

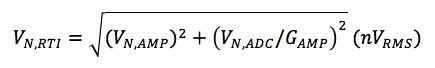

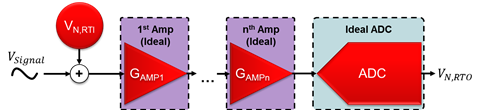

これで、この出力換算ノイズの式を使用し、システムの等価な入力換算ノイズ源に変換することができます。これを求めるには、まず図3の回路図を単純化し、アンプとADCのノイズ源を1つの入力換算ノイズ源(VN,RTI)に統合した等価回路ノイズ・モデルの回路図にします。これで、目的のアプリケーションに対してシンプルなシグナル・チェーン(ADC+アンプ)に十分な分解能があるかどうかを判断できるようになり、解析も単純になります。

図4:ノイズなし部品および1つの入力換算総ノイズ源

出力換算ノイズから入力換算ノイズを算出するには、式3のように個々のノイズ項を回路のゲインGAMPで割ります。

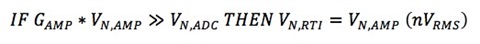

式2と式3のゲイン項GAMPの位置に注意してください。式2ではアンプのノイズがゲインに比例しますが、式3ではADCのノイズがゲインの逆数に比例します。どちらの場合も、アンプのゲインとそれに相当するアンプ・ノイズが十分に大きければ、ADCのノイズは無視できます。式4に示すように、結果としての入力換算ノイズは、アンプのノイズに完全に依存します。これは、アンプがADC内蔵かどうか、またはディスクリート部品かどうかにかかわらず、成り立ちます。

図5のように、シグナル・チェーンにさらにアンプを追加したらどうなるでしょうか。ディスクリートのアンプを複数追加したり、アンプ内蔵や外付けアンプの付いたADCを追加することもあるでしょう。

図5:ノイズのないアンプおよびノイズのないADCと、別個の入力基準のノイズ源

これらのノイズ項をすべてまとめて1つの入力換算ノイズ源にした等価回路ノイズ・モデルを図6に示します。

図6:1つの入力換算総ノイズと、ADCの入力にノイズのないアンプを複数配置

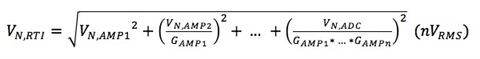

図6と式2および式3を用いて、式5に示すように、このようなn個のアンプがある拡張シグナル・チェーンの入力換算ノイズを判定できるようになります。  (5)

(5)

前の例と同じく、新しい入力換算ノイズ式もシグナル・チェーンのすべてのデバイスからのノイズに依存します。しかし、各項はすべてのアンプ・ゲインの積の逆数で逓倍されますが、最初の項(最初のアンプの電圧ノイズ)だけはゲインと無関係です。

式4と同様に、1段目のゲインが大きい場合、式5のその他すべての項が事実上ゼロに近づくことになり、結果としてシステムの入力換算ノイズは1段目のアンプのノイズのみに依存することを意味します。そのため、単一段または複数段のアンプ構成で最良の性能を得るためには、1段目にゲインが大きい低ノイズ・アンプを選択してください。

式4で示すように、この選択がすべてのADCで同じように効果があるわけではありません。実際に、低分解能のADCを高ノイズのアンプと組み合わせたり、より大きいゲインを利用しながら必要なシステムのノイズ特性を満たしたりもできるでしょう。そのほかにも、高分解能のADCではゲインがわずかに増加しても何の効果も感じられないかもしれません。

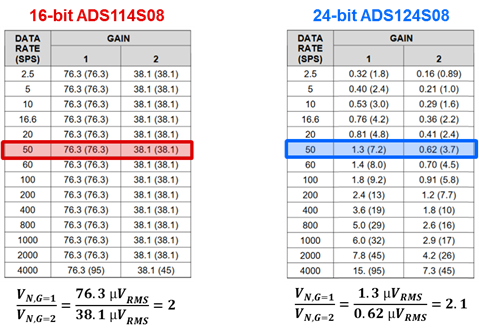

これらの結論を、16ビットの『ADS114S08』と24ビットの『ADS124S08』を比較して、さらに詳しく分析してみましょう。この2つのADCは、分解能は異なるものの、アンプ・ノイズが同じプログラマブル・ゲイン・アンプ(PGA)を内蔵するなど、それ以外は同等です。この類似性のため、ADCの分解能の違いがゲインの変化によりシステム・ノイズにどう影響するかを分析することができます。

低分解能ADCと高分解能ADCの比較

図7に示すのは、『ADS114S08』と『ADS124S08』について、使用できるすべてのデータ・レートに対するゲイン1V/Vおよび2V/Vでの入力換算ノイズです。データ・レートをどれか選択し(例えば50SPS)、各ゲインでの入力換算ノイズの比をとると、どちらのADCでもほぼ2となります。言い換えれば、ゲインが2倍に増加するとき、同時にノイズは1/2に減少します。この場合、ゲインを追加することで、高分解能(24ビット)と低分解能(16ビット)のADC両方でシステムのノイズ特性が改善します。

図7:G = 1および2V/Vでの入力換算ノイズ(µVRMS [µVPP])の表 – AVDD = 3.3V、AVSS = 0V、PGA有効、グローバル・チョッピング無効、内部基準電圧2.5VでのSINC3フィルタ

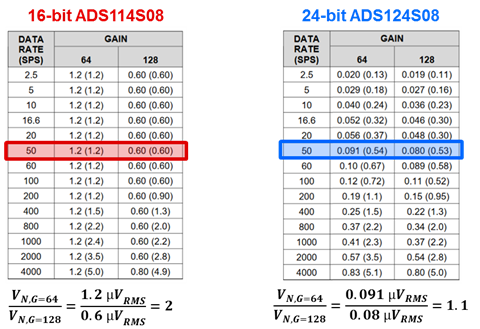

これを図8の場合と比べてください。図8では、64V/Vおよび128V/Vの最高ゲインを使用して同じ計算をしています。低分解能のADCでは比率が2のままですが、高分解能のADCでは約1に減少しています。この高分解能ADCの例では、ゲインが増加してもノイズ特性の向上につながっていません。なぜこの違いが生まれるのでしょうか。

図8:G = 64および128 V/Vでの入力換算ノイズ(µVRMS [µVPP])の表 – AVDD = 3.3V、AVSS = 0V、PGA有効、グローバル・チョッピング無効、内部基準電圧2.5VでのSINC3フィルタ

分解能が低い(量子化ノイズが支配的な)ADCでゲイン間の比率が一定である理由は、アンプのノイズに比べてADCのノイズのレベルが高いからです。この場合、ADCのノイズがアンプのノイズよりずっと大きいため、式4で記述された条件は満たされません。ADCのノイズは、ゲインを2倍に増加させるたびに確かに減少します。しかし、その最低レベル(G = 128V/V)でも、アンプのノイズと比べて依然としてADCのノイズが支配的です。そのため、実際に測定でアンプ・ノイズが「見える」ことはなく、この特定のシグナル・チェーンはアンプの性能にあまり左右されないため、ゲイン値を大きくすることでノイズ特性を改善できる可能性があります。

分解能が高い(熱ノイズが支配的な)ADCの場合は、両方のADCで用いられるアンプが同じだとしても、逆のことが言えます。この場合、ゲインで逓倍されたアンプ・ノイズと比べてADCのノイズがかなり低いため、式4の条件を満たします。結果として、VN,RTIは実質的に一定になり、ゲインを増やしても入力換算ノイズ性能は事実上変化しません。このような状況では、アンプ性能が非常に重要です。多くの場合、アンプを使用すると、まったくアンプを使用しないシステムよりもシステムの分解能が悪くなります。

この論点をさらに詳しく考察するために、「信号の分解」シリーズの第7部では、さまざまな外部アンプを高分解能ADCの入力に付け加えた設計例を取り上げ、それぞれの組み合わせでのシステム・ノイズ特性を比較します。

重要なポイント

以下は、アンプのノイズがデルタ-シグマADCに与える影響をより良く理解するうえで重要なポイントをまとめたものです。

- ゲインのないシグナル・チェーンでは、出力換算ノイズは入力換算ノイズと等しい

- 出力換算ノイズは測定で求め、入力換算ノイズは計算で求める

- 入力換算ノイズはシステムの入力分解能を表す

- システムの入力換算ノイズで支配的なのは、(部品のノイズ値が同様で1段目のゲインが大きいと想定すると)1段目のアンプのノイズである

- 高分解能(低ノイズ)ADCをノイズの多いアンプと一緒に使用すると、システム性能が低下する

- 最良のノイズ特性を得るには、低ノイズで小信号ゲインのアンプを1段目として構成するのが一般的である

著者紹介

Bryan Lizon(Texas Instruments)

※すべての登録商標および商標はそれぞれの所有者に帰属します。

※ご質問はE2E Support Forumにお願い致します。