第11部では、電源ノイズについて取り上げ、ノイズが多い電源になる原因や、A/Dコンバータ(ADC)に与える影響などにつ��て述べました。また、ノイズ除去において電源の影響の度合いを測定する方法として、電源除去(PSR)を紹介し、電源ノイズが各種のADC電源に与える影響を分析しました。

最終回となる第12部では、ADS127L01評価モジュール(EVM)を使用した設計例を用いて、引き続き電源ノイズについて考察します。この設計例を用いることで、システムのPSRを高めようとする際に、どの電源が最も重要かがわかりやすくなります。最後に、電源ノイズを低く保つベストプラクティスと、システムの総ノイ��特性を改善するデバッグのヒントについても説明します。

AVDD、DVDD、LVDD:一番重要なのはどの電源か

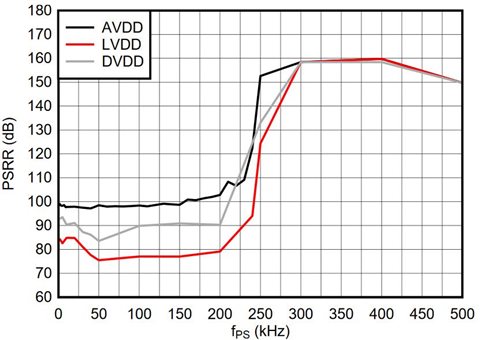

第11部では、TIの『ADS127L01』で使われる各電源のPSR比(PSRR)を確認し���した(図1)。多くのADCと同じように、ADS127L01はアナログ電源(AVDD)とデジタル電源(DVDD)の両方を使用します。説明用にこのデバイスを選んだ理由は、このデバイスには低電圧ドロップアウト電源(LVDD)と呼ばれる3つ目の電源が必要だからです。LVDDは、ADS127L01のデルタ・シグマ変調回路に直接電源を供給します。LVDD電源は、内蔵低ドロップアウト(LDO)レ��ュレータ(AVDDに接続)または外部LVDD電源のどちらかから供給されます。この記事の後の方で述べますが、ノイズの多い電源を使って外部からLVDDを駆動すると、ADCのノイズ特性への悪影響が最も大きくなります。

図1:TA=25°C、AVDD=3.3V、VREF=2.5V、HRモード、¯INTLDO¯=1

図1を見ると、3つの電源のうちでLVDDのPSRRが最も低いため、ADC出力への結合ノイズに最も影響を受けやすいのはLVDDになります。LVDDはデルタ・シグマ変調回路に直接電源を供給し、次に変調回路がアナログ入力からデジタル出力への変換処理を直接制御するため、LVDDがノイズの影響を最も受けます。それに比べてAVDDは、メインのバイアス電流の生成を含め、その他のアナログ回路に電源を供給しますが、変換処理の結果に与える直接的な影響は大きくありません。ADCのデジタル・コアに電源を供給するDVDDは、変調回路の出力がデジタルデシメーション・フィルタに達する前にすでにバイナリ形式になっているため、変換処理の結果に与える影響は最も低くなります。複数の電源が必要なデバイスでは、デルタ・シグマ変調回路に最も直接的に電源を供給する電源を優先させますが、通常はAVDDです。

ノイズの多い電源で変調回路を駆動したときの影響を実物で明らかにするために、ADS127L01評価モジュール(EVM)で入力短絡によるADCのノイズ測定を行いました。使用した条件は次の4つです。

- AVDD、LVDD、DVDDにクリーンな電源を供給(リップルなし)

- AVDD = 3V + 1kHz、100mVPリップル、クリーンなLVDDとDVDD

- LVDD = 1.825V + 1kHz、100mVPリップル、クリーンなAVDDとDVDD

- DVDD = 1.8V + 1kHz、100mVPリップル、クリーンなAVDDとLVDD

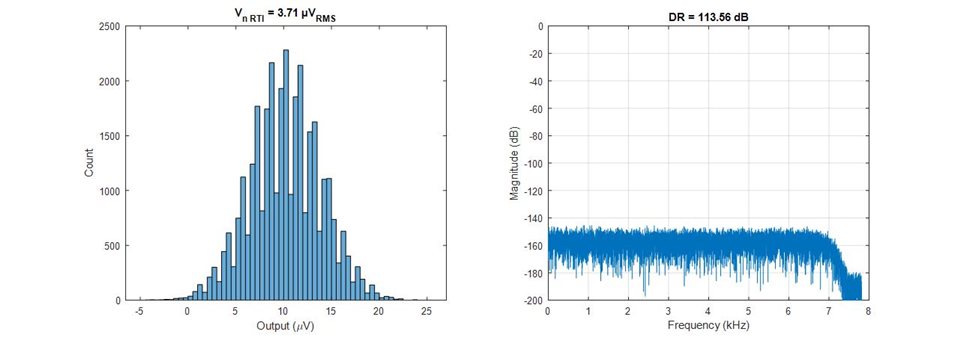

それぞれのケースで、ADCの入力同士を短絡し、それに中間電源電圧(1.5V)のバイアスをかけ、ADCのフルスケールに対する実現可能な最大の信号対雑音比を計算しました。この結果は、ADCのダイナミック・レンジと呼ばれます。ADS127L01データシートの表1に、ADCの動作モードとデータ・レートの各々に対する標準ノイズ特性が記載されています。このテストは、オーバーサンプリング比を256にし、広帯域2デジタル・フィルタを使った4MHzクロック入力の超低電力モードで行われました。表1から、この設定のときのダイナミック・レンジは約114dBと想定されます。

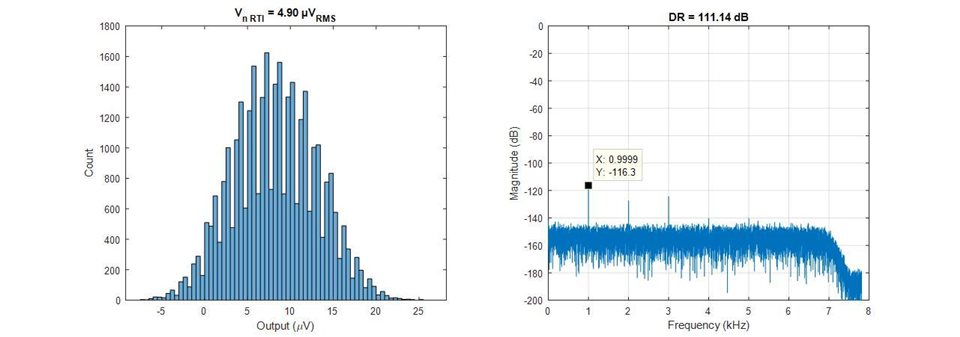

想定どおり、EVMは、ADC電源ピンの3本すべてにクリーンな電源を使用したときに最も高い性能を発揮します。図2は、この条件でのノイズ・ヒストグラム(左)と高速フーリエ変換(FFT)(右)のグラフです。ダイナミック・レンジは113.56dBと、データシート仕様に非常に近くなっています。

図2.AVDD、LVDD、DVDDにクリーンな電源を使用したときのノイズ・ヒストグラム(左)とFFT(右)

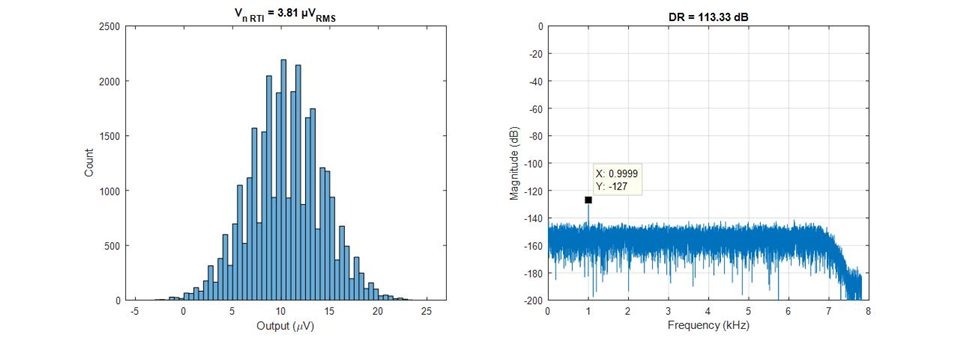

次に、3VのAVDD電源に1kHz、100mVPの正弦波を乗せました。この正弦波は電源ノイズを模しており、公称AVDD電源電圧(3V)と等しいDCオフセットで信号発生器を使ってADCに与えます。このケースでは、このノイズはADS127L01の内蔵LDOでもほとんど除去することができ、図3に示すように113.33dBの定格性能を維持できました。1kHzの周波数スペクトルに-127dBの大きさのわずかなトーンが現れているのが見えるでしょうか。これは、フルスケールに対する元々の入力信号レベル(2.5VのADCリファレンス電圧に対して-28dB)からAVDDのPSRR、つまり約100dBを引いたものと相関があると思われます。

図3.LVDDとDVDDにクリーンな電源を使用、AVDDにリップルを乗せたときのノイズ・ヒストグラム(左)とFFT(右)

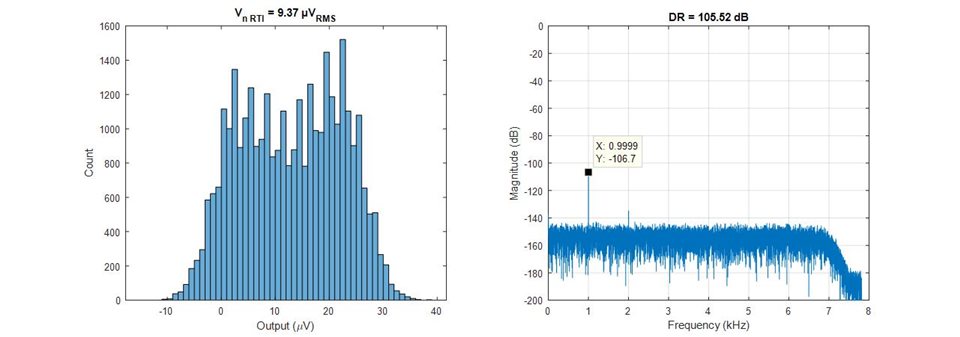

次のテストでは、EVMのAVDD電源をデフォルトに戻し、信号発生器を使ってLVDD電源を供給します。このテストでは、1.825VのDCオフセットを中心とする1kHz、100mVPの正弦波リップルを入力し、内蔵LDOはバイパスしています。その結果、LVDD電源ノイズが原因で、図4に示すようにノイズ特性が大きく悪化しました(105.52dB)。また、図3の右図に比べて、周波数スペクトルの1kHzのトーンがよりはっきりと見えます(-106dB)。

図4.AVDDとDVDDにクリーンな電源を使用、LVDDにリップルを乗せたときのノイズ・ヒストグラム(左)とFFT(右)

最後のテストでは、EVMのAVDDとLVDDをデフォルトのクリーンな電源に戻し、DVDDに正弦波を与えました。このケースでは、1kHz、100mVPの正弦波リップルの中心は1.8VのDCオフセットです。興味深いことに、図5では、FFTでは1kHzリップルの高調波成分が増えているにもかかわらず、ダイナミック・レンジはLVDDで試したときよりも悪化していません(111.14dB)。

図5.AVDDとLVDDにクリーンな電源を使用、DVDDにリップルを乗せたときのノイズ・ヒストグラム(左)とFFT(右)

最終的に、これらの実験からは、図1の結果が確かめられるとともに、一部の電源(特にデルタ・シグマ変調回路に供給する電源)は他の電源に比べて電源ノイズの影響を受けやすいということと、そのため高いPSRを維持��る��はこれらの電源に特に注意す���必要があることが再認識できます。

PSRRの改善

それでは、システムのPSRRを良好に維持するいくつかの方法を、3つの異なる手法を使用して検討していきましょう。初めに、最も肝心なレイアウトについて説明します。

- レイアウトの最適化

レイアウトの最適化は、PSRRの改善とシステム性能の維持に用いることができる、圧倒的に重要な手法です。電源に結合するDC/DCスイッチング・レギュレータのノイズについての説明を長々としてきた中で、実行可能なレイアウト最適化手段の1つ が、影響を受けやすいアナログ入力からスイッチング・レギュレータを離して、���のノイズを分離することです。スイッチング・レギュレータは効率が非常に高いものの、電源に注入される過渡事象が大きく、これが周りの回路やADC自体にも結合します。プリント基板(PCB)の同じ面にデジタル部品と電源調整回路があれば、ノイズの多いリターン電流はどれも、より影響を受けやすいアナログ回路を流れずに済みます。

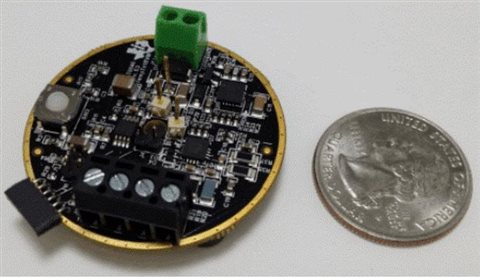

しかし、PCBによってはサイズや形状の制約が厳しく、このようなレイアウト手法が使えません。例えば、図6は、PCBのサ���ズを硬貨と比較したときの画像です(TIの温度トランスミッタのリファレンス・デザインの1つ)。このように限られたスペースでは、レイアウトを最適化するのは困難でしょう。

図6.温度トランスミッタのPCBと硬貨の比較(TIDA-00095)

このよう場合は(すべてのPCBレイアウトに言えることですが)、常に適切な電源デカップリングを使用するようにしてください。デカップリング・コンデンサは、大きくバルクとローカルの2つに分けられます。バルク・デカップリン���・コンデンサは、一般に電源の出力に直接配置されます。このコンデンサは、電源の出力をフィルタリングし、負荷電流が変動しても安定した電圧を維持するのに役立ちます。それに加えて、ほとんどのアクティブ部品には、主電源ピンそれぞれのすぐ横にローカル・デカップリング・コンデンサが少なくとも1個必要になります。ローカル・コンデンサは、一般にバルク・コンデンサに比べて容量が1桁小さく、高周波数ノイズをフィルタで除去しながら、デバイスからの瞬間的な電流要求に対応するのに使われます。特定の電源ピンにデカップリング・コンデンサを2つ以上(例えば0.01µFと1µFを並列で)使用することが推奨される場合は、小さい方のコンデンサが電源ピンに近くなるように配置してください。

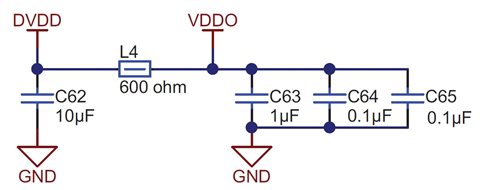

さらに、第11部では、クロックなどのある種のアクティブ部品から電源に、大きな過渡電流が流れる可能性があることをお話ししました。このノイズは、直列フェライト・ビーズといったデカップリング部品を追加することで抑えることができます。図7は、ADCとクロック・ファンアウト・バッファ電源にデカップリング部品がいくつか追加された、ADS127L01EVMの回路図の一部です。このファンアウト・バッファは、『ADS127L01』のデジタル・コア(DVDD)と同じデジタル入出力レベルを基準としなければならず、このことでスイッチング過渡事象がこの電源に結合してしまうことがあります。システム性能を維持するために、EVMではコン��ンサとフェライト・ビーズを使って、ファンアウト・バッファ出力電源(VDDO)からDVDDをデカップリングします。

図7.ADS127L01EVM回路図でのADCのデジタル電源(DVDD)とクロック・バッファ出力電源(VDDO)の

デカップリング部品(コンデンサとフェライト・ビーズ)

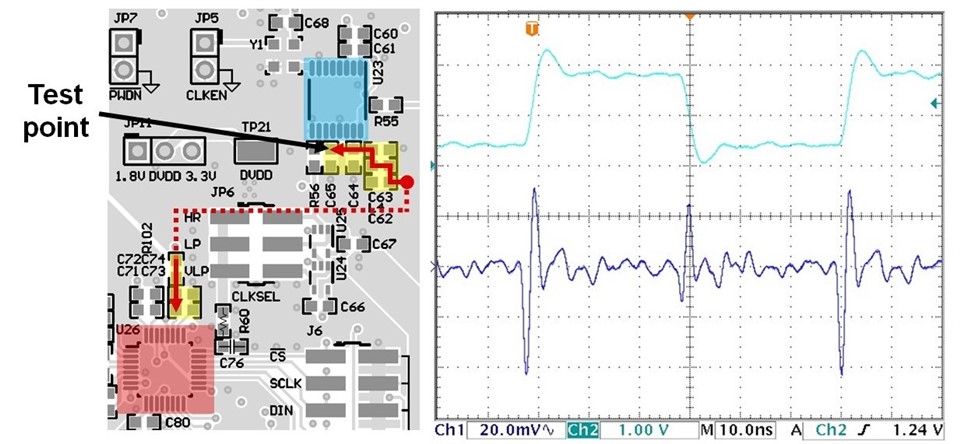

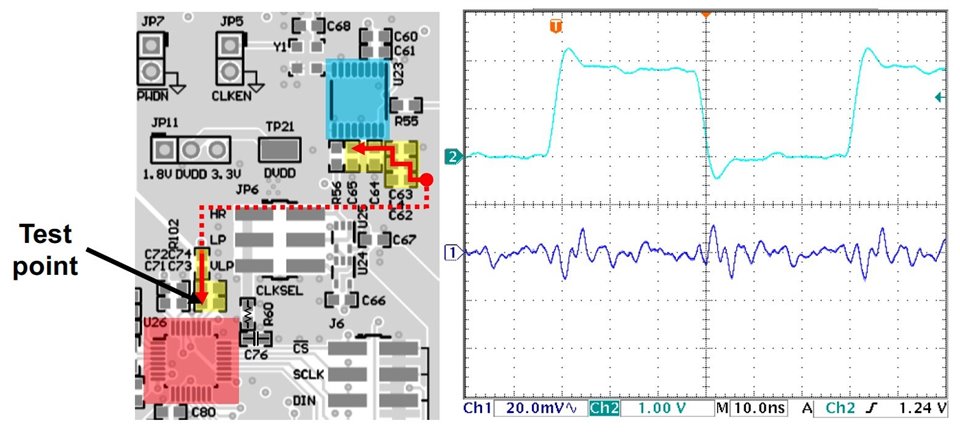

偶然にも、ADS127L01EVMのクロック・ファンアウト・バッファとその一般的なクロック回路については、以��に第10部でお話しました。そのときは、ファンアウト・バッファを青で、ADCを赤で強調表示したEVMのクロック回路をお見せしました。図8の左はそれと同じ図に同じように強調表示したものですが、今回はさらにデカップリング部品を黄色で、IOVDD電源へのDVDD電源パスを赤の矢印で示しています。

図8の左図に、IOVDD電源ピンのテスト・ポイントを黒い矢印で示しています。右図は、このポイント(Ch1)の電圧のオシロスコープ画面をキャプチャしたものです。この画面キャプチャでは、C65における出力クロック信号(Ch2)の立ち上がりと立ち下がりのそれぞれのエッジで、バッファにより大きな電源過渡が生じているのがわかりま���。

図8.ADS127L01EVMの回路図(左)とバッファ・テスト・ポイントでの電圧計測(右)

図7に示したデカップリング回路がなければ、図8の右図に示される過渡事象がDVDDに結合し、図5で示した結果のように、ADCの性能に影響するでしょう。しかし、適切にデカップリングすることで、このようなグリッチをクロック・ファンアウト・バッファの出力の中に封じ込めることができます。図9の左図に黒い矢印で示したテスト・ポイント(C73)で、オシロスコープ画面をキャプチャした図9の右図を見ると、封じ込めの効果は明らかです。図8の過渡事象は、図9のキャプチャでは事実上取り除かれ、ADCまで到達する電源ノイズがほとんどなくなっていることに注目してください。

図9.ADS127L01EVMの回路図(左)とADCテスト・ポイントでの電圧計測(右)

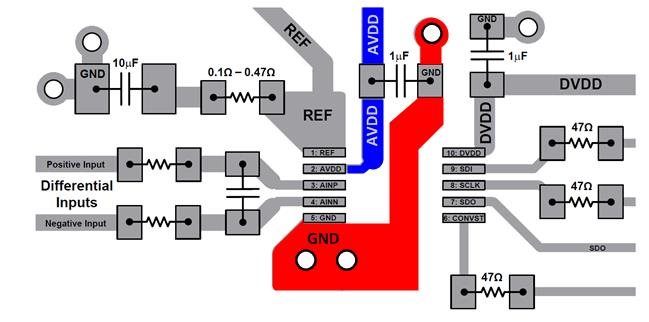

配線も、電源ノイズを低く維持するために検討すべき、もう1つのレイアウト手法です。可能な限り必ずソースからコンデンサのパッドを通り、それからデバイス・ピンへと電源ラインを配線してください。また、大電流が流れる可能性がある電源には、幅広のパターンを使用します。そして、グランドも電源の1つであることも忘れないでください。グランドは、信号と電源の両方で、電流のリターン・パスの働きをします。大きいグランド銅箔や余分なビアがあるプレーンを使用することで、リターン・パスのインダクタンスが減少し、リターン電流がソースに戻る経路を見つけやすくなります。これらの考え方の一部を図10に示します。

図10.幅広パターン、コンデンサのパッドを通る配線などの配線手法

- 周波数プランニング

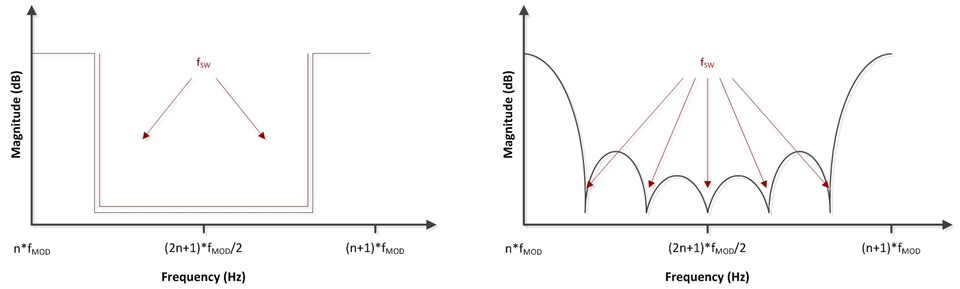

電源ノイズの低減に使用できるもう1つの手法では、スイッチング・レギュレータかADCのどちらかに周波数プランニングを利用します。第11部で説明し、図1にも再掲したように、ADCの電源はそれぞれ異なるPSRR特性を示す可能性があります。それに加えて、ADCのすべての電源は、デジタル・フィルタの遮断帯域内の周波数でPSRRが急増します(図1参照)。デルタ-シグマADCでは、このデジタル・フィルタ応答が変調器周波数(fMOD)の倍数で繰り返されます。したがって、スイッチング・ノイズが変調回路周波数かその倍数に近い場合、このノイズはADC通過帯域に折り返すことになるかもしれません。

これらの信号が折り返さないようにしてシステムのPSRを改善するためには、可能であれば、フィルタのNULLのうちのどれか(通常は出力データ・レートの倍数)に当たるスイッチング周波数を選択してください。図11に、一般的な種類のADCフィルタの遮断帯域を示します。図11の左図は広帯域有限インパルス応答フィルタ、右図はSINCフィルタです。ADCのデータ・レートはシステム要件により固定されているのが普通なので、赤の矢印で指した領域が、デジタル・フィルタ応答に基づいてスイッチング周波数に推奨される帯域です。データ・レートは自由に変えられるが、スイッチング周波数は固定されている場合に、その周波数がNULLとなるようなADCの出力データ・レートを選択してください。

図11.フラットな通過帯域フィルタ(左)とSINCフィルタ(右)を使用した場合の、推奨されるスイッチング周波数帯

- LDOの追加

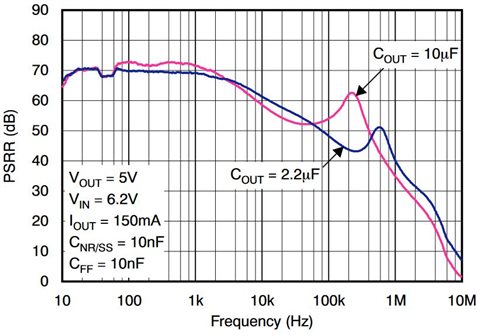

この記事の最初のセクションでお話したように、LDOを追加して不要なノイズを抑制することで、システムのPSRRをさらに改善できます。システムでスイッチング電源を使う予定である場合は、システムに最適な効果が出る特定のスイッチング周波数も検討してください。この手法は、すべての高分解能ADCアプリケーションに利用可能ですが、ノイズが結合したり出力に折り返したりしやすい広帯域アプリケーションでは、より重要です。この場合は、使用予定のスイッチング周波数での電源除去が最も大きいLDOを選択してください。あるいは逆に、LDOのPSRRがグラフで最高になる範囲のスイッチング周波数を検討してください。図12は、TIのLDOである『TPS7A49』で、PSRRを周波数に対してプロットしたも��です。このLDOのPSRRは、スイッチング周波数が高くなると減少することに注目してく��さい。

図12.TPS7A49 LDOの周波数に対するPSRRのプロット図。COUT= 2.2µF

電源の問題を防ぎ、解決するには

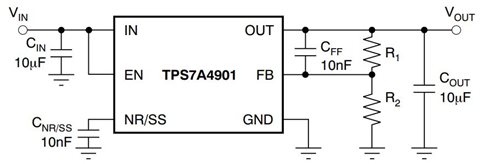

ADCの電源設計を見直す際には、潜在的な問題を除外して最初の段階を無事通過するために、いくつかのパラメータを確認するところから始めるとよいでしょう。各部品の出力電流制限や入出力電圧範囲といった、主要な電源仕様を見直すことから始めましょう。電源を共有するすべてのアクティブ部品の総消費電流を考慮し、バジェットに余裕を組み込むようにしてください。また、電源の出力の最大容量性負荷を確��してください。その電源のバルクとローカルのすべてのデカップリング・コンデンサは実質的に並列であり、簡単に合計できます。容量が大きすぎると、起動が遅くなる可能性があります。最後に、LDOの入力と出力の間に少なくとも最小ドロップアウト電圧があることを確認してください。図13に示すように、フィルタリングを強化するために、推奨するその他のノイズ低減コンデンサ(CNR)やフィードフォワード・コンデンサ(CFF)の追加も検討してください。

図13.LDOのフィルタリング・コンデンサ

使用する電源が正しく設定されているのが確認できたら、フィルタリング強化のためにADCのデカップリング・コンデンサのサイズを大きくして、ノイズ特性全体の改善に取り組みましょう。これは、主電源ピンだけでなく、外付けデカップリング用の専用ピンにつながるどの内部電圧ノードでも有用です。それらに対しても普通はADCメーカーが推奨する容量値があります。最高の性能を得るには、容量の大きいコンデンサと並列に容量の小さいコンデンサを配置し、小さい方がコンデンサがデバイス・ピンに近くなるように配置することを忘れないでください。

最後に、電源調整部品自体のせいでADCスペクトルにトーンが生じると考えられる場合は、それぞれのADC電源を一度に1つずつ、外部ベンチ電源と置き換えてみてください。これでも問題箇所が明らかにならない場合は、ノイズの発生源を特定するために、基板の主電源を置き換えてみるのもいいでしょう。

これで、TIの「信号の分解」シリーズを終わります。楽しみながらアナログ・シグナル・チェーン設計のノイズについて理解を深めていただけたなら幸いです。

著者紹介

Bryan Lizon(Texas Instruments)

テキサス・インスツルメンツ 高精度ADC製品プロダクト・マーケティング・エンジニア

※すべての登録商標および商標はそれぞれの所有者に帰属します。

※ご質問はE2E Support Forumにお願い致します。