電源のレール要件に関する前回のブログ記事はご覧いただけたでしょうか。今回は、フィールド・プログラマブル・ゲート・アレイ(FPGA)電源設計におけるもう1つの重要なトピックである、シーケンシングについて説明します。FPGAへの電源投入時/遮断時は、特定の順序で電源をオンにする必要があります。実際のシーケンシングの順序はさまざまですが、一般にコア・レールは最初にオンになり、かつ最初にオフになります。電源のオン動作は単調でなければなりません。つまり、FPGAに電力を供給する出力電圧は継続的に上昇する必要があります。最後に、レール全体への電源投入が最初から最後まで完了する時間についての要件があり、通常はすべてのレールが40または50ms以内に95%に達する必要があります。このブログ記事では、3つの一般的なシーケンシング手法について見ていきます。

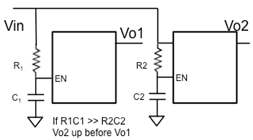

最初に紹介する最も単純な手法が、図1に示す抵抗-コンデンサ(RC)シーケンシングです。電源がオンになるとき、デバイスがオンになるタイミングはRC時定数によって決まります。つまり、電源ごとのRC値を調整するだけで、オンになるタイミングをずらすことができます。図1を見ると、RC時定数の小さい電源が最初にオンになることがわかります。これに似た別の手法として、一部の電源が遅れてオンになるようにソフトスタートを調整するというものがあります。ただし、これらの手法はパワーダウン・シーケンスに対応できず、温度の変動時や、何らかの障害によってパワー・サイクルの中断や繰り返しが発生している場合に、信頼性が低下する可能性があります。

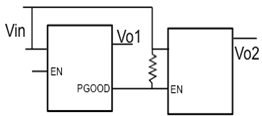

前述した手法より大幅に効果的かつ信頼性の高い手法が、図2に示す電源のカスケード接続です。この手法では、最初のデバイスのパワー・グッド・ピンの出力を次にオンにする電源のイネーブル・ピンに接続します。つまり、最初のデバイスのパワー・グッドがHighになると、次のデバイスのターンオンがトリガされます。この手法は基本的なRCシーケンシングよりも信頼性に優れていますが、やはりパワーダウン・シーケンスには対応できません。

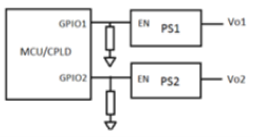

図3に示す最後のシーケンシング手法では、マイクロコントローラ(MCU)を使用してシーケンシングを行います。この手法にはソフトウェアが必要になるほか、タイマ、汎用入出力(GPIO)、MCUの帯域幅を使用します。MCUは、各電源の出力電圧を検出し、プログラミングされたシーケンスに基づき、次のデバイスにターンオン(またはターンオフ)を開始するよう伝える頭脳として機能します。この手法は最も複雑ですが、最も詳細に制御できる手法でもあり、パワーアップ・シーケンスとパワーダウン・シーケンス両方のプログラミングが可能です。

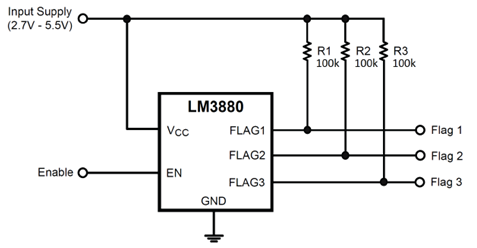

もう1つの選択肢として、TIのLM 3880簡易シーケンサというソリューションもあります。図4に示すように、LM 3880には3つのレールがあり、R1、R2、R3の値を操作して3つのデバイスをターンオン/ターンオフできます。最初に紹介した2つの手法より高い信頼性が必要で、3つ目の手法を実装するためのMCU帯域幅がないという場合は、これによって単純なシーケンシング手法が実現できます。必要に応じてLM 3880をデイジーチェーン接続すれば、4つ以上のデバイスのシーケンシングにも対応できます。

図4:LM 3880簡易シーケンサ

図4:LM 3880簡易シーケンサ

システム・アーキテクチャを選択し、電源レール要件を把握し、シーケンシング戦略を選定したら、電源に必要な主要機能および性能指標をより深く理解できているはずなので、いよいよ部品の選択を開始します。これについては、FPGA電源に関するこのシリーズの最終回となる次回の記事で説明します。

その他のリソース

上記の記事は下記 URL より翻訳転載されました。

https://e2e.ti.com/blogs_/b/powerhouse/archive/2017/11/13/fpga-power-made-simple-sequencing

※すべての商標および登録商標はそれぞれの所有者に帰属します。

*ご質問は E2E 日本語コミュニティにお願い致します。