우주에서는 위성 PLL 합성기 디자인이 얼마나 복잡하고 비용이 많이 드는지 아무리 말해도 들어줄 사람이 없다.

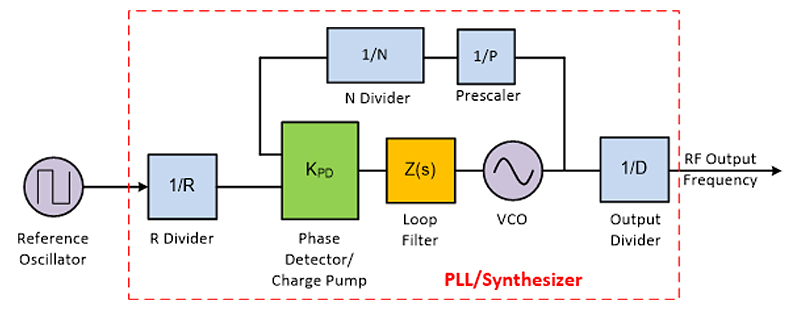

PLL(phase-lock loop) 합성기를 설계하기 위해서는 다수의 개별 부품이 필요하므로 상당한 공간을 차지하고 무게를 증가시킨다. 통상적인 PLL 디자인은 전압 제어 오실레이터(VCO), 합성기, 높은 주파수를 수용하기 위한 추가적인 프리스케일러/분할기 또는 출력 체배기 같은 다수의 이산적인 부품들로 이루어진다. 또 어떤 경우에는 시스템으로 잡음을 최소화하고자 별도의 위상 검출기/차지 펌프를 사용하기도 한다. 이와 같이 긴 부품 목록 때문에 디자이너가 우주에서 사용하기 위한 용으로 크기가 작고 가벼운 시스템을 설계하려고 할 때 솔루션 크기와 설계 복잡성이 문제가 될 수 있다.

이것은 초기에 휴대전화 디자이너들이 무선 주파수(RF) 및 마이크로파 부품들을 단말기 안으로 집어넣으려고 할 때 직면했던 것과 같은 문제이다. 당시에 등장해 있던 IC들을 사용해서 휴대전화 단말기를 설계하기 위해서 상당히 많은 수의 이산적인 부품들을 사용해야 했다. 그럼으로써 단말기가 크기가 크고 가격이 비쌌으며 배터리 시간은 짧았다.

휴대전화와 위성 시스템에 사용되는 합성기는 요구사항이 많이 다르지만, 성능은 높이면서 크기를 줄여야 하는 요구는 동일하다. 그렇다면 예전에 벽돌 크기의 단말기에서 오늘날에 주머니에 쏙 들어가는 날렵한 스마트폰으로 어떻게 진화할 수 있었으며 위성 시스템 디자이너들이 PLL 디자인을 어떻게 간소화할 수 있을 것인가? 이것은 바로 RF 및 합성기 부품들을 모노리딕 RF IC로 통합함으로써 가능한 것이다.

통합은 오늘날 디자이너들에게 생소한 개념이 아니며, 우주용이나 휴대전화 디자인에만 해당되는 것도 아니다. 통신 위성은 넓은 범위의 RF 및 마이크로파 주파수를 사용한다. 위성-대-지상 및 위성간 통신 시스템 모두로 복잡성이 높아짐으로써 변화된 새로운 아키텍처가 필요하게 되었다.

속도는 높이고 보드 공간은 줄이고

| 우주 애플리케이션 용으로 LMX2615-SP RF PLL 합성기를 사용함으로써 최대 15GHz 속도 달성 및 보드 공간 90%까지 축소. |

VCO, PLL 분할기, 차지 펌프, 지원 회로를 포함하는 다수의 부품들로 이루어진 기존의 디스크리트 합성기 솔루션은 8인치 x 10인치에 이르는 풋프린트를 차지할 수 있다. 하지만 통합 수준을 높임으로써 동일한 기능을 1인치 x 1인치의 PCB 면적 안으로 집어넣을 수 있다. 열을 소산시키는 것과 관련된 문제를 피하기 위해서는 전반적인 전력 소모를 최소화하는 것이 중요하다. 내부적 전원 공급을 위해서 LDO를 통합함으로써 외부적으로 필요로 하는 내방사선 부품을 추가적으로 줄일 수 있다.

그림 1은 PLL/합성기 기능 블록으로서, 이 기능들을 부분적으로 혹은 전체적으로 모노리딕 RF IC로 통합할 수 있다는 것을 보여준다.

그림 1: RF PLL/합성기 기능 블록

통합은 신뢰성을 높이는 데도 도움이 된다. 멀티코어 VCO를 통합한 광대역 합성기는 이산적인 VCO 모듈들을 사용하는 것에 비해서 시스템 크기를 최소화할 수 있는 직관적이면서 비용적으로 경제적인 방법이다. 솔루션 표면적이 줄어들면 부유 중이온이 주요 부품들을 타격하고 정상 작동을 방해할 가능성을 낮출 수 있다.

설계 간소화

그러므로 이제 우주에서 사용하기 위한 RF 합성기를 더 손쉽게 설계할 수 있게 되었으며, 기존 디자인으로 공간을 절약할 수 있다. 또한 RF IC로 기능들을 통합함으로써 우주용 디자인의 까다로운 성능 요구를 더 잘 충족할 수 있다.

추가 정보

- 애플리케이션 노트 “RF 합성기 VCO 캘리브레이션 간소화 및 PLL 동기 시간 최적화”

- Electric Products에 게재된 기사 전문 보기: “우주용 PLL 합성기로 부품 통합이 왜 중요한가?”

리암 키스(Liam Keese), TI RF 모바일 전력 시스템 및 애플리케이션 매니저

(원문 보기)