作者:德州儀器 Zach Imm 與Sam Jaffe

隨著車用設計與時俱進,需要更高功率的應用越來越多。工程師設計高功率系統時,常常把低壓差(LDO)穩壓器改成直流/直流降壓轉換器,因後者的轉換效率與散熱表現較佳。然而,這樣的改動有其代價,因為直流/直流降壓轉換器的電磁干擾(EMI)比起所替代的LDO穩壓器高出許多。

而EMI會影響敏感元件,如AM/FM收音機接受器、駕駛輔助感測器等,甚至嚴重時還會導致系統失常,所以國際無線電干擾特別委員會(CISPR)等官方標準規範了帶有內燃機的車輛與船隻須遵守的EMI限制,像是CISPR 25 Class 5 (5個等級)。

突破電路板佈線限制

降低EMI最簡單的方法,就是使用正確的印刷電路板(PCB)佈線。對於降壓轉換器,最重要的考量是:

- 降低高瞬態電壓(dv/dt)節點的表面積

- 降低高瞬態電流(di/dt)環路上的環路面積

這些考量決定了特定元件的配置,如果配置正確,就能使 EMI降至最低。

但是,電路板的尺寸與形狀會限制特定元件的配置方式,從而導致洗板所需時間與開銷過高。我們要如何在重重限制中,仍然符合CISPR 25 Class 5的EMI規定呢?

如果無法改善EMI佈線方式,以下列出幾個直流/直流轉換器搭配萬用佈線封裝(layout-agnostic package),從裝置層級(device-level)改善以壓低EMI。

低EMI的裝置層級功能

展頻功能可以透過抖動(dither)切換頻率,來分散開關節點所產生的EMI諧波,展開諧波中集中的能量,分散到其他頻率,如此就不需要太多的濾波與最佳化,也能讓設計符合規範。

控制迴轉率(slew-rate)可以降低高壓側場效應電晶體(FET)的起動時間,進而降低高頻諧波的能量。只要在起動電容多串連一個小電阻,或在帶有此功能裝置的RBOOT針腳加一個起動電阻,就能達成效果。儘管降低FET的迴轉率可以改善EMI,但同時也會影響效率。

低EMI封裝

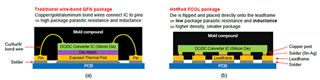

TI的HotRod導線架上覆晶封裝(flip-chip-on-lead frame),是能夠抑制EMI的封裝等級,如圖1所示,內部沒有接合打線。透過移除在輸入端電容不連續電流高di/dt環路上電感性的接合打線,可以消除輸入環路電感的一個主要來源,並滿足上面提到的其中一個主要考量:降低高di/dt環路的面積。

圖1:標準導線接合四方扁平無引線(QFN)封裝與HotRod封裝的橫截面

另一個封裝等級的特色,是在關鍵線路上使用對稱針腳。LMR33630-Q1、LMR36015-Q1、LM61460-Q1、LMQ61460-Q1等直流/直流降壓轉換器的開關節點針腳在中間,並在兩側都有PGND和VIN針腳。這樣對稱設計產生的磁場有較好的圍阻,能降低與周圍電路的耦合。

整合輸入端電容

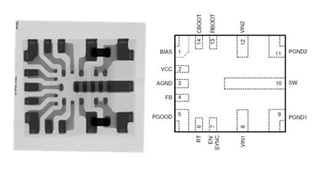

為了要使裝置層級的EMI降低,LMQ61460-Q1等產品將輸入端電容整合到封裝中。圖2a中的電容以深色長方形顯示,跨接右上與右下的VIN與PGND針腳對,可參考圖2b的針腳圖。將輸入端電容納入封裝可以減少寄生電感、振鈴、以及高頻EMI(同樣是因為滿足了第二個考量)。特別要注意高頻EMI 的影響,因為當輸入高電壓或輸出高電流的時候,高頻率造成的問題更大,而這兩個狀況在車用應用常常發生。

圖2:配置整合電容的LMQ61460-Q1X光圖(a);LMQ61460-Q1針腳圖(b)

EMI對於車用應用的確是一大挑戰,但電路板佈線限制並沒有斷絕所有生路,裝置層級的功能以及現代封裝方式,可以可靠且有效地壓低EMI,讓您在改良設計的同時,不用擔心EMI超標。

參考資料

- 欲了解封裝方式如何影響EMI,請參考培訓影片「使用HotRod降低EMI並縮小產品體積」

- 閱讀《類比設計期刊》的文章「透過降低寄生電感來減少降壓轉換器的EMI與電壓應力」

- 請參考應用報告「在車用降壓轉換器應用中減少EMI傳導」,以了解如何最佳化車用設計的EMI。