Application Report

SWRA550-May 2017

# IWR1xxx Radar Digital Front End (DFE)

Joe Quintal

#### **ABSTRACT**

The IWR family of radar processors have multiple transmitter and four receiver sections in each device. The radar processors utilize Frequency Modulated Continuous Wave (FMCW) processing. This application report provides a receiver simplified description and discusses the digital front-end processing.

#### Contents 1 2 **List of Figures** 1 2 3 4 5 Mhz Signal Bandwidth Example 6 List of Tables 1

#### **Trademarks**

ARM is a registered trademark of ARM Limited.

All other trademarks are the property of their respective owners.

## 1 Introduction

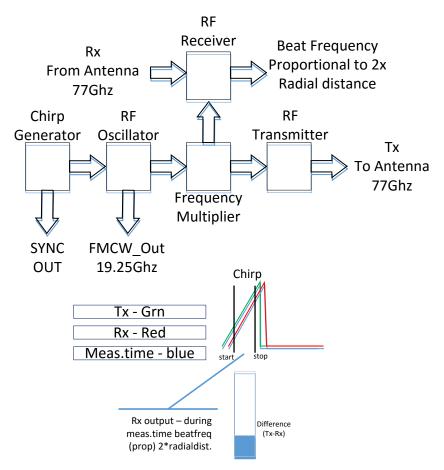

DFE is a portion of the IWR1xxx receiver architecture (see Figure 1). FMCW can be separated into a reference waveform generated by the chirp generator with the frequency multiplier, a transmitter that has RF power amplifiers and phase offset to generate the RF signal for the transmit antenna, and a receiver section that receives a signal from the receive antenna, amplifies it, provides a block down conversion, filtering, frequency translation, and further baseband processing.

The Tx reference waveform (chirp parameters), receiver configuration, the Analog-to-Digital Converter (ADC) sample rate, the receiver desired bandwidth, and the number of ADC samples are used to provide blocks of chirp Rx samples for baseband processing. If the receiver is operating in real sampling mode, the Inphase ADC and DFE are used. If the receiver is operating in quadrature mode, the Inphase ADC, Quadrature ADC, and DFE are used. After DFE, the output is further processed:

- In hardware accelerator and ARM® software (IWR1443), using internal calculations, the MSS ARM outputs the calculated data. In the IWR1443, the hardware accelerator output can be exported to an external DSP over the CSI-2 interface.

- In DSP and ARM software (IWR1642), using internal calculations, the MSS ARM outputs the calculated data.

Introduction www.ti.com

Figure 1. FMCW Radar Simplified Block Diagram

www.ti.com Introduction

## 1.1 DFE Operating Modes

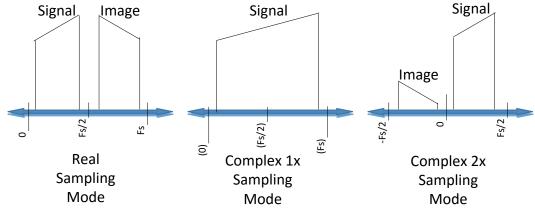

DFE can be operated in one of three modes; the DFE operates at 90% of the allowed Nyquist bandwidth for the selected mode (see Figure 2):

- Real Inphase only sampling, the first Nyquist zone is used for 0 fs to .45 fs, which requires further processing to reject the sample image and generally has an lower Signal-to-Noise Ratio (SNR).

- Complex 1x Quadrature sampling, special treatment of complex sample rate and tuned frequency;

the effect of this mode is to provide a 0.05 fs to .95 fs single sided signal.

- Complex 2x Quadrature sampling, the output –fs/2 to fs/2 range has a passband of -.45 fs to .45 fs.

Figure 2. Output Signal Representation With DFE Modes

## 1.2 DFE Example Configuration for Target BW

The distance calculated from the FMCW radar is based on the baseband Rx output frequency. The chirp parameters are used to provide resolution and distance. Delta frequency is used for other types of processing for velocity and angle; multiple receivers do further processing. The important parameter for the chirp profile is based on Chirp-to-Chirp sample period and additional parameters. Table 1 provides an illustration of the max frequency in each set of modes, the mmwave SDK has APIs to adjust these parameters.

provides specific configurations for the receiver operating mode and DFE parameters.

| IWR No. | ADC Mode   | DFE OP<br>Mode | BW-<br>maxbeatfr.<br>(.45*OutFs) | 1st Stage<br>Inrate | 1st Stage<br>Outrate | Special<br>Image<br>Suppression | 2nd Stage<br>Outrate | Notes      |

|---------|------------|----------------|----------------------------------|---------------------|----------------------|---------------------------------|----------------------|------------|

| 1443    | Full Cmplx | Cmp2x          | 8.4e6                            | 1800e6              | 100e6                | No                              | 18.75e6              | 7.5 Mhz BW |

| 1443    | Full Cmplx | Cmp1x          | 16.8e6                           | 1800e6              | 100e6                | Yes                             | 18.75e6              | 15 Mhz BW  |

| 1443    | Full Cmplx | Cmp1x          | 11.2e6                           | 1800e6              | 100e6                | Yes                             | 12.5e6               | 10 Mhz BW  |

| 1443    | Full Cmplx | Cmp1x          | 8.4e6                            | 1800e6              | 100e6                | Yes                             | 9.375e6              | 7.5 Mhz BW |

| 1443    | Low Cmplx  | Cmp1x          | 5.6e6                            | 900e6               | 50e6                 | Yes                             | 6.25e6               | 5 Mhz BW   |

| 1642    | Low Cmplx  | Cmp1x          | 5.6e6                            | 900e6               | 50e6                 | Yes                             | 6.25e6               | 5 Mhz BW   |

Table 1. Example ADC and DFE Sample Rates

Digital Front End (DFE) www.ti.com

## 2 Digital Front End (DFE)

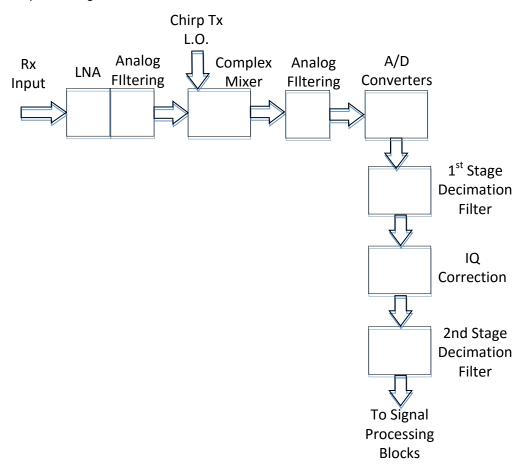

The direct down conversion receiver has several operating modes and selectable features to support signal processing. The main features are:

- Receiver Complex Down conversion Mixer the RF signal from the LNA is converted to a complex (Inphase and Quadrature)

- Receiver Analog filtering is applied to the downconverted mixer output

- Receiver Sigma Delta analog-to-digital conversion sample the down converted and Nyquist filtered RF signals. When complex sampling is used, there is an inphase and a quadrature ADC output. When real sampling is used, there is an Inphase ADC output.

- DFE First stage filtering and decimation the sampled RF signal is filtered and decimated

- DFE IQ bias and gain correction the output from the first stage filtering and decimation has DC removal; I and Q gain balancing is applied to reduce the IQ bias and gain imbalance if complex sampling is used.

- DFE Second stage filtering and decimation software controlled filtering, decimation, resampling, complex mixing are performed; the software APIs are used to set the mode and output sample rate for further processing.

Figure 3. FMCW Receiver Block Diagram

The DFE contains the three processing blocks shown in Figure 3:

- · First stage decimation filter

- IQ correction

- Second stage decimation filter, including image suppression filter

**TRUMENTS**

www.ti.com Digital Front End (DFE)

The mode (Real, Complex1x, Complex 2x), ADC sample rate, second stage decimation filter settings are controlled through the mmWave API, rlSetAdcOutConfig. The IQ correction is performed as part of the RSS calibration for each receiver channel.

## 2.1 DFE First Stage Decimation Filter

The Quadrature (I and Q) or real (I only) output of the A-D Converter is filtered and decimated. The multistage decimation filter, decimates by 18. The full ADC output of this filter section typically provides a 100 Msps output. The lower ADC output is 50 Msps output.

#### 2.2 DFE IQ Correction

The DFE IQ provides for calibration bias correction and calibration gain correction. The output of this section is monitored for calibration by the BSS/RSS subsystem. The bias removal and IQ gain correction is expected to provide >35 db image rejection ratio (IMRR). The IMRR is a ratio of the desired signal to its image.

## 2.3 DFE Second Stage Decimation Filter

The DFE second stage decimation filter combines a bank of 5 decimate by 2 filters, a fractional resampler, and final stage decimation filter. The overall second stage decimation and resampling convert the 100 Msps to the final quadrature or real only output. The filters in the 2nd stage decimation filter provide for 45% bandwidth (they are decimate by 2 filters) and have 60db stop band rejection. The resampler provides for fractional decimation ratios of 1 to 2.

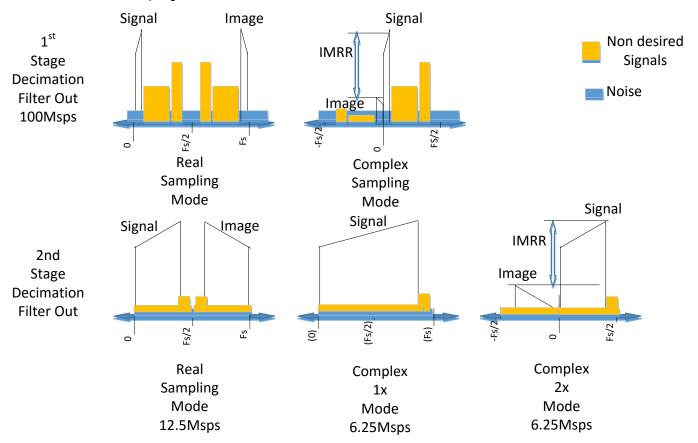

There are two operating modes of the DFE Second Stage Decimation Filter:

- · Normal low pass filter and decimation

- Image suppression

In the complex 2x or real mode, the low-pass digital filter and decimate by 2 stage are used.

In the complex 1x mode, the image suppression feature is used. This feature uses several blocks together: complex mixer, decimate by 2 low-pass filter, low-pass digital filter, complex mixer, and decimate by 2 stage.

Digital Front End (DFE) www.ti.com

In Figure 4 shows an example of a desired signal range of .1 MHz to 4.9 Mhz for further processing, using each of the sampling modes.

Figure 4. 5 Mhz Signal Bandwidth Example

The output of the second stage decimation filter goes to the ADC buffer in memory. The output data can be rounded and saturated for 12-, 14-, or 16-bit signed integer values. The data format is controlled by the rlGetAdcOutConfig mmWave API. The ADC output buffer is sent to the RSS/BSS calibration processing for gain, and IQ correction in the receiver. The ADC output buffer is sent to the CSI-2 external interface, or processed in the hardware accelerator (IWR1443) or DSP subsystem (IWR1642). A special output is possible for IWR1443 to send the hardware accelerator output over CSI-2.

#### IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated ('TI") technical, application or other design advice, services or information, including, but not limited to, reference designs and materials relating to evaluation modules, (collectively, "TI Resources") are intended to assist designers who are developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you (individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of this Notice.

TI's provision of TI Resources does not expand or otherwise alter TI's applicable published warranties or warranty disclaimers for TI products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections, enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications (and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1) anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED "AS IS" AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL, COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services. These include; without limitation, TI's standard terms for semiconductor products <a href="http://www.ti.com/sc/docs/stdterms.htm">http://www.ti.com/sc/docs/stdterms.htm</a>), evaluation modules, and samples (<a href="http://www.ti.com/sc/docs/sampterms.htm">http://www.ti.com/sc/docs/sampterms.htm</a>).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2017, Texas Instruments Incorporated