**Stephan Henzler**

## SPRINGER SERIES IN ADVANCED MICROELECTRONICS 29

# Time-to-Digital Converters

Springer Series in Advanced Microelectronics 29

The Springer Series in Advanced Microelectronics provides systematic information on all the topics relevant for the design, processing, and manufacturing of microelectronic devices. The books, each prepared by leading researchers or engineers in their fields, cover the basic and advanced aspects of topics such as wafer processing, materials, device design, device technologies, circuit design, VLSI implementation, and subsystem technology. The series forms a bridge between physics and engineering and the volumes will appeal to practicing engineers as well as research scientists.

Series Editors: Dr. Kiyoo Itoh Hitachi Ltd., Central Research Laboratory, 1-280 Higashi-Koigakubo Kokubunji-shi, Tokyo 185-8601, Japan

Professor Thomas Lee Department of Electrical Engineering, Stanford University, 420 Via Palou Mall, CIS-205 Stanford, CA 94305-4070, USA

Professor Takayasu Sakurai Center for Collaborative Research, University of Tokyo, 7-22-1 Roppongi Minato-ku, Tokyo 106-8558, Japan

Professor Willy M.C. Sansen ESAT-MICAS, Katholieke Universiteit Leuven, Kasteelpark Arenberg 10 3001 Leuven, Belgium

Professor Doris Schmitt-Landsiedel Lehrstuhl für Technische Elektronik, Technische Universität München Theresienstrasse 90, Gebäude N3, 80290 München, Germany

For other titles published in this series, go to http://www.springer.com/series/4076

Stephan Henzler

## Time-to-Digital Converters

Dr. Stephan Henzler TU München Lehrstuhl für Technische Elektronik Arcisstr. 21 80290 München Germany henzler@tum.de

ISSN 1437-0387 ISBN 978-90-481-8627-3 e-ISBN 978-90-481-8628-0 DOI 10.1007/978-90-481-8628-0 Springer Dordrecht Heidelberg London New York

Library of Congress Control Number: 2010921003

© Springer Science+Business Media B.V. 2010

No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

Cover design: eStudio Calamar S.L.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

Pour Julie

## Contents

| List | t of S | ymbols and Abbreviations                                    | ix |

|------|--------|-------------------------------------------------------------|----|

| 1    | For    | eword                                                       | 1  |

| 2    | Tim    | e-to-Digital Converter Basics                               | 5  |

|      | 2.1    | Motivation – The Way to the Time Domain                     | 5  |

|      | 2.2    | Analog Time-to-Digital Converters – The First Generation    | 8  |

|      | 2.3    | Fully Digital TDCs – The Second Generation                  | 12 |

|      | 2.4    | Basic Digital Delay-Line Based TDC                          | 13 |

|      |        | 2.4.1 Inverter Based Time-to-Digital Converter              | 15 |

|      | 2.5    | Synchronous Versus Asynchronous Time Interval Measurement   | 18 |

| 3    | The    | ory of TDC Operation                                        | 19 |

|      | 3.1    | Basic Performance Figures                                   | 19 |

|      | 3.2    | Quantization Error Revisited                                | 21 |

|      |        | 3.2.1 Linear Imperfections of TDC Characteristic            | 22 |

|      | 3.3    | Non-Linear Imperfections of TDC Characteristic              | 24 |

|      | 3.4    | Dynamic Performance and Effective Resolution                | 25 |

|      |        | 3.4.1 Basic ENOB Definition                                 | 27 |

|      | 3.5    | Timing Figures                                              | 31 |

|      | 3.6    | Noise Shaping in Time-to-Digital Converters                 | 31 |

|      | 3.7    | Process Variations in TDCs                                  | 34 |

|      |        | 3.7.1 Impact of Local Variations in Buffer Tree             | 36 |

|      |        | 3.7.2 Impact of Local Process Variations on Delay-Line      | 37 |

|      |        | 3.7.3 Impact of Local Process Variations on the Comparators | 39 |

|      |        | 3.7.4 Combined Impact of Local Variations on TDCs           | 40 |

| 4    | Adv    | anced TDC Design Issues                                     | 43 |

|      | 4.1    | Bipolar Time-to-Digital Converter                           |    |

|      | 4.2    | Looped Time-to-Digital Converter                            |    |

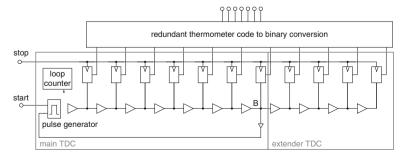

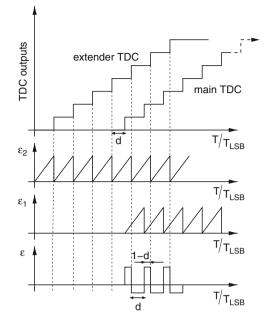

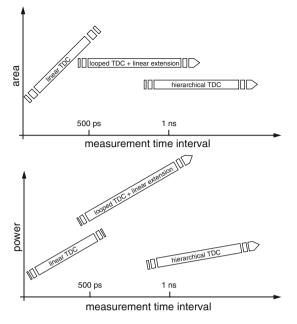

|     | 4.3   | Linearly Extended TDC Loop                                    | 49 |

|-----|-------|---------------------------------------------------------------|----|

|     |       | 4.3.1 Operation and Calibration of Linearly Extended TDC      | 50 |

|     | 4.4   |                                                               | 53 |

|     | 4.5   |                                                               | 55 |

|     | 4.6   |                                                               | 59 |

|     | 4.7   |                                                               | 63 |

|     | 4.8   |                                                               | 65 |

|     | 4.9   |                                                               | 67 |

| 5   |       | e-to-Digital Converters with Sub-Gatedelay                    |    |

|     | Rese  | olution – The Third Generation                                | 69 |

|     | 5.1   | Sub-Gate Delay Resolution                                     | 69 |

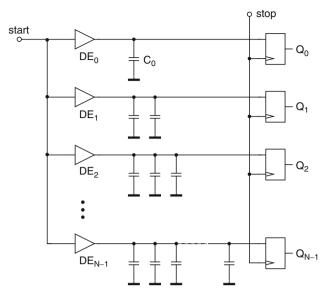

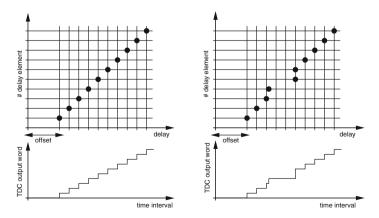

|     | 5.2   | Parallel Scaled Delay Elements                                | 70 |

|     |       | 5.2.1 Variability in TDC Based on Parallel Scaled             |    |

|     |       | Delay Elements                                                | 72 |

|     | 5.3   |                                                               | 74 |

|     |       | 5.3.1 Vernier TDC in Loop Configuration                       | 76 |

|     |       | 5.3.2 Variability in Vernier TDC                              | 78 |

|     | 5.4   | Pulse-Shrinking TDC                                           | 80 |

|     |       | 5.4.1 Pulse-Shrinking TDC in Loop Configuration               | 83 |

|     |       | 5.4.2 Variability in Pulse-Shrinking TDC                      | 84 |

|     | 5.5   | Local Passive Interpolation TDC                               | 86 |

|     |       | 5.5.1 LPI-TDC in Loop Configuration                           | 89 |

|     |       |                                                               | 89 |

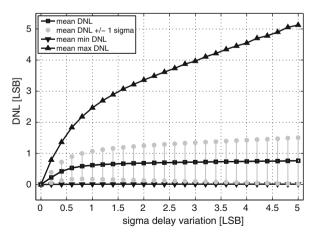

|     |       | 5.5.3 Variability in LPI-TDC                                  | 92 |

|     |       |                                                               | 94 |

|     | 5.6   |                                                               | 96 |

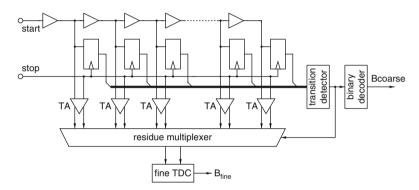

|     | 5.7   | Time-to-Digital Converter with Time Amplification             | 98 |

| 6   | Арр   | blications for Time-to-Digital Converters 1                   |    |

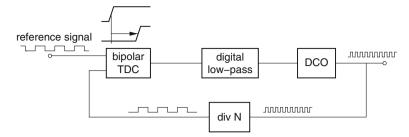

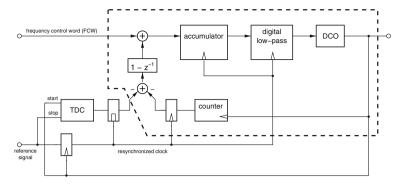

|     | 6.1   | Digital Phase Locked Loop1                                    |    |

|     | 6.2   | TDC Based Analog-to-Digital Converter 1                       | 07 |

|     |       | 6.2.1 Dual-Slope Analog-to-Digital Converter Revisited1       |    |

|     |       | 6.2.2 Pulse Position Modulation Analog-to-Digital Converter 1 | 09 |

|     |       | 6.2.3 Sigma Delta Modulator with Time Domain Quantizer 1      | 11 |

| Ref | erenc | ces                                                           | 15 |

| Ind | ex    |                                                               | 19 |

## List of Symbols and Abbreviations

| $A_{core}^{TDC-type}$ | Core area of a TDC                                                     |

|-----------------------|------------------------------------------------------------------------|

| ACF                   | Auto-correlation function                                              |

| ADC                   | Analog-to-digital converter                                            |

| ASDM                  | Asynchronous sigma delta modulator                                     |

| BIST                  | Built-in self test                                                     |

| CML                   | Current mode logic                                                     |

| CMOS                  | Complementary metal oxide semiconductor                                |

| DAC                   | Digital-to-analog converter                                            |

| DL                    | Delay-line                                                             |

| DL-TDC                | Delay-line TDC                                                         |

| DLL                   | Delay-locked loop                                                      |

| DNL                   | Differential non-linearity                                             |

| DR                    | Dynamic range                                                          |

| DTC                   | Digital-to-time converter                                              |

| $E_{gain}$            | TDC gain error                                                         |

| ELD                   | Early-late detector                                                    |

| $E_{offset}$          | TDC offset error                                                       |

| ENOB                  | Effective number of bits                                               |

| $f_{clk}$             | Clock frequency                                                        |

| FCW                   | Frequency control word                                                 |

| FET                   | Field effect transistor                                                |

| FOM                   | Figure of merit                                                        |

| FF                    | Flip-flop                                                              |

| GRO                   | Gated ring oscillator                                                  |

| INL                   | Integral non-linearity                                                 |

| $k_{TDC}$             | TDC gain                                                               |

| $k_{TDC}^{core}$      | TDC core gain                                                          |

| kincremental<br>TDC   | Incremental TDC gain                                                   |

| L                     | Transistor channel length                                              |

| LC                    | Describes a resonator based on an inductance (L) and a capacitance (C) |

| LDO                   | Linear drop out (regulator)                                            |

|                       |                                                                        |

| LE                         | Loop footor                                              |

|----------------------------|----------------------------------------------------------|

| LF                         | Loop factor                                              |

| LO                         | Local oscillator                                         |

| LPI                        | Local passive interpolation                              |

| LPV                        | Local process variations                                 |

| LSB                        | Least significant bit                                    |

| MOS                        | Metal oxide semiconductor                                |

| MS                         | Mixed-signal                                             |

| MSB                        | Most significant bit                                     |

| OPAMP                      | Operational amplifier                                    |

| OSR                        | Oversampling ratio                                       |

| $P_{core}^{TDC-type}$      | Core power consumption of a TDC                          |

| PD                         | Phase detector                                           |

| PFD                        | Phase-frequency detector                                 |

| pdf                        | Probability density function                             |

| PLL                        | Phase-locked-loop                                        |

| PPM                        | Pulse position modulation                                |

| PVT                        | Process, voltage, and temperature (variations)           |

| PWM                        | Pulse width modulation                                   |

| RDC                        | Resolution degradation coefficient                       |

| RF                         | Radio frequency                                          |

| rms                        | Root-mean-square                                         |

| RN                         | Asynchronous reset signal low-active                     |

| SCE                        | Short channel effects                                    |

| SDM                        | Sigma delta modulator                                    |

| SNDR                       | Signal-to-noise-and-distortion ratio                     |

| SNR                        | Signal-to-noise ratio                                    |

| SOC                        | System-on-chip                                           |

| SQNR                       | Signal-to-quantization-noise ratio                       |

| SSP                        | Single-shot precision                                    |

| STA                        | Static timing analysis                                   |

| std(.)                     | Standard deviation                                       |

| Т                          | Absolute temperature in Kelvin                           |

| ТА                         | Time (interval) amplifier                                |

| T <sub>conv</sub>          | Conversion time of TDC                                   |

| $T_{dead}$                 | Dead time, i.e. minimum time between two measurements    |

| <i>T<sub>latency</sub></i> | Latency of TDC                                           |

| $T_{LSB}$                  | Minimum time increment that can be resolved by a TDC     |

| $T_{max}$                  | Maximum time interval that can be measured               |

| $T_{min}$                  | Minimum time interval that can be measured               |

| $t_d$                      | Delay of logic gate or circuit                           |

| TDC                        | Time-to-digital converter                                |

| VCO                        | Voltage controlled oscillator                            |

| $V_{DD}$                   | Positive supply potential of digital circuit             |

| $V_{LSB}$                  | Minimum voltage increment that can be resolved by an ADC |

| $V_{SS}$                   | Negative supply potential of digital circuit             |

|                            |                                                          |

| $V_T = \frac{kT}{q}$ | Thermal voltage                                     |

|----------------------|-----------------------------------------------------|

| $V_{th}$             | Threshold voltage                                   |

| $V^0_{th}$           | Threshold voltage for $V_{DS} = 0$ and $V_{BS} = 0$ |

| $V_{tn}$             | NMOS threshold voltage                              |

| $V_{tp}$             | PMOS threshold voltage                              |

| VLSI                 | Very large scale integration                        |

| W                    | Transistor channel width                            |

|                      |                                                     |

## Chapter 1 Foreword

Micro-electronics and so integrated circuit design are heavily driven by technology scaling. The main engine of scaling is an increased system performance at reduced manufacturing cost (per system). In most systems digital circuits dominate with respect to die area and functional complexity. Digital building blocks take full advantage of reduced device geometries in terms of area, power per functionality, and switching speed. On the other hand, analog circuits rely not on the fast transition speed between a few discrete states but fairly on the actual shape of the transistor characteristic. Technology scaling continuously degrades these characteristics with respect to analog performance parameters like output resistance or intrinsic gain. Below the 100 nm technology node the design of analog and mixed-signal circuits becomes perceptibly more difficult. This is particularly true for low supply voltages near to 1 V or below. The result is not only an increased design effort but also a growing power consumption. The area shrinks considerably less than predicted by the digital scaling factor. Obviously, both effects are contradictory to the original goal of scaling. However, digital circuits become faster, smaller, and less power hungry. The fast switching transitions reduce the susceptibility to noise, e.g. flicker noise in the transistors. There are also a few drawbacks like the generation of power supply noise or the lack of power supply rejection. Still, the advantages are overwhelming and suggest to implement as much system components as possible in the digital domain. As digital functionality nearly comes for free it usually makes no sense to optimize single gates or to elimination a few logic functions. In most cases the effort for these optimizations does not pay off. If however analog or mixed-signal performance can be increased by digital assist or enhancement techniques the effort should be spent. If digital circuit add-ons help to reduce analog power or improve robustness and reliability, the investment in these add-ons should be done. In the deep sub-micron regime a few thousand gates are not worth to be discussed. Very often the introduction of digital assist techniques or even all digital implementations cause a one time area and power overhead. The increased performance and new functionality should justify this expense. Moreover, the overhead will shrink in future technology generations so the full advantage of the increased performance and the robustness will pay off one or two generations later.

It is obvious that there are functions that can be done best with analog circuits. Hence, the message should not be to avoid analog circuits at all but to use digital techniques whenever they promise an advantage. The effort is justified very often.

By definition digital circuits (binary circuits to be more precise) cannot resolve any information in the amplitude domain. Instead they have a very high resolution in the time domain. The very first approach of trading voltage (current) resolution against time resolution is the sigma delta modulator: A coarse quantizer causes a considerable quantization error that is antagonized by oversampling with noise shaping. For high resolution at high bandwidths the quantizer often has more than two quantization levels so not the complete information is covered in the time domain. A generalization of this time domain concept encodes any information of the signal into the time domain. This can be done by providing time domain information at equidistant time instances: A pulse width modulated signal, for instance, consists of pulses that occur with a fixed rate and that contain the information within the width of the pulses. An asynchronous approach has not even a fixed sample rate but provides non-equidistant pulses. In this case both the sample information as well as the sampling instance is implicitly encoded by two time instances. Timeto-digital converters are highly precise stopwatches that convert time domain information into a digital representation. Hence, they represent the fundamental building blocks between the continuous time domain of time encoded data and the digital world. In principle TDCs only consist of sampled delay-lines. The challenges arise when continuous measurement, long time intervals, high resolution, linearity, low power consumption, and robustness come into the play. The architectures addressing one or more of these issues rapidly become more complex. This is the reason for this text on time-to-digital converters which is organized as follows: First an introduction to time domain signal processing is given in Chapter 2. The basic concepts of time-to-digital converters (TDC) are introduced and basic structures are discussed. Chapter 3 addresses the theory of TDCs. Performance figures are defined and compared to corresponding features of analog-to-digital converters. Noise and variability are discussed in detail. Their impact on the single-shot precision, the effective number of bits and the linearity is derived. Next, various TDC architectures for high dynamic range, linearity, bipolar measurement, matching, and low power consumption are discussed in Chapter 4. Many of these architectural concepts are based on research work by the author and are proposed and presented in this text for the very first time. High resolution below one gate delay is discussed in Chapter 5. Finally, representative TDC applications in the field of phase locked loops and analog-to-digital converters are discussed in Chapter 6.

The criterion for the selection of the material and for the focus of the text has been the advantage of the digital processing of time domain signals. The reason for this is the following: Time domain signal processing and so time-to-digital converters are proposed for high volume micro-electronics in order to circumvent analog impairments in nanometer-scale CMOS technologies. Hence, only TDC concepts are promising that have the ability to exploit the advantages of digital circuits. Timeto-digital converters that are based on sensitive analog approaches cannot take a real advantage of the time domain. If only such TDCs were available it would be instructive to stay with the old analog/mixed-signal concepts that are based on the voltage domain but are architecturally mature, sophisticated, and proven for many years. A time domain signal representation, however, makes sense when the main building blocks are based on digital concepts. Anyhow, it is to be understood that time-to-digital converters are no digital circuits in the sense of synthesizeable semicustom circuits. Yet some design automation is possible, but the careful knowledge and handling of the sensitive (continuous time) signals inside the TDC requires analog expert knowledge. This means that a TDC can exploit some advantages of digital circuits but still behaves like a mixed-signal circuit. Not least because of the fact that it processes continuous time signals.

With this book I want to give an overview and substantiated impression on timeto-digital converters. It is shown that the main challenges are not only the high time resolution but often lie in the architectures that focus on other performance figures such as high dynamic range and linearity. I have tried to motivate that time-to-digital converters have the potential to become a trend-setting technology for ultimately scaled CMOS technologies. TDCs are much more than delay-lines and can be used for many more applications than for simple phase detectors. I am confident that this new class of circuits, namely continuous time continuous time circuits, will take up an important role in upcoming RF and mixed-signal applications, especially in nanometer scale technologies. Perhaps they will even find a role in the world of integrated systems that will emerge after the transistor era.

The new concepts and investigations presented in this book mainly originate from my research work at Infineon Technologies AG during the last years. I highly appreciate that I got the great opportunity to work in this interesting field and for the permission to use unpublished material on time-to-digital converters in this book for the first time. I also want to thank Dominik Lorenz for his valuable contributions during his master thesis and his outstanding commitment during the start up phase of our TDC projects. Many thanks go to Professor Ulf Schlichtmann and Professor Yannos Manoli who take so much time in reviewing my research work and advising me in many situations. My deep gratefulness goes to my mentor Professor Doris Schmitt-Landsiedel, head of the Institute for Technical Electronics, Technische Universität München. She always encourages me to open my mind to new challenges, concepts, and ideas. Without this mindset I would not have the drive to excel the limits of current structures and concepts. I am very proud of having the possibility to teach together with her in the micro-electronics track of Technische Universität München where I try to teach not only technical stuff but also the fun of innovation.

Munich November 2009 Stephan Henzler

### Chapter 2 Time-to-Digital Converter Basics

**Abstract** On the basis of a generic mixed-signal system the scaling difficulties of analog and mixed-signal circuits based on a signal representation in the voltage domain are discussed for nanometer CMOS technologies. Therewith, the advantages of a signal representation in the time domain are emphasized. The primary approach to time-to-digital converters (analog TDCs) based on a two step approach translating the time interval into a voltage and this voltage into a digital value is explained. Analog impairments and resolution limitations are examined. Counter based time interval measurement and delay-line based TDCs (digital TDCs) are introduced and analyzed with respect to operating principle, basic implementation issues, and quantization error, i.e. resolution.

**Key words:** Basic Time-to-Digital Converter, Analog TDC, Digital Delay-Line TDC, Mixed-Signal Systems

#### 2.1 Motivation – The Way to the Time Domain

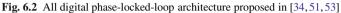

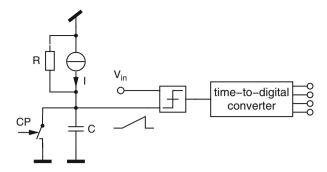

Time-to-digital converters (TDC) – certainly most engineers link this expression with all-digital phase-locked loops (PLL) where a TDC serves as phase detector [34, 51–53]. Interestingly, TDCs have been used for more than 20 years in the field of particle and high-energy physics, where precise time-interval measurement is required [27, 28, 32, 54]. Other applications cover time-of-flight measurement, or measurement and instrumentation applications such as digital scopes and logic analyzers. Currently the micro-electronics community rediscovers time-to-digital converters and this is the justification for a complete book on this topic. While the all digital PLL is the first and most famous TDC application others emerge rapidly. TDC based analog-to-digital converter for instance shows that TDCs are not just phase detectors but useful in a much wider field [8, 48]. Of course the requirements for any micro-electronics application differ from the applications mentioned above with respect to acceptable price, reproducibility, and suitability for mass production. These issues will be discussed in detail throughout the book. At this point

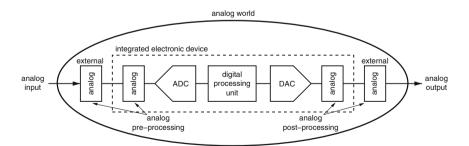

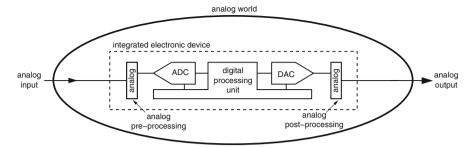

the motivating question shall be discussed why TDCs suddenly become popular in mainstream micro-electronics: Modern VLSI technology is mainly driven by digital circuits. The reasons for this are the many advantages of digital compared to analog circuits: Atomic digital functions can be realized by very small and simple circuits. This results in a compact and cheap implementation of elementary logic functions and enables complex and flexible signal processing systems. A comparable complexity was not feasible with an analog implementation due to area and power consumption but also due to variability and signal integrity. Flexible means reconfigurable, adjustable or even programmable. Data can be stored easily in digital systems without any loss of information. The design of digital circuits is highly automated resulting in high design efficiency and productivity. However, the main advantage of digital signal processing is the inherent robustness of digital signals against any disturbances, i.e. noise and coupling, as well as the inherent robustness of digital circuits against process variations. Both signal integrity and variability in digital circuits are heavily discussed in technical literature during the last years. It is true that these are critical issues especially for large chips fabricated in ultra deep sub-micron technologies. But compared to analog realizations digital solutions are still by far more robust. As a consequence of all these advantages most digital signal processing systems are realized according to the generic structure depicted in Fig. 2.1. A small mixed-signal shell provides the interface between the digital core and the environment which is always analog.<sup>1</sup> While the mixed-signal interface is mainly responsible for the data conversion, the actual signal processing task is performed in the digital domain. In the input path some basic analog signal conditioning, e.g. coarse filters, amplifiers and mixers are followed by a sampler and a quantizer, i.e. an ADC. The sampler evaluates the input signal at discrete time instances and the quantizer maps the resulting continuous values to discrete ones. Both together result in a digital signal representation. In the output path the digital values provided by the signal processing core at discrete time instances are converted in voltages/currents and held constant until the next value occurs. An optional analog low pass filter removes the (sinc-filtered) mirror spectra and provides smooth output signals.

Fig. 2.1 Generic digital signal processing system comprising a digital core embedded in a mixedsignal shell for interfacing with the analog environment

<sup>&</sup>lt;sup>1</sup> In fact even interfaces with digital functionality are analog. Digital signal transmission over highspeed serial links for instance poses lots of analog challenges, which become obvious on the lower abstraction levels.

But what has all of this to do with time-to-digital converters? What is the problem with this generic structure that has been successfully used for so many years? The difficulties arise from technology scaling in the ultra deep sub-micron regime: With each technology generation the intrinsic gain of a single MOS transistor namely the  $\frac{g_m}{g_{ds}}$  decreases. This does not only result from parasitic short channel effects but is a fundamental result from MOS physics.<sup>2</sup>

In principle there are classical countermeasures to cope with decreasing transistor gain. Cascode transistors, for instance, increase the output resistance of basic amplifiers, current mirrors, and active loads dramatically, but cause at least one  $V_{Dsat}$  in the DC voltage budget. With the reduced supply voltages of scaled technologies there is often not enough voltage headroom to use cascodes. But even though this is possible, the speed of the circuit and the signal swing is reduced. The latter effect is particularly disadvantageous because of the reduced signal-to-noise ratio (SNR). In general technology scaling comes with a reduction in supply voltage and so reduced signal levels. As noise does not scale the SNR in the voltage domain is reduced in proportion to  $V_{DD}^2$ .

Altogether, the design of classical mixed-signal circuits becomes increasingly difficult. This rises two questions: First we have to check whether the mixed-signal content of modern signal processing systems is really reduced to a minimum. Second we have to answer why classical mixed-signal systems have that bad scaling behavior. In many systems mixed-signal circuits are just used for interfacing, so the first question can be approved. However, digital enhancement techniques within the mixed-signal building blocks, e.g. calibration techniques can help to improve the performance considerably. This means that the mixed-signal content of the generic system in Fig. 2.1 is minimized, but that the mixed-signal blocks themselves could be flavored with additional digital enhancement techniques.

The second question can be answered by considering the strengths of technology scaling. Although the main benefit of scaling in the deep sub-micron regime is the area reduction, there is still a speed improvement. This effect becomes smaller especially in low-power technologies, but continues to push digital performance. Despite increasing leakage currents [13] the power also scales to some extend. Good scaling behavior is thus achieved for all systems that take advantage of the fast digital switching speed. The reduction of the gate delay results in continuously improving temporal resolution which is contrary to the amplitude resolution [53]. Therewith, there is no principal restriction of mixed-signals blocks in aggressively scaled technologies but the problem is the signal representation in the voltage domain. An implementation of the same functionality in the time-domain would immediately take advantage of technology scaling again. The enabler for the time-domain processing of continuous signals is the time-to-digital converter. With this key building block a transformation of classical mixed-signal systems with a signal representation in the voltage domain is possible. This final rush for digitalization has just started.

<sup>&</sup>lt;sup>2</sup> The channel length modulation coefficient  $\lambda = \frac{1}{V_E L}$  is inverse proportional to the channel length *L* and the Early voltage  $V_E$ . The channel length scales considerably faster than  $V_E$  so the dependence of the drain current on the drain-to-source voltage increases with technology scaling [50].

**Fig. 2.2** Future digital signal processing system where the mixed-signal shell is heavily flavored with digital enhancement techniques that help to cope with the impairments of analog circuits in the deep sub-micron CMOS technologies

During the next years the amount of classical mixed-signal circuitry will be further reduced. The remaining mixed-signal components will be heavily supported by digital enhancement techniques and digital post-processing of imperfect data (ref. Fig. 2.2). Non-idealities due to analog impairments will be corrected by digital signal processing. For sure this is no digitalization in a VHDL or Verilog sense but a conversion of the continuous voltage domain into the continuous time domain. A substantiated expert knowledge in transistor level circuit design will still be the essential basis to cope with the increasing challenges in deep sub-micron CMOS technologies.

#### 2.2 Analog Time-to-Digital Converters – The First Generation

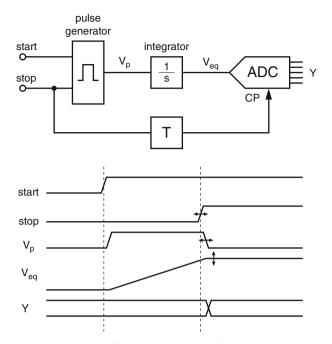

The traditional approach to time-to-digital conversion is first to convert the time interval into a voltage. In a second step this voltage is digitized by a conventional analog-to-digital converter (ADC). A basic block diagram is given in Fig. 2.3. The start and the stop event are used to form a pulse with a width corresponding to the time interval to be measured. An analog integrator transforms this pulse into a voltage which is then fed to the ADC. A fundamental trade-off between the dynamic range *DR*, i.e. the maximum time interval to be measured and the maximum number of bits *N* the ADC can accomplish is revealed by the following equation:

$$DR = 2^N \cdot T_{LSB} \tag{2.1}$$

The minimum time interval that can be resolved is given by  $T_{LSB}$ . As the maximum resolution of the ADC is limited by analog constraints, a long measurement interval means low resolution and vice versa. A high resolution measurement of long time intervals requires a two stage approach, i.e. a coarse quantization of the long time interval and a fine quantization of the remainder. Another approach is to integrate up and down periodically. The number of periods gives a coarse quantization and the

Fig. 2.3 Block and signal diagram of basic analog time-to-digital converter, e.g. [32, 42]

analog voltage level can be converted by the ADC to achieve a high resolution. We will see later in this book that the limitation given by eq. 2.1 does not exist for digital TDCs which is a great advantage over ADCs. There are also multi-stage approaches for digital TDCs (ref. Section 4.5) but the motivation behind this is the reduction of area and power.

Although the conversion principle in Fig. 2.3 is quite simple there are several analog issues that degrade the TDC performance: All building blocks, i.e. the pulse generator, the integrator, and the ADC have to meet the full linearity demands of the overall TDC. A basic integrator implementation that allows for high-speed, i.e. short measurement intervals, is a current source which is connected to an integration capacitance during the measurement interval. Due to the finite output resistance of the current source the linearity is weak. To overcome this problem an active RC-integrator may be used. As the potential at the virtual ground is nearly constant the linearity is improved. However, the finite bandwidth of the operational amplifier (opamp) limits the speed and so the minimum time interval considerably.

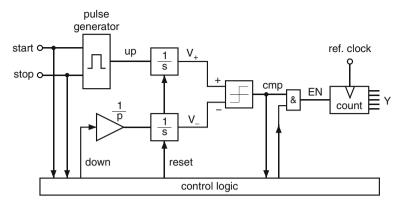

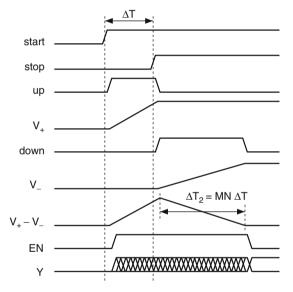

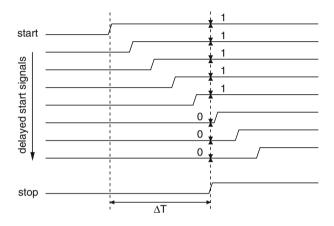

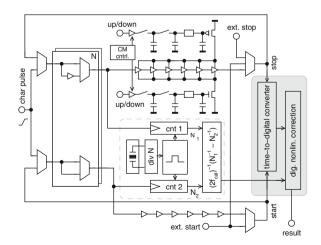

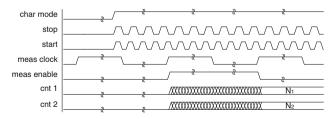

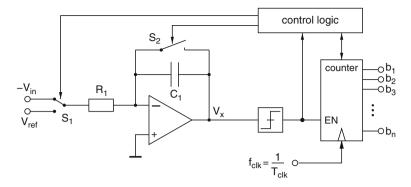

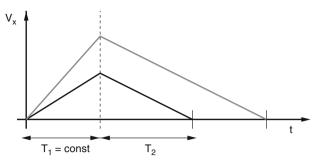

Absolute time measurement requires the knowledge of the current and the capacitance value. For integrated TDC implementations this is not feasible without calibration. A more elaborate TDC approach which does not require the knowledge of absolute device values is shown in Fig. 2.4. An exemplary signal diagram is given in Fig. 2.5. Again the pulse defined by the start and the stop signals is integrated. On the arrival of the stop signal a second integrator starts integrating but with a

Fig. 2.4 Blockdiagram of analog TDC based on dual-slope analog-to-time-interpolation [43]

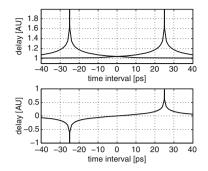

Fig. 2.5 Basic signal diagram of analog time-to-digital converter based on dual-slope analog-totime interpolation. By means of pulse stretching the initial time interval  $\Delta T$  is converted into a digital representation

reduced integration constant  $\frac{1}{p}$ . A comparator detects when the output of the second integrator is equal to the first one. This happens  $(1+p)\Delta T$  seconds after the start event. The initial time interval  $\Delta T$  is stretched by the factor (1+p). Therefore this dual-slope approach is also known as time amplification. If p is large enough the enlarged time interval may be quantized by a simple digital counter.

In principle the dual-slope TDC is a reversed dual-slope analog-to-digital converter. In a dual-slope ADC an unknown analog signal is integrated for a well defined time. In the dual-slope TDC a well defined voltage namely the pulse height is

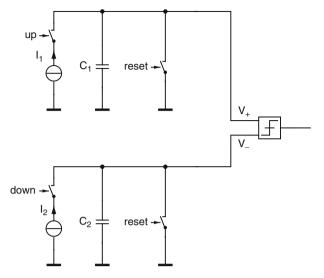

Fig. 2.6 Schematic circuit diagram of a basic dual-slope TDC [43]

integrated for the unknown time interval  $\Delta T$ . In both cases the output voltage of the integrator after the first phase is integrated down by a predefined rate until a reference level is reached and a basic counter measures the required time. A major advantage of the dual-slope with respect to the basic single-slope ADC is the fact that absolute device values cancel out. The same should hold for the dual-slope TDC: To demonstrate this, the implementation in Fig. 2.6 is considered. At the beginning both capacitances  $C_1$  and  $C_2$  are discharged by the reset devices. During the time interval  $\Delta T$  a first current source is connected to  $C_1$ . Assuming a perfect current source, the voltage  $V_+$  increases linearly and reaches a final value given by  $V_+ = \frac{I_1}{C_1}\Delta T$ . On the arrival of the stop signal  $C_1$  becomes floating and  $C_2$  is connected to a second current source  $I_2$ . The voltage  $V_-$  across  $C_2$  is given by  $V_- = \frac{I_2}{C_2}\Delta T_2$  where  $\Delta T_2$  is the time elapsed since the stop event has occurred. The comparator connected to both capacitors detects when the two voltages  $V_+$  and  $V_-$  are equal. This happens a time interval

$$\Delta T + \Delta T_2 = \left(1 + \frac{C_2}{C_1} \frac{I_1}{I_2}\right) \Delta T \tag{2.2}$$

after the start event. With a capacitance ratio  $M := \frac{C_2}{C_1}$  and a current ratio  $N^{-1} = \frac{I_2}{I_1}$  the initial time interval is stretched (amplified) by a factor  $(1 + M \cdot N)$ . As both factors M and N are ratios of physical quantities namely capacitances and currents the absolute values are not relevant. This makes the dual-slope approach very robust against process variations and enables an integration without the need for calibration. The fact that both ratios are multiplied is also advantageous for integration as large stretching factors can be realized even without unreasonably large capacitance or current ratios.

#### 2.3 Fully Digital TDCs – The Second Generation

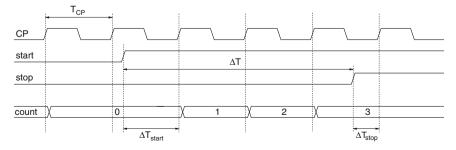

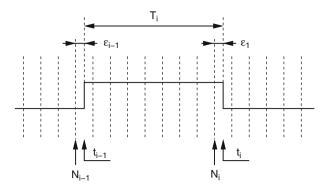

If the motivation for a TDC was just to implement a precise timer, an analog approach like one of those discussed in the previous section would be enough. However, the strategy to provide TDCs as generic mixed-signal building blocks for various applications rises questions about the suitability in ultimately scaled CMOS technologies. In Section 2.1 the advantages of time domain signal processing and the superior scaling properties of TDCs have been emphasized. Obviously this does not hold for any analog TDC which converts time domain information first into the analog and then to the digital domain. Such TDCs consist mainly of an ADC so have all the impairments of analog circuits in deep sub-micron technologies. The advantages of the time domain can be exploited only if there is no analog conversion step in the time-to-digital conversion. Only if the TDC is clearly dominated by digital circuitry the scaling and robustness arguments hold. Therefore, digital conversion techniques are investigated in the remainder of this book: The simplest technique to quantize a time interval is to count the cycles of a reference clock fitting into the respective measurement interval. As shown in Fig. 2.7 the measurement interval defined by the start and stop signal is completely asynchronous to the reference clock signal. This causes a measurement error  $\Delta T_{start}$  at the beginning and  $\Delta T_{stop}$  at the end of the time interval. The measurement interval  $\Delta T$  can be expressed as

$$\Delta T = N \cdot T_{CP} + (T_{CP} - \Delta T_{stop}) - (T_{CP} - \Delta T_{start})$$

=  $N \cdot T_{CP} - \Delta T_{stop} + \Delta T_{start}$

=  $N \cdot T_{CP} + \varepsilon_T$  (2.3)

$$\Delta T_{start} \in [0; T_{CP}]$$

$$\Delta T_{stop} \in [0; T_{CP}]$$

$$\varepsilon_T = \Delta T_{start} - \Delta T_{stop} \in [-T_{CP}; T_{CP}]$$

(2.4)

where *N* is the counter value and  $T_{CP}$  the reference clock period.  $\Delta T_{start}$  and  $\Delta T_{stop}$  are the time intervals between the start and the stop signal, respectively, and the next rising edge of the clock signal. The quantization error of the  $\Delta T$  measurement is between  $-T_{CP}$  and  $+T_{CP}$ , i.e. is limited to twice the period of the clock signal.

Fig. 2.7 Principle of counter based TDC

The measurement accuracy can be increased by a higher clock frequency. However, the higher the clock frequency the higher the power consumption for the generation and the processing of the clock signal. Above a certain clock frequency (corresponding to 3–4 FO2 inverter delays<sup>3</sup>) CMOS based oscillators are not available anymore, so even more expensive CML or LC oscillators are required for the clock generation. Timing restrictions in the counter as well as in the controller circuit pose another limit on the maximum frequency. In a 65 nm technology for instance the maximum frequency is limited to 5–10 GHz, i.e. a maximum measurement accuracy of  $2 \cdot 100-200$  ps may be achieved.

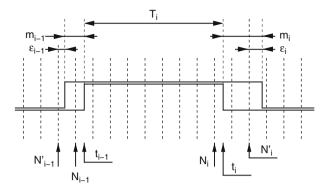

An even higher resolution is achieved by subdividing one clock period asynchronously into smaller time intervals. The engine that performs this subdivision is actually what we call a digital time-to-digital converter. Hence, the resolution is the criterion that distinguishes a counter from a TDC. The measurement interval quantized with a TDC can be described by

$$\Delta T = NT_{CP} - (T_{CP} - \Delta T_{start}) + (T_{CP} - \Delta T_{stop})$$

(2.5)

$$\Delta T_{start} = N_1 \frac{T_{CP}}{k} - \varepsilon_1 \tag{2.6}$$

$$\Delta T_{stop} = N_2 \frac{T_{CP}}{k} - \varepsilon_2 \qquad \varepsilon_1, \varepsilon_2 \in \left[0; T_{LSB} = \frac{T_{CP}}{k}\right]$$

(2.7)

$$\Delta T = NT_{CP} + N_1 \frac{T_{CP}}{k} - \varepsilon_1 - N_2 \frac{T_{CP}}{k} + \varepsilon_2$$

(2.8)

$$\varepsilon_T = \varepsilon_2 - \varepsilon_1 \in \left[ -\frac{T_{CP}}{k}; \frac{T_{CP}}{k} \right]$$

(2.9)

where the resolution  $T_{LSB} = \frac{T_{CP}}{k}$  is increased by the factor *k*. The interpolation factor *k* describes in how many sub-intervals the reference clock cycle is partitioned,  $N_1$  and  $N_2$  indicate the position of the start and the stop event within such a reference clock cycle. The subsequent chapters describe the basic concepts of digital time-to-digital converters and explain how a higher resolution can be achieved even without a higher reference clock frequency.

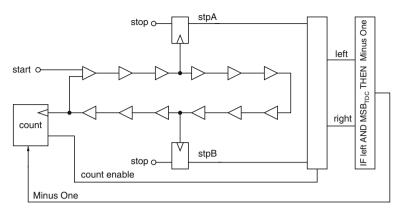

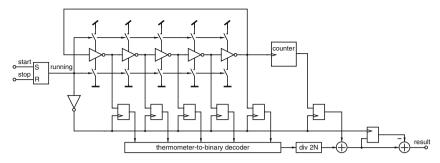

#### 2.4 Basic Digital Delay-Line Based TDC

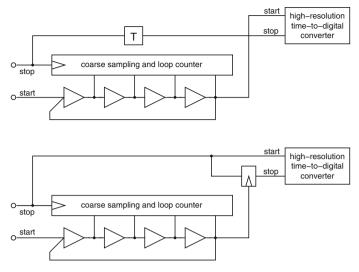

To increase the measurement resolution beyond the maximum feasible clock frequency each counter clock cycle has to be sub-divided asynchronously by a time-todigital converter. Figure 2.8 illustrates that the counter value then provides a coarse quantization of the measurement interval and the TDC a fine sub-quantization [37]. The subdivision of the reference clock interval, also known as reference clock

<sup>&</sup>lt;sup>3</sup> FO2 refers to the fan-out of two inverter delay, i.e. to the delay of an inverter that is loaded with twice its input capacitance.

Fig. 2.8 Principle of a counter based TDC where the resolution is increased by subdividing one clock interval asynchronously into smaller time intervals [37]

**Fig. 2.9** Operating principle of a time-to-digital converter. Delayed versions of the start signal are sampled on the rising edge of the stop signal, resulting in a thermometer code at the outputs of the sampling elements (flip-flops or comparators)

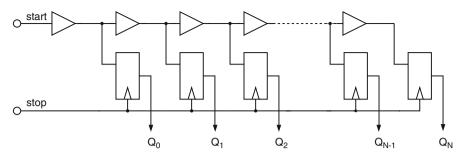

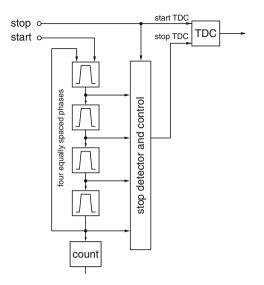

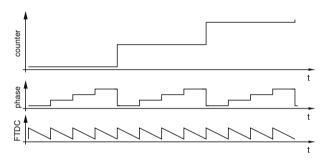

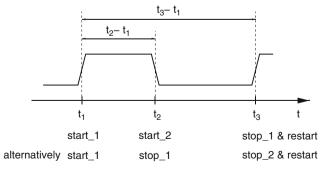

interpolation, is done by using multiple phases of the reference clock. For a small interpolation factor, i.e. medium resolution, the phases may be directly derived from the oscillator which generates the reference clock. A ring oscillator consisting of kdelay stages for instance generates k equally spaced versions of the clock signal. An even higher resolution is achieved by delaying the original reference clock in a chain of digital delay elements. The resolution then depends on the delay of the delay elements in the chain. Figure 2.9 illustrates the operating principle of a TDC based on a digital delay-line. The reference clock which is in a more general sense an arbitrary start signal is delayed along the delay-line. On the arrival of the stop signal the delayed versions  $start_i$  of the start signal are sampled in parallel. Either latches or flip-flops can be used as sampling elements. The sampling process freezes the state of the delay-line at the instance where the stop signal occurs. This results in a thermometer code because all delay stages which have been already passed by the start signal give a HIGH value at the outputs of the sampling elements, all delay stages which have not been passed by the start signal yet give a LOW value. The position of the HIGH-LOW transition in this thermometer code indicates how far the start signal could propagate during the time interval spanned by the start and the stop signal. Hence this transition is a measure for the time interval. The number N

Fig. 2.10 Implementation of a basic delay-line based time-to-digital converter (DL-TDC)

of all sampling elements with a HIGH output is related to the measurement interval  $\Delta T$  according to

$$N = \left\lfloor \frac{\Delta T}{T_{LSB}} \right\rfloor \tag{2.10}$$

where  $T_{LSB}$  is the delay of a single delay element in the delay-line. The time interval  $\Delta T$  can be calculated from the number of HIGH outputs by

$$\Delta T = NT_{LSB} + \varepsilon \tag{2.11}$$

where  $\varepsilon$  describes the quantization error that arises as a delay element has been either passed by the start signal yet or not. Any intermediate state is not possible. The quantizer characteristic of a TDC and its non-idealities are discussed in Chapter 3 extensively.

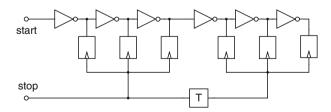

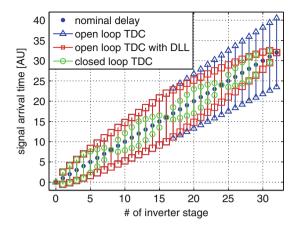

An implementation of the basic delay-line TDC is shown in Fig. 2.10. The start signal ripples along a buffer chain that produces the delayed signals  $\text{start}_i$ . Flip-flops are connected to the outputs of the delay elements and sample the state of the delay-line on the rising edge of the stop signal. The stop signal drives a high number of flip-flops so a buffer-tree (not shown) is required. Any skew in this buffer-tree directly contributes to the non-linearity of the TDC characteristics. For a correct thermometer code the skew between adjacent branches in this tree has to be smaller than  $T_{LSB}$  which makes the design challenging.

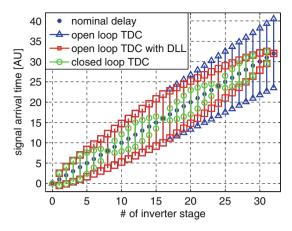

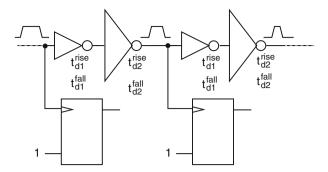

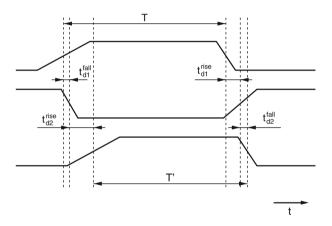

#### 2.4.1 Inverter Based Time-to-Digital Converter

The resolution of the delay-line based TDC discussed in the previous section is limited by the delay of the buffers. The resolution can be doubled by replacing the buffers by CMOS inverters. This, however, rises some implementation challenges which will be discussed next: The use of inverters means that both the rising and the falling signal transitions are used for measurement. Hence the thermometer code at the outputs of the sampling elements becomes a pseudo thermometer code with alternating ones and zeros:

| 111111111111111 _ 00000000000000000 | buffer TDC   |

|-------------------------------------|--------------|

| 010101010101010 _ 010101010101010   | inverter TDC |

The length of the measurement interval is indicated not by a HIGH-LOW transition but by a phase change of the alternation HIGH-LOW sequence.

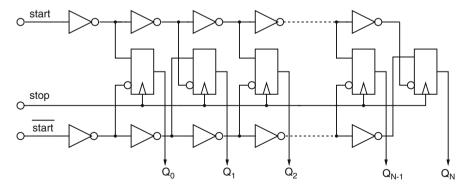

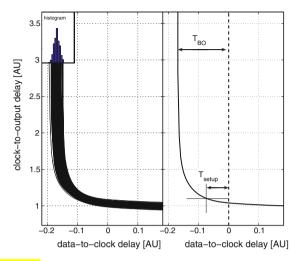

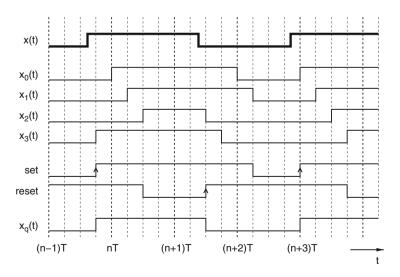

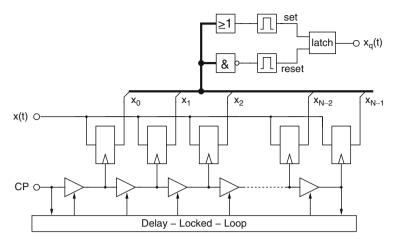

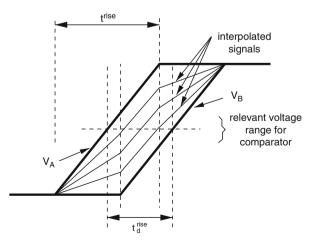

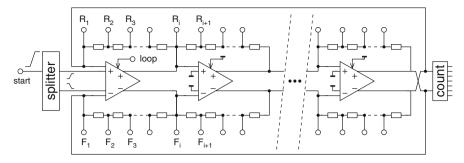

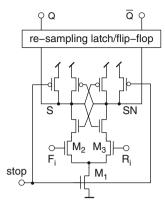

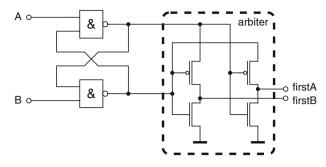

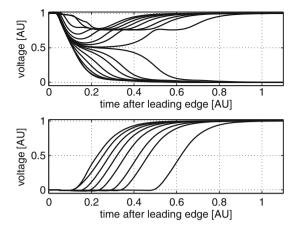

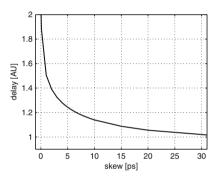

In principle the delays for a rising and a falling transition of a CMOS inverter are different and only partially correlated. There is some correlation due to common process steps during manufacturing of NMOS and PMOS devices. Examples for such process steps are the formation of the gate oxide and the gate lithography. However, there are also completely independent process steps such as the ion implantation for threshold voltage adjustment. This leads to systematic non-linearity of the converter characteristic. For nominal process conditions the rise and the fall delay can be made equal but any process variation imbalances the delays again. An even stronger effect has the asymmetric setup time of basic sampling elements such as master slave latch pairs. Hence, a high-resolution TDC based on a single inverter delay chain seems to be not feasible if process variations become significant. Figure 2.11 shows a robust inverter based TDC. Fully symmetrical differential flipflops such as sense amplifier based flip-flops are used as sampling elements. Two delay chains propagate the start as well as the inverted start signal and provide differential data to the flip-flops. The inverting characteristics of the CMOS inverters is compensated by twisting the input signals of the flip-flops in each second stage. This compensates completely for the potential asymmetric setup time of the flipflops and asymmetric rise and fall delays of the inverters. Local process variations may cause a faster signal propagation in one delay-line compared to the other. Coupling elements such as cross coupled inverter pairs in between two corresponding

Fig. 2.11 Time-to-digital converter based on inverters instead of buffers. The resolution is doubled with respect to the implementation given in Fig. 2.10

|                                                    | Deffer Delese Line TDC                                                                                                        | Less to Dalars Line TDC                                                                                                                                                                              |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>D</b> ! ! !                                     | Buffer Delay-Line TDC                                                                                                         | Inverter Delay-Line TDC                                                                                                                                                                              |

| Principle                                          |                                                                                                                               | Differential start signal propa-                                                                                                                                                                     |

|                                                    |                                                                                                                               | gates in two coupled chains of in-                                                                                                                                                                   |

|                                                    |                                                                                                                               | verters. On the arrival of a stop                                                                                                                                                                    |

|                                                    |                                                                                                                               | signal the state of the delay-line                                                                                                                                                                   |

|                                                    | flops/comparators                                                                                                             | is sampled by (differential) flip-                                                                                                                                                                   |

|                                                    |                                                                                                                               | flops/comparators                                                                                                                                                                                    |

| Resolution $T_{LSB}$                               | $t_d^{buffer} = 2t_d^{inv}$                                                                                                   | $t_d^{inv}$                                                                                                                                                                                          |

| Number of Stages N                                 | $\frac{T_{max}}{T_{LSB}} = \frac{T_{max}}{t_d^{buffer}} = \frac{T_{max}}{2t_d^{mv}}$                                          | $\frac{T_{max}}{T_{LSB}} = \frac{T_{max}}{t_d^{lmv}}$                                                                                                                                                |

| Core Area A <sup>Vernier</sup> <sub>core</sub>     | $\frac{T_{max}}{T_{LSB}} \left( 2A^{inv} + A^{FF} \right)$                                                                    | $\frac{T_{max}}{T_{LSB}} \left( 2.2 A^{inv} + A^{FF} \right)$                                                                                                                                        |

| Average Power $\langle P_{vernier}^{core} \rangle$ | $f_{meas} \frac{T_{max}}{T_{LSB}} \left( 2E_{rise}^{inv} + 2E_{fall}^{inv} + E^{FF} \right)$                                  | $f_{meas} \frac{T_{max}}{T_{LSB}} \left( 2.2 E_{rise}^{inv} + 2.2 E_{fall}^{inv} + E^{FF} \right)$<br>The factor 2.2 accounts for the overhead required to couple the two delay-lines (differential) |

| Conversion Time <i>T<sub>conv</sub></i>            | Т                                                                                                                             | Т                                                                                                                                                                                                    |

| Latency T <sub>latency</sub>                       | 0                                                                                                                             | 0                                                                                                                                                                                                    |

| Loop Structure                                     | loop possible                                                                                                                 | loop possible                                                                                                                                                                                        |

| PROS                                               | <ul> <li>Simple</li> <li>Fully digital</li> <li>Low power</li> <li>Low latency</li> <li>Easy control and embedding</li> </ul> | <ul><li>Same as for buffer TDC</li><li>Doubled resolution</li></ul>                                                                                                                                  |

| CONS                                               | <ul><li>Low resolution</li><li>Resolution limited by technology</li></ul>                                                     | <ul> <li>Alignment of delay-lines</li> <li>Resolution limited by technology</li> <li>Doubled number of comparators for same dynamic range</li> </ul>                                                 |

**Table 2.1** Performance summary of buffer and inverter delay-line TDC. The performance figures are introduced in the following chapter. However, for comparability with the results presented in Chapter 4 this table is already presented here

delay elements reduces this drifting of the signals. However, there is still a very regular and symmetrical layout required for the two delay-lines. This is probably the most challenging task for an actual TDC implementation (Table 2.1).

#### 2.5 Synchronous Versus Asynchronous Time Interval Measurement

Synchronous time interval measurement based on a coarse pre-quantization by a reference clock and a fine quantization with a TDC (ref. Fig. 2.8) has the fundamental drawback that the reference clock jitter deteriorates the measurement accuracy. This can be seen by rewriting eqs. 2.5–2.8 with a jitter term:

$$\Delta T = NT_{CP} - (T_{CP} - \Delta T_{start}) + (T_{CP} - \Delta T_{stop})$$

(2.12)

$$\Delta T_{start} = N_1 \frac{T_{CP}}{k} - \varepsilon_1 + t_{jitter,1}$$

(2.13)

$$\Delta T_{stop} = N_2 \frac{T_{CP}}{k} - \varepsilon_2 + t_{jitter,2} \qquad \varepsilon_1, \varepsilon_2 \in \left[0; T_{LSB} = \frac{T_{CP}}{k}\right]$$

(2.14)

$$\Delta T = NT_{CP} + N_1 \frac{T_{CP}}{k} - \varepsilon_1 + t_{jitter,1} - N_2 \frac{T_{CP}}{k} + \varepsilon_2 - t_{jitter,2}$$

(2.15)

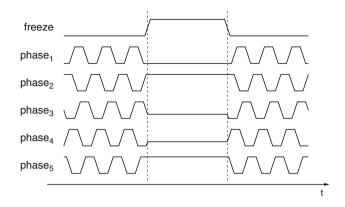

The jitter is a mean free not necessarily gaussian random variable characterized by its rms value  $\sigma_{jitter}$ . It can be seen that two partly independent jitter contributions add to the measurement uncertainty statistically. For short and medium time intervals it may be advantageous to abdicate the reference clock and to use a longer TDC. Therewith the measurement error caused from reference clock jitter vanishes. The start and stop signals for the TDC are directly extracted from the measurement pulse and not referred to any clock (asynchronous time interval measurement). The TDC has to be able to measure the complete time interval not just a reference clock period, i.e. the delay chain has to be long enough or an advanced TDC architecture like the looped TDC (ref. Section 4.2) has to be used. Of course there is also noise in the TDC which translates into a deviation of the switching instances of the delay elements from the ideal time instances and a variation of the sampling instance. The resulting measurement uncertainty increases with  $\sqrt{T}$  where T is the length of the measurement interval. Hence for long measurement intervals the intrinsic timing uncertainty of the TDC may be larger than the reference clock jitter. For an actual design and a required measurement time the intrinsic TDC noise and the quality of a possible reference clock generator must be compared. Thereupon it can be decided whether a synchronous or asynchronous approach is preferable. Beside the noise the availability of the clock signal is another criterion as an additional clock PLL contributes considerably to the overall power consumption and die area.

## Chapter 3 Theory of TDC Operation

**Abstract** This chapter addresses theoretical aspects of time-to-digital converters. First the basic shape of a TDC input–output characteristic is explained. The quantization error that arises from the mapping of a continuous into a discrete signal domain is revisited. Linear and non-linear imperfections of a TDC, namely offset and gain error as well as differential and integral non-linearities, are explained. Dynamic performance figures are motivated on the basis of analog-to-digital converters. The difference between ADC and TDC measurement is discussed. The interrelation between the single tone experiment of ADCs and the single shot experiment for TDCs is derived. An effective number of bits is defined for TDCs based on a single shot measurement. Therewith, an ADC compliant figure of merit is defined for TDCs. Local (process) variations are a critical issue for high resolution time-to-digital converters. The susceptibility of each of these components is analyzed individually. Finally, the particular variation effects are combined.

**Key words:** TDC Characteristic, TDC Offset Error, TDC Gain Error, TDC Non-Linearity, Single-Shot-Precision, TDC Effective Number of Bits, TDC Process Variations

#### 3.1 Basic Performance Figures

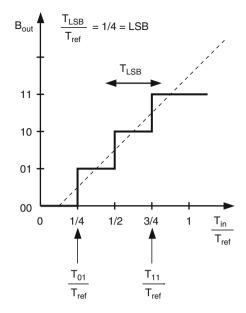

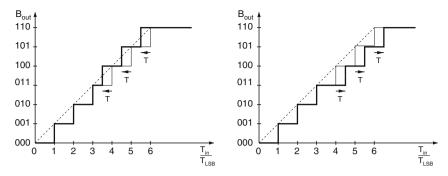

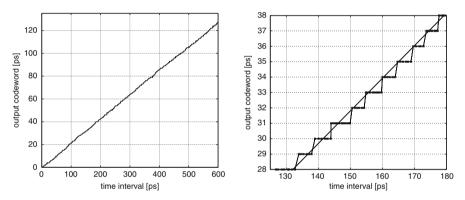

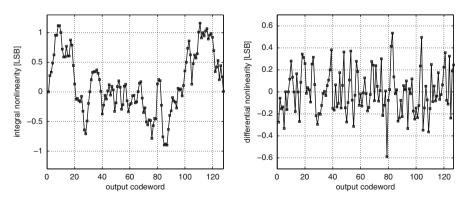

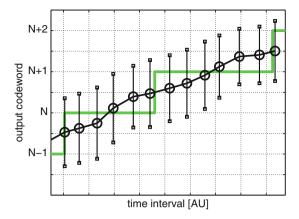

The static input–output behavior of a TDC is given by a quantizer characteristic such as that depicted in Fig. 3.1. The input time interval to be measured is plotted on the *x*-axis and the corresponding digital output word is represented by the *y*-axis. The term quantizer characteristic means that continuous time intervals at the TDC input are mapped to discrete output values. Consequently, there is a range of time intervals that is mapped to the same output value. The (ideal)<sup>1</sup> width of this time

<sup>&</sup>lt;sup>1</sup> In actual TDC designs the step width varies from step to step. This non-linearity is described later in this chapter. A more precise definition for  $T_{LSB}$  will be given in eq. 3.4.

Fig. 3.1 Ideal input-output characteristic of time-to-digital converter

interval is the absolute resolution  $T_{LSB}$  and the corresponding output increment is called 1 *LSB*. The time-to-digital conversion is not invertible and the input–output behavior

$$T_{in} = B_{out} T_{LSB} + \varepsilon \qquad 0 \le \varepsilon < T_{LSB} \tag{3.1}$$

can be described only by means of the so called quantization error  $\varepsilon$ . In the ideal case the unknown quantization error behaves like an equally distributed, uncorrelated random signal and contributes only to the noise floor of the measurement. This is only true, however, if the input signal changes fast enough and strong enough so that the quantization error appears to be de-correlated from the signal. For periodic operation, this is not the case and the quantization error which is actually not noise but deterministically dependent on the signal gives rise to harmonic distortion.

The time intervals where the steps occur are labeled by  $T_B$  where B is the quantization level after the step, i.e.  $T_{0...01}$  indicates the position of the very first and  $B_{1...11}$ of the last step. These step positions will be used throughout this chapter to define the various non-idealities such as offset, gain error, or non-linearity.

In principle, a TDC characteristic is identical with the characteristic of an analogto-digital converter (ADC), except the fact that a continuous time and not a continuous voltage is measured. In ADCs, this voltage is referred to a reference voltage. The reference voltage  $V_{ref}$  is the voltage against which the input voltage is compared and indicates usually the maximum input level that can be measured without saturation effects. Usually the reference voltage is externally provided and the ADC derives the quantization voltage  $V_{LSB}$  from this reference voltage according to

$$V_{LSB} = \frac{V_{ref}}{2^N} \tag{3.2}$$

where *N* is the number of bits. In a TDC, however, not a reference time interval  $T_{ref}$  but a quantization time  $T_{LSB}$  is given. A corresponding reference time can be defined by

$$T_{ref} = 2^N \cdot T_{LSB} \tag{3.3}$$

The problem with this definition is the fact that, theoretically, a TDC can measure an arbitrarily long time interval. In the looped TDC that is discussed in Section 4.2, for instance, the timing event to be measured circulates in the TDC delay-line and a loop counter determines the number of full loop cycles. The number of bits in eq. 3.3 then depends on the number of bits in the loop counter and the reference time  $T_{ref}$  has no useful meaning. Yet, the loop structure means that the converter characteristic is constructed periodically by the characteristic of a single loop cycle. The time increment corresponding to this periodicity is then a much better definition for the reference time. The number of bits corresponding to this reference time is called the core resolution<sup>2</sup>  $N_c$ , whereas the overall resolution is named N. With this  $T_{ref}$  definition the definition of the quantization time interval according to

$$T_{LSB} = \frac{T_{ref}}{2^{N_c}} \tag{3.4}$$

makes sense again. It is important to understand that the resolution according to this formula is the ideal resolution, i.e. the best value that can be achieved with the underlying converter architecture. In reality impairments such as non-linearity and noise degrade the effective resolution that is actually measured. This will be discussed after the introduction of the various imperfections.

A further difference compared to ADCs is the fact that the steps in a TDC characteristic usually occur at the end of a quantization interval whereas for ADC characteristic the steps often lie in the middle of an interval. This is a minor difference that changes the definition of the TDC performance figures slightly.

#### **3.2 Quantization Error Revisited**

Converting a continuous into a discrete signal results in a quantization error  $\varepsilon$  according to eq. 3.1. In contrast to ADCs where the quantization error is usually symmetrical around zero, i.e.  $-\frac{1}{2}V_{LSB} \le \varepsilon < \frac{1}{2}V_{LSB}$ , the quantization error of a TDC is not mean free ( $0 \le \varepsilon < T_{LSB}$ ). An equally distributed quantization error has the mean value

$$\langle \boldsymbol{\varepsilon} \rangle = \frac{1}{T_{LSB}} \int_0^{T_{LSB}} \boldsymbol{\varepsilon} d\boldsymbol{\varepsilon} = \frac{1}{2} T_{LSB}$$

(3.5)

The quantization noise power

$$\langle \varepsilon^2 \rangle = \frac{1}{T_{LSB}} \int_0^{T_{LSB}} \varepsilon^2 d\varepsilon = \frac{1}{3} T_{LSB}^2$$

(3.6)

<sup>&</sup>lt;sup>2</sup> In a controlled TDC the reference time according to this definition corresponds usually to the time reference  $T_R$  of the control loop (ref. Section 4.4).

can be separated into a constant and a mean free variable component according to

$$\boldsymbol{\varepsilon} = \langle \boldsymbol{\varepsilon} \rangle + \boldsymbol{\eta} \tag{3.7}$$

$$\langle \varepsilon^2 \rangle = \langle \varepsilon \rangle^2 + \langle \eta^2 \rangle$$

(3.8)

with

$$\left\langle \boldsymbol{\varepsilon} \right\rangle^2 = \frac{1}{4} T_{LSB}^2 \tag{3.9}$$

$$\left\langle \eta^2 \right\rangle = \frac{1}{12} T_{LSB}^2 \tag{3.10}$$

In the frequency domain the constant component  $\langle \varepsilon \rangle$  yields a DC spectral line. The variable component  $\eta$  results in spectral power with f > 0. This component of the quantization error is often assumed as white, i.e. its power spectral density is flat. This is justified for non-periodic signals that change sufficiently fast. If this condition is fulfilled, the power spectral density can be described by

$$psd\left(\varepsilon\right) = \frac{1}{4}T_{LSB}^{2}\delta(f) + \frac{T_{LSB}^{2}}{12f_{s}}\left[\sigma\left(f + \frac{f_{s}}{2}\right) - \sigma\left(f - \frac{f_{s}}{2}\right)\right]$$

(3.11)

For a sinusoidal signal  $x(t) = A \sin(2\pi f t)$  with  $2^{M-1}$  quantization steps for the signal amplitude<sup>3</sup> the ideal signal-to-(quantization)-noise ratio (S(Q)NR) is given by

$$SNR = 6.02 \, \mathrm{dB} \cdot M + 1.76 \, \mathrm{dB}$$

(3.12)

The DC component of the quantization error has been neglected. As for the ADC each additional bit in the amplitude domain increases the signal-to-noise ratio by 6.02 dB. This is the ideal signal-to-noise ratio as only the quantization but no physical noise is considered. The actual SNR is always lower than this theoretical value.

#### 3.2.1 Linear Imperfections of TDC Characteristic

In an ideal TDC the first step occurs at the position  $T_{00...01} = T_{LSB}$ . If this step and so the complete converter characteristic is shifted along the time axis, the converter is said to have an offset error  $E_{offset}$ , defined by

$$E_{offset} = \frac{T_{00...01} - T_{LSB}}{T_{LSB}}$$

(3.13)

i.e., the offset error (ref. Fig. 3.2) is the deviation of the first step position from its ideal value  $T_{LSB}$  in terms of  $T_{LSB}$ . This is not necessarily the same as the output

<sup>&</sup>lt;sup>3</sup> This definition sounds a little bit artificial. However, unlike the input voltage of ADCs the maximum input time interval of TDCs is not limited so the reference to a sinusoidal input signal with maximum amplitude is not possible.

Fig. 3.2 Input-output characteristic of a TDC with offset error

value  $B_{out}(T = 0)$  that is measured for a zero time interval. The reason for a mismatch between these two figures is a potential non-linearity as discussed in the next section. In contrast to an ADC, the input time interval is not bound in principle, so the definition of the TDC gain is somehow ambiguous. Generally, the gain  $k_{TDC}$  of a TDC is the steepness of the input–output characteristic, or mathematically,

$$k_{TDC} = \frac{\Delta B}{\Delta T} \tag{3.14}$$

Depending on the definition of the deltas, several gain definitions are possible: Using the whole converter characteristic yields the overall gain  $k_{TDC}$  of the TDC. In looped TDCs, i.e. for converter characteristics with a periodicity, it makes sense to refer to this periodicity and to call the respective gain the core gain  $k_{TDC}^{core}$ . Differences of these two gain definitions arise if the periodic parts do not fit together perfectly. If non-linearity is noticeable it makes sense to define the gain as the slope of a regression line. This is possible for both gain definitions given above. If only a small fraction of the TDC characteristic is used during operation, an incremental gain definition  $k_{TDC}^{incr}$  around an operating point is suited best. It depends on the application which gain definition is the most appropriate one. An ideal TDC has a gain of

$$k_{TDC} = \frac{1}{T_{LSB}} \tag{3.15}$$

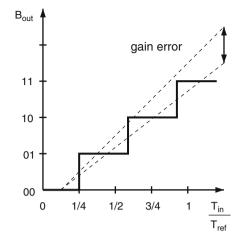

i.e. a  $T_{LSB}$  increment of the input time interval reflects in an output increment of one LSB. Any variation of the gain may be quantified by the gain error  $E_{gain}$ , which is the deviation of the last step position from its ideal value in terms of LSB after the offset error has been removed (ref. Fig. 3.3):

$$E_{gain} = \frac{1}{T_{LSB}} \left( T_{11\dots 11} - T_{00\dots 01} \right) - \left( 2^N - 2 \right)$$

(3.16)

Fig. 3.3 Input-output characteristic of a TDC with gain error

Again, similar definitions may be used if only a certain part of the converter characteristic is of interest. The actual TDC gain can be expressed in terms of the gain error according to

$$k_{TDC} = \frac{2^N - 2}{(2^N - 2)T_{LSB} + E_{gain}T_{LSB}} \approx \frac{1}{T_{LSB}} \left(1 - \frac{E_{gain}}{2^N - 2}\right)$$

(3.17)

Finally, it shall be mentioned that the offset and the gain error are so called linear imperfections as they can be modeled by an additive or multiplicative term to the input time interval, respectively, so do not cause non-linear distortion.<sup>4</sup>

#### 3.3 Non-Linear Imperfections of TDC Characteristic

Non-linear imperfections are all deviations of a TDC characteristic from its expected shape that lead to non-linear distortion. The integral non-linearity (INL) is a macroscopic description of the bending of a converter characteristic. It is defined as the deviation of the step position from its ideal value normalized to one  $T_{LSB}$ . The ideal value is defined by a straight line that can be either a line connecting the first and the last step or a best fit line. The former is a pragmatic approach, whereas the latter causes a little bit more computation effort but yields better insight especially for converters with the main non-linearity at the beginning and/or the end of the characteristic. The INL is defined for each step. However, sometimes a single number is given as INL value. This is then the maximum or root-mean-square (rms)

<sup>&</sup>lt;sup>4</sup> Quantization is always a very non-linear operation. In this context, the term linear means that the output is linearly dependent on the input when the quantization error is neglected.

value over all steps. The differential non-linearity (DNL) describes the deviation of each step from its ideal value, namely  $T_{LSB}$ , so gives a more microscopic view on the non-linearity. Both the INL and the DNL are usually normalized to one  $T_{LSB}$ .

The terms 'integral' and 'differential' may suggest that the INL is obtained by summing up the DNL. However, if the  $T_{LSB}$  is the quantization time interval of the ideal converter, the DNL contains both gain and non-linearity error. This can be easily seen by considering a case where each step has a width of let's say  $0.5 \cdot T_{LSB}$ . The error with respect to a reference line is zero, i.e. there is no integral non-linearity, but the slope of this line differs by a factor of two from the ideal characteristic.

#### **3.4 Dynamic Performance and Effective Resolution**

The performance figures discussed so far result from so called static measurements. This means usually that the measurements are done slowly, without active peripheral circuits. For converter characteristics multiple measurements are averaged. This averaging means that any noise (physical noise, power supply noise, substrate noise) and any dynamic coupling effects are removed from the measurement results. In real operation where any single measurement counts and where many measurements are done subsequently noise cannot be neglected and reduces the effective resolution. In this section dynamic performance figures of conventional analog-to-digital converters are explained, transferred to time-to-digital converters, and compared.

The classic dynamic measurement of ADCs is the stimulation with a sinusoidal signal and the evaluation of the output spectrum. Therefore, output data is stored for multiple cycles of the input signal and transferred into the frequency domain via Fourier transformation. The resulting spectrum is a so called single tone spectrum. It contains a peak at the signal frequency, smaller peaks at multiples of the signal frequency are called harmonics. The noise floor describes power components at all other frequencies. It results from both quantization as well as physical noise. The signal-to-noise ratio is defined as the ratio between the power of the fundamental over the total noise power. Usually it is given in dB, i.e.

$$SNR = 10 \text{ dB} \cdot lg\left(\frac{P_{signal}}{P_{noise}}\right)$$

(3.18)

The harmonic components are neglected during the calculation of the noise power. The signal-to-noise-and-distortion ratio (*SNDR*) defined by

$$SNDR = 10 \text{ dB} \cdot lg\left(\frac{P_{signal}}{P_{noise} + P_{harmonics}}\right)$$

(3.19)

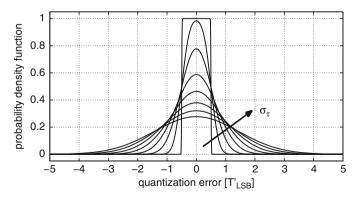

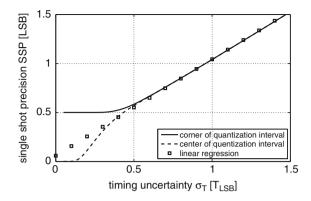

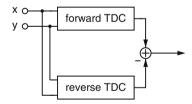

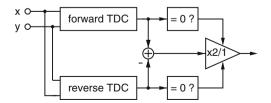

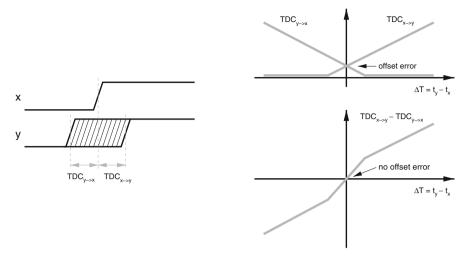

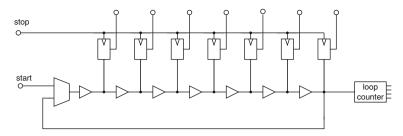

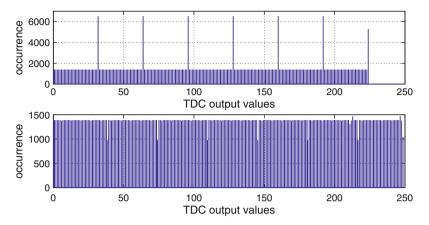

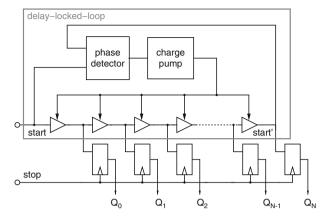

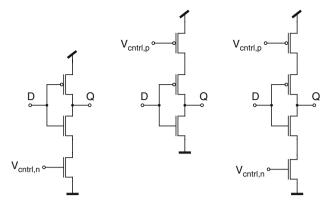

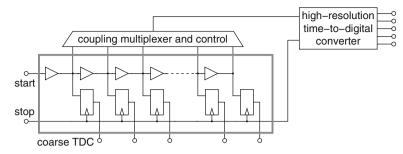

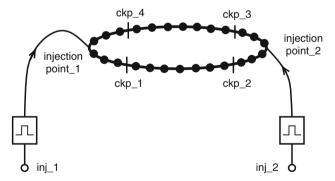

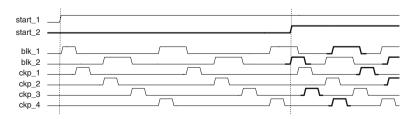

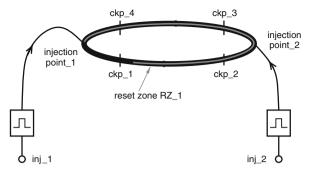

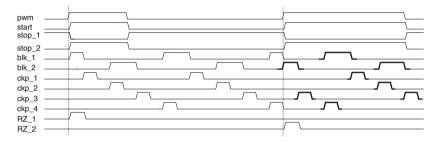

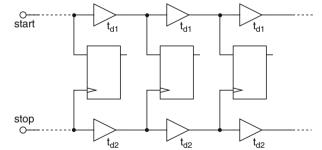

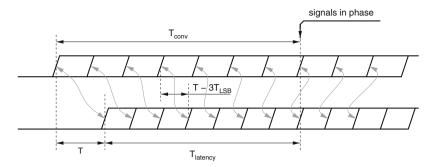

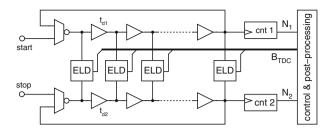

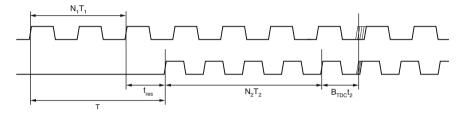

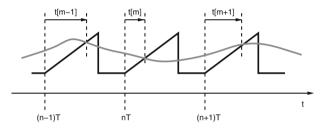

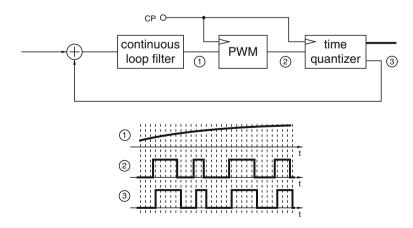

takes also the harmonics into account. Thus, the *SNDR* is always smaller than the *SNR*. Obviously, *SNR* and *SNDR* are functions of the signal amplitude. This dependence is usually demonstrated by a diagram where the signal amplitude is plotted