# TSM12

# 12-Channel Self Calibration Capacitive Touch Sensor

# SPECIFICATION V1.0

# **1** Specification

#### 1.1 General Feature

- 12-Channel capacitive sensor with auto sensitivity calibration

- Selectable output operation (single mode / multi-mode)

- Independently adjustable in 8 step sensitivity

- Sync function for multi chip application

- Touch intensity can be detectable within 3 steps (Low, Middle and High)

- Adjustable internal frequency with external resister

- Adjustable response time and interrupt level by the control registers

- I2C serial interface

- Embedded high frequency noise elimination circuit

- IDLE mode to save the consumption

- Embedded power key function on channel 1 for mobile phone application

- RoHS compliant 32QFN package

## 1.2 Application

- Mobile application (mobile phone / PDA / PMP etc)

- Membrane switch replacement

- Sealed control panels, keypads

- Door key-lock matrix application

- Touch screen replacement application

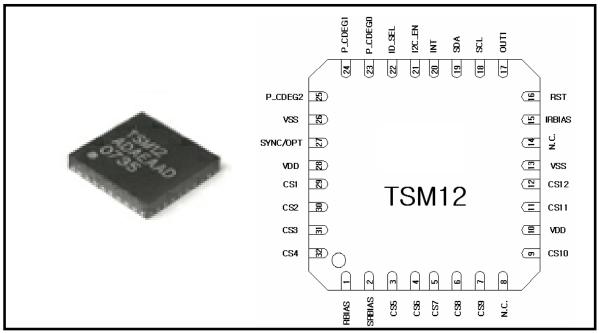

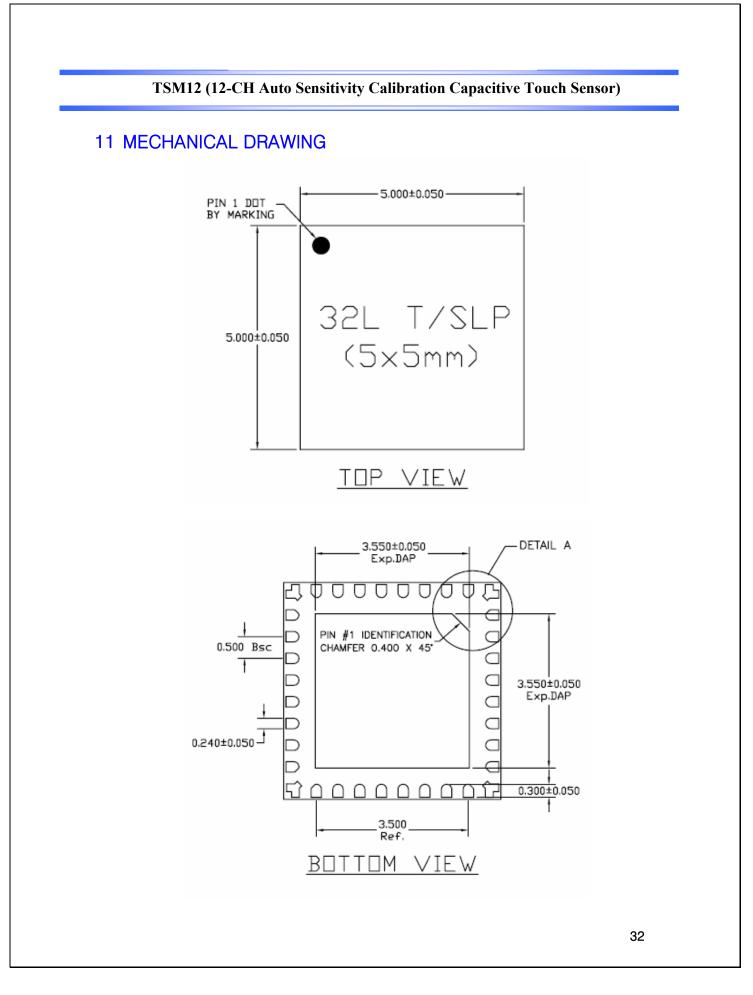

## 1.3 Package (32QFN)

TSM12 32QFN (Drawings not to scale)

| 2 Pin   | 2 Pin Description (32QFN) |                         |                                                                                            |            |  |  |  |  |

|---------|---------------------------|-------------------------|--------------------------------------------------------------------------------------------|------------|--|--|--|--|

| PIN No. | Name                      | I/O                     | Description                                                                                | Protection |  |  |  |  |

| 1       | RBIAS                     | Analog Input            | Internal bias adjust input                                                                 | VDD/GND    |  |  |  |  |

| 2       | SRBIAS                    | Analog Input            | IDLE Mode Internal bias adjust input                                                       | VDD/GND    |  |  |  |  |

| 3       | CS5                       | Analog Input            | CH5 capacitive sensor input                                                                | VDD/GND    |  |  |  |  |

| 4       | CS6                       | Analog Input            | CH6 capacitive sensor input                                                                | VDD/GND    |  |  |  |  |

| 5       | CS7                       | Analog Input            | CH7 capacitive sensor input                                                                | VDD/GND    |  |  |  |  |

| 6       | CS8                       | Analog Input            | CH8 capacitive sensor input                                                                | VDD/GND    |  |  |  |  |

| 7       | CS9                       | Analog Input            | CH9 capacitive sensor input                                                                | VDD/GND    |  |  |  |  |

| 8       | N.C.                      | -                       | No Connection                                                                              | -          |  |  |  |  |

| 9       | CS10                      | Analog Input            | CH10 capacitive sensor input                                                               | VDD/GND    |  |  |  |  |

| 10      | VDD                       | Digital Input           | -                                                                                          | VDD/GND    |  |  |  |  |

| 11      | CS11                      | Analog Input            | CH11 capacitive sensor input                                                               | VDD/GND    |  |  |  |  |

| 12      | CS12                      | Analog Input            | CH12 capacitive sensor input                                                               | VDD/GND    |  |  |  |  |

| 13      | VSS                       | Ground                  | Supply ground                                                                              | VDD        |  |  |  |  |

| 14      | NC                        | _                       | No Connection                                                                              | -          |  |  |  |  |

| 15      | IRBIAS                    | Analog Input            | Internal I2C clk frequency adjust input                                                    | VDD/GND    |  |  |  |  |

| 16      | RST                       | Digital Input           | System reset (High reset)                                                                  | VDD/GND    |  |  |  |  |

| 17      | OUT1                      | Digital Output          | CH1 output (Open drain)                                                                    | VDD/GND    |  |  |  |  |

| 18      | SCL                       | Digital Input           | I2C clock input                                                                            | VDD/GND    |  |  |  |  |

| 19      | SDA                       | Digital<br>Input/Output | I2C data (Open drain)                                                                      | VDD/GND    |  |  |  |  |

| 20      | INT                       | Digital Output          | Interrupt output (Open drain)                                                              | VDD/GND    |  |  |  |  |

| 21      | I2C_EN                    | Digital Input           | I2C enable(Low enable)                                                                     | VDD/GND    |  |  |  |  |

| 22      | ID_SEL                    | Digital Input           | I2C address selection                                                                      | VDD/GND    |  |  |  |  |

| 23      | P_CDEG0                   | Digital Input           | Ch1 sensitivity selection bit0                                                             | VDD/GND    |  |  |  |  |

| 24      | P_CDEG1                   | Digital Input           | Ch1 sensitivity selection bit1                                                             | VDD/GND    |  |  |  |  |

| 25      | P_CDEG2                   | Digital Input           | Ch1 sensitivity selection bit2                                                             | VDD/GND    |  |  |  |  |

| 26      | VSS                       | Digital Input           | -                                                                                          | VDD/GND    |  |  |  |  |

| 27      | SYNC/OPT                  | Digital<br>Input/Output | Output mode selection<br>(Single Output / Multi Output Note 1)<br>Sync pulse input /output | VDD/GND    |  |  |  |  |

| 28      | VDD                       | Power                   | Power (2.5V~5.0V)                                                                          | GND        |  |  |  |  |

| 29      | CS1                       | Analog Input            | CH1 capacitive sensor input                                                                | VDD/GND    |  |  |  |  |

| 30      | CS2                       | Analog Input            | CH2 capacitive sensor input                                                                | VDD/GND    |  |  |  |  |

| 31      | CS3                       | Analog Input            | CH3 capacitive sensor input                                                                | VDD/GND    |  |  |  |  |

| 32      | CS4                       | Analog Input            | CH4 capacitive sensor input                                                                | VDD/GND    |  |  |  |  |

Note 1 : Refer to 6.3 SYNC/OPT implementation

# 3 Absolute Maximum Rating

| Battery supply voltage      | 5.0V            |

|-----------------------------|-----------------|

| Maximum voltage on any pin  | VDD+0.3         |

| Maximum current on any PAD  | 100mA           |

| Power Dissipation           | 800mW           |

| Storage Temperature         | -50 ~ 150℃      |

| Operating Temperature       | -20 ~ 75℃       |

| Junction Temperature        | 150℃            |

| Note Unless any other comma | nd is noted all |

Note Unless any other command is noted, all above are operated in normal temperature.

# 4 ESD & Latch-up Characteristics

| Mode   | Polarity  | Мах   | Reference |

|--------|-----------|-------|-----------|

|        |           | 2000V | VDD       |

| H.B.M  | Pos / Neg | 2000V | VSS       |

|        |           | 2000V | P to P    |

|        |           | 200V  | VDD       |

| M.M    | Pos / Neg | 200V  | VSS       |

|        |           | 200V  | P to P    |

| 0.0.14 | Dec / Neg | 500V  | DIRECT    |

| C.D.M  | Pos / Neg | 800V  | DINECT    |

## 4.1 ESD Characteristics

## 4.2 Latch-up Characteristics

| Mode               | Polarity | Max    | Test Step |  |  |

|--------------------|----------|--------|-----------|--|--|

| l Test             | Positive | 200mA  | 25mA      |  |  |

| TTest              | Negative | -200mA | 25111A    |  |  |

| V supply over 5.0V | Positive | 8.0V   | 1.0V      |  |  |

# 5 Electrical Characteristics

| V <sub>DD</sub> =3.3V, Rb=510k, Syn | c Mode (Rsync = 2MQ) | ) (Unless otherwise note | d) T₄ = 25℃ |

|-------------------------------------|----------------------|--------------------------|-------------|

| $V_{DD}$ 0.0V, HD 010K, Oyh         |                      |                          | u), 1A 200  |

| Characteristics                           | Symbol              | Test Condition                                                          | Min | Тур | Max  | Units    |

|-------------------------------------------|---------------------|-------------------------------------------------------------------------|-----|-----|------|----------|

| Operating supply voltage                  | V <sub>DD</sub>     |                                                                         | 2.5 | 3.3 | 5.0  | V        |

|                                           |                     | $V_{DD}$ = 3.3V R <sub>B</sub> =510k R_SB=0                             | -   | 80  | 130  |          |

|                                           |                     | $V_{DD}$ = 5.0V R <sub>B</sub> =510k R_SB=0                             | -   | 200 | 315  | ٨        |

| Current consumption                       | I <sub>DD</sub>     | $V_{DD}$ = 3.3V R <sub>B</sub> =510k R_SB=3M                            | -   | 7   | _    | μA       |

|                                           |                     | $V_{DD}$ = 5.0V R <sub>B</sub> =510k R_SB=3M                            | -   | 15  | _    |          |

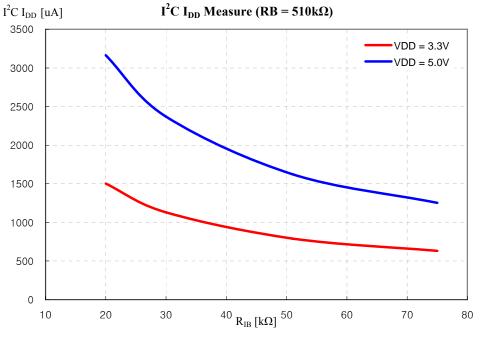

| Note1                                     |                     | $V_{DD}$ = 3.3V R <sub>B</sub> =510k R <sub>I2C</sub> =20k              | -   | 1.5 | _    | <b>~</b> |

|                                           | I <sub>DD_I2C</sub> | $V_{DD}$ = 5.0V R <sub>B</sub> =510k R <sub>I2C</sub> =30k              | -   | 2.3 | _    | mΑ       |

|                                           |                     | IDD_I2C Disable                                                         | -   | _   | 1    | μA       |

| Output maximum sink<br>current            | Ι <sub>ουτ</sub>    | T <sub>A</sub> = 25℃                                                    | _   | -   | 4.0  | mA       |

| Sense input<br>capacitance range<br>Note2 | Cs                  |                                                                         | _   | 10  | 100  | рF       |

| Sense input<br>resistance range           | R <sub>s</sub>      |                                                                         | _   | 200 | 1000 | Ω        |

| Minimum detective capacitance difference  | ΔC                  | Cs = 10pF, C <sub>DEG</sub> = 200pF<br>(I2C default sensitivity select) | 0.2 | _   | _    | pF       |

| Output impedance                          | 7.                  | $\Delta C > 0.2 pF$ , Cs = 10pF,<br>(I2C default sensitivity select)    | -   | 12  | -    | 0        |

| (open drain)                              | Zo                  | $\Delta C < 0.2 pF$ , Cs = 10pF,<br>(I2C default sensitivity select)    | _   | 30M | _    | Ω        |

| Self calibration time after               | т                   | $V_{DD} = 3.3 V R_B = 510 k$                                            | -   | 100 | _    |          |

| system reset                              | T <sub>CAL</sub>    | $V_{DD} = 5.0V R_{B} = 510k$                                            | -   | 80  | -    | ms       |

| Recommended bias<br>resistance range      | R <sub>B</sub>      | $V_{DD} = 3.3V$                                                         | 200 | 510 | 820  | kΩ       |

| Note3                                     |                     | $V_{DD} = 5.0 V$                                                        | 330 | 620 | 1200 |          |

| Maximum bias<br>capacitance               | C <sub>B_MAX</sub>  |                                                                         | -   | 820 | 1000 | рF       |

| Recommended sync<br>resistance range      | R <sub>SYNC</sub>   |                                                                         | 1   | 2   | 20   | MΩ       |

Note 1 : In case of SCL frequency is 500kHz.

Note 2 : The sensitivity can be increased with lower  $C_{\mbox{\scriptsize S}}$  value.

The recommended value of  $C_S$  is 10pF when using 3T PC(Poly Carbonate) cover and 10 mm x 7 mm touch pattern.

Note 3 : The lower  $\mathsf{R}_{\mathsf{B}}$  is recommended in noisy condition.

# 6 Implementation of TSM12

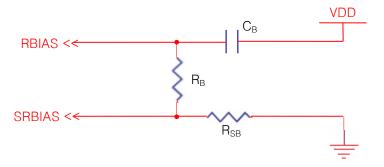

#### 6.1 RBIAS & SRBIAS implementation

The RBIAS is connecting to the resistor to decide the oscillator and internal bias current. The sensing frequency, internal clock frequency and current consumption are therefore able to be adjusted with  $R_B$ . A voltage ripple on RBIAS can make critical internal error, so  $C_B$  is connected to the VDD (not GND) is recommended. (The typical value of  $C_B$  is 820pF and the maximum Value is 1nF.)

The  $R_{SB}$  should be connected as above figure when the TSM12 operates in IDLE Mode to save the current consumption. In this case, the consumption depends on the sum of the serial resistors and the response time might be longer.

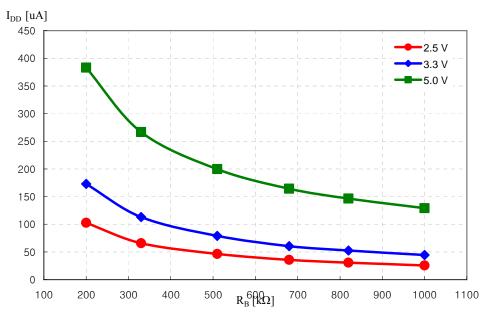

Normal operation current consumption curve (Pin21 I2C\_EN is High)

The current consumption curve of TSM12 is represented in accordance with  $R_B$  value as above. The lower  $R_B$  requires more current consumption but it is recommended in noisy application. For example, refrigerator, air conditioner and so on.

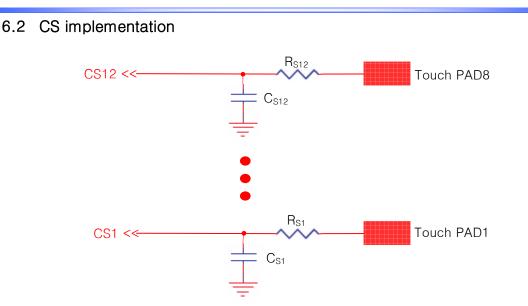

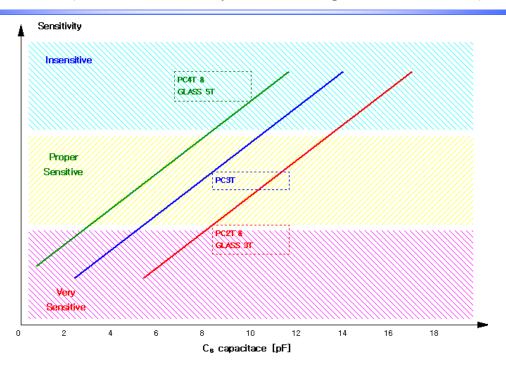

The TSM12 has basically eight steps sensitivity, which is available to control with internal register by I2C interface. The parallel capacitor  $C_{S1}$  is added to CS1 and  $C_{S12}$  to CS12 to adjust sensitivity. The sensitivity will be increased when smaller value of  $C_S$  is used. (Refer to the below Sensitivity Example Figure) It could be useful in case detail sensitivity mediation is required. The internal touch decision process of each channel is separated from each other. The twelve channel touch key board application can therefore be designed by using only one TSM12 without coupling problem. The  $R_S$  is serial connection resistor to avoid mal-function from external surge and ESD. (It might be optional.) From 200 $\Omega$  to 1k $\Omega$  is recommended for  $R_S$ . The size and shape of PAD might have influence on the sensitivity. The sensitivity will be optimal when the size of PAD is approximately an half of the first knuckle (it's about 10 mm x 7 mm). The connection line of CS1 ~ CS12 to touch PAD is recommended to be routed as short as possible to prevent from abnormal touch detect caused by connection line.

TSM12 (12-CH Auto Sensitivity Calibration Capacitive Touch Sensor)

Sensitivity example figure with default sensitivity selection

## 6.3 SYNC/OPT implementation

#### 6.3.1 Output Mode Option

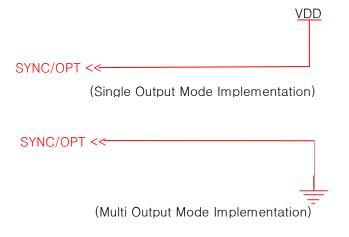

This pin will be assigned for the output mode option selection. It will decide that TSM12 is working on single or multi touch detection mode. It should be implemented as below for these.

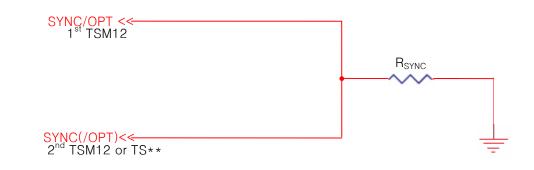

#### 6.3.2 Multi Chip Application

Over two TSM12 can work on the one application at the same time thanks to SYNC function with this pin. The SYNC pulse prevents over two sensing signal from interfering with each other.  $R_{SYNC}$  is pull-down resistor of SYNC/OPT pin. Too big value of  $R_{SYNC}$  makes the SYNC pulse falling delay, and too small value of  $R_{SYNC}$  makes rising delay. Typical value of  $R_{SYNC}$  is 2M $\Omega$ .The Sync pin should be implemented as below. The TSM12 can also be used with the other TSxx series by employing this SYNC function. The TSM12 could only operate on multi output mode in this configuration.

## 6.4 P\_CDEG2 , P\_CDEG1 , P\_CDEG0 implementation

The P\_CDEG0, 1 and 2 are only for the CS1 to control the sensitivity. The sensitivity of channel 1 will be controlled by the register (refer to the "sensitivity control register" chapter) same as the other channel if the P\_CDEG(2:0) value is 011. But it should be fixed as following table if the P\_CDEG(2:0) value is not 011.

| _           | The sensitivity table of channel 1                                 |  |  |  |  |  |  |

|-------------|--------------------------------------------------------------------|--|--|--|--|--|--|

| P_CDEG(2:0) | Sensitivity of Channel 1 (@Cs = 0pF)                               |  |  |  |  |  |  |

| 011         | Respect the register value (refer to the I2C register description) |  |  |  |  |  |  |

| 000         | 14~16T                                                             |  |  |  |  |  |  |

| 001         | 12~14T                                                             |  |  |  |  |  |  |

| 010         | 10~12T                                                             |  |  |  |  |  |  |

| 100         | 7~9T                                                               |  |  |  |  |  |  |

| 101         | 6~8T                                                               |  |  |  |  |  |  |

| 110         | 5~7T                                                               |  |  |  |  |  |  |

| 111         | 3~5T                                                               |  |  |  |  |  |  |

Note 1: The unit T represents the thickness (mm) of a panel in case of poly-carbonate. Note 2: The above table data is compatible with a pad size that is approximately an half of the first knuckle. (it's about 10 mm x 7 mm)

The channel 1 provides the output with two ways whether the I2C or the out1 (pin17) directly.

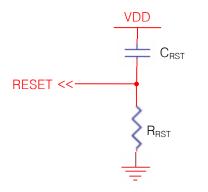

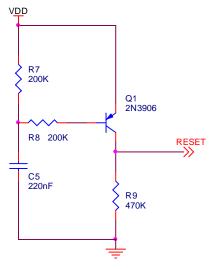

## 6.5 RESET implementation

TSM12 has internal data latches, so initial state of these latches must be reset by external reset pulse before normal operation starts. The reset pulse can be controlled by host MCU directly or other reset device. If not, the circuit should be composed as below figure. The reset pulse must have high pulse duration about a few msec to cover power VDD rising time. The recommended value of  $R_{RST}$  and  $C_{RST}$  are 330K $\Omega$  and 100nF.

Recommended reset circuits 1

The better performance is warranted with below reset circuit. The Q1 is turned on and makes reset pulse when power is on and VDD is raised to operating voltage. After a few msec (duration time is determined by R7, R8, C5), Q1 is turned off and TSM12 can be operated with normal sensitivity.

Recommended reset circuits 2

# 7 I<sup>2</sup>C Interface

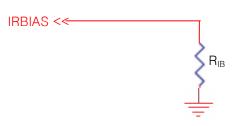

## 7.1 IRBIAS Implementation

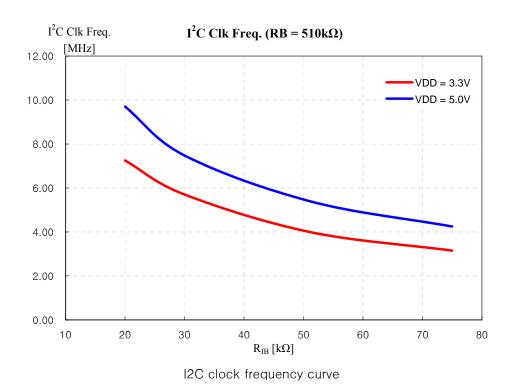

The  $R_{IB}$  is only charged in making the I2C internal clock and should be implemented as above figure. The smaller  $R_{IB}$  will increase the I2C internal clock frequency and current consumption. (Refer to the following consumption curve)

10

## 7.2 Start & Stop Condition

- ◀ Start Condition (S)

- ◀ Repeated Start (Sr)

The EN (Pin21) should be low before START condition and be high after STOP condition.

## 7.3 Data validity

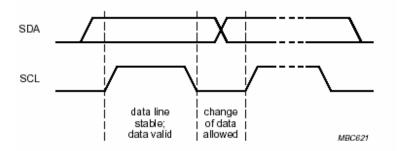

The SDA should be stable when the SCL is high and the SDA can be changed when the SCL is low.

#### 7.4 Byte Format

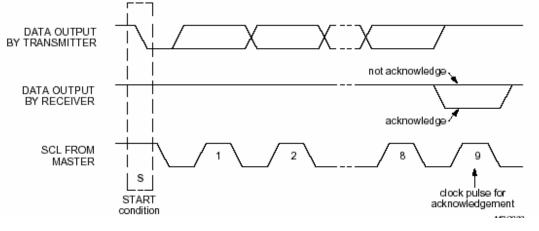

The byte structure is composed with 8Bit data and an acknowledge signal.

## 7.5 Acknowledge

It is a check bit whether the receiver gets the data from the transmitter without error or not. The receiver will write '0' when it received the data successfully and '1' if not.

# 7.6 First Byte

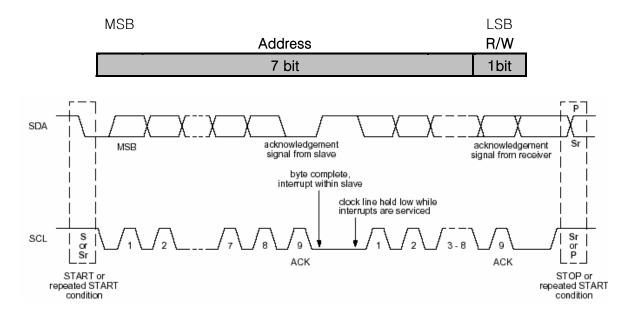

## 7.6.1 Slave Address

It is the first byte from the start condition. It is used to access the slave device.

| TSM12 Chip Address : 7bit |         |  |  |  |  |

|---------------------------|---------|--|--|--|--|

| ID_SEL                    | Address |  |  |  |  |

| GND                       | 0xD0    |  |  |  |  |

| VDD                       | 0xF0    |  |  |  |  |

# 7.6.2 R/W

The direction of data is decided by the bit and it follows the address data.

## 7.7 Transferring Data

#### 7.7.1 Write Operation

The byte sequence is as follows:

If the first byte gives the device address plus the direction bit (R/W = 0).

the second byte contains the internal address of the first register to be accessed.

■ the next byte is written in the internal register. Following bytes are written in successive internal registers.

the transfer lasts until stop conditions are encountered.

■ the TSM12 acknowledges every byte transfer.

| S SLAVE ADDRESS RW   | A DATA A DATA AA P                                    |

|----------------------|-------------------------------------------------------|

| '0' (write)          | data transferred<br>(n bytes + acknowledge)           |

| from master to slave | A = acknowledge (SDA LOW)                             |

| from slave to master | A = not acknowledge (SDA HIGH)<br>S = START condition |

| MBC605               | P = STOP condition                                    |

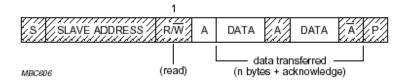

## 7.7.2 Read Operation

The address of the first register to read is programmed in a write operation without data, and terminated by the stop condition. Then, another start is followed by the device address and R/W= 1. All following bytes are now data to be read at successive positions starting from the initial address.

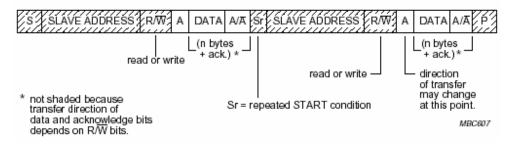

## 7.7.3 Read/Write Operation

| 7.8 I <sup>2</sup> C write and read operations in normal mode |                       |                              |          |               |         |          |     |      |  |

|---------------------------------------------------------------|-----------------------|------------------------------|----------|---------------|---------|----------|-----|------|--|

| The followir                                                  | ng figure repres      | ents the I <sup>2</sup> C no | ormal m  | ode write and | read re | gisters. |     |      |  |

| 🖙 Write reg                                                   | jister 0x00 to 0>     | 01 with data A               | AA and I | BB            |         |          |     |      |  |

| Start                                                         | evice<br>ess 0xD0 ACK | Register<br>Address 0x00     | АСК      | Data AA       | ACK     | Data BB  | ACK | Stop |  |

| Read regist                                                   | er 0x00 and 0x0       | 01                           |          | ·             |         |          |     |      |  |

| Start                                                         | evice<br>ess 0xD0 ACK | Register<br>Address 0x00     | ACK      | Stop          |         |          |     |      |  |

|                                                               |                       |                              |          |               |         |          |     |      |  |

| Start                                                         | evice<br>ess 0xD1 ACK | Data Read AA                 | ACK      | Data Read BB  | ACK     | Stop     |     |      |  |

| From Master to Slave From Slave to Master                     |                       |                              |          |               |         |          |     |      |  |

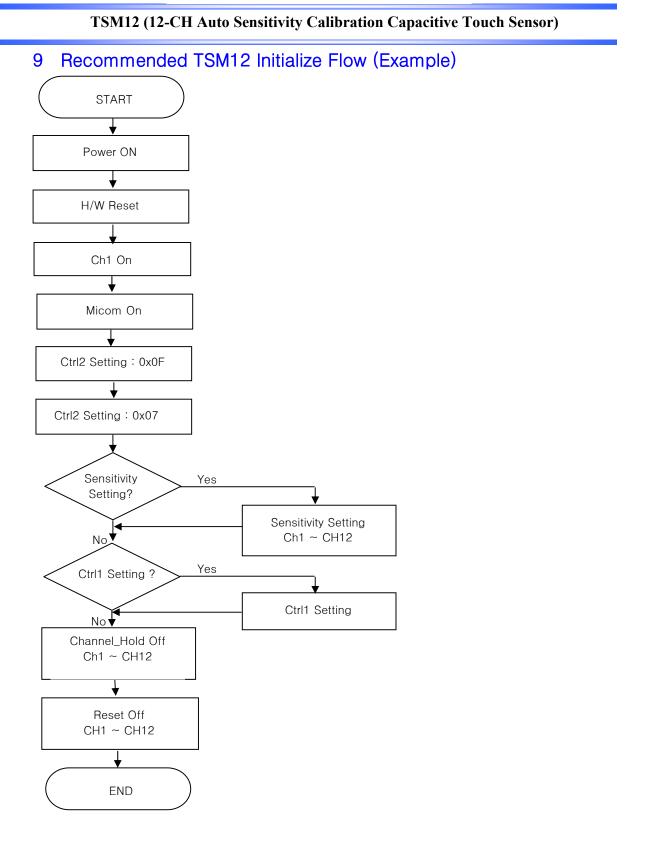

# 8 TSM12 Register List

◀ Note: The unused bits (defined as reserved) in I<sup>2</sup>C registers must be kept to zero.

- ◀ Note: The bit0 and bit1 of CTRL2 register must be written by 0b11 after power on during an initialize phase. (Refer to the chapter 9. initialize flow)

- ◀ Note: HS (High Sensitivity) / MS (Middle Sensitivity) / LS (Low Sensitivity)

- ◀ Note: Low Output (light touch) / Middle Output (middle touch) / High Output (hard touch)

| Name         | Addr. | Reset Value | e Register Function and Description |                    |       |        |       |      |      |      |

|--------------|-------|-------------|-------------------------------------|--------------------|-------|--------|-------|------|------|------|

| Name         | (Hex) | (Bin)       | Bit7                                | Bit6 Bit5 Bit4     |       | Bit4   | Bit3  | Bit2 | Bit1 | Bit0 |

| Sensitivity1 | 02h   | 1011 1011   | Ch2HL                               |                    | Ch2M  |        | Ch1HL |      | Ch1M |      |

| Sensitivity2 | 03h   | 1011 1011   | Ch4HL                               |                    | Ch4M  |        | Ch3HL |      | Ch3M |      |

| Sensitivity3 | 04h   | 1011 1011   | Ch6HL                               |                    | Ch6M  |        | Ch5HL |      | Ch5M |      |

| Sensitivity4 | 05h   | 1011 1011   | Ch8HL                               |                    | Ch8M  |        | Ch7HL |      | Ch7M |      |

| Sensitivity5 | 06h   | 1011 1011   | Ch10HL                              |                    | Ch10M |        | Ch9HL |      | Ch9M |      |

| Sensitivity6 | 07h   | 1011 1011   | Ch12HL                              | Ch12HL Ch12M Ch11H |       | Ch11HL | Ch11M |      |      |      |

| CTRL1        | 08h   | 0010 0010   | MS                                  | FT                 | ГC    | IL     | С     | RTC  |      |      |

| CTRL2        | 09h   | 0000 01XX   | 0                                   | 0                  | 0     | 0      | SRST  | IDLE | 1    | 1    |

| Ref_rst1     | 0Ah   | 1111 1110   | Ch8                                 | Ch7                | Ch6   | Ch5    | Ch4   | Ch3  | Ch2  | Ch1  |

| Ref_rst2     | 0Bh   | 0000 1111   | 0                                   | 0                  | 0     | 0      | Ch12  | Ch11 | Ch10 | Ch9  |

| Ch_hold1     | 0Ch   | 1111 1110   | Ch8                                 | Ch7                | Ch6   | Ch5    | Ch4   | Ch3  | Ch2  | Ch1  |

| Ch_hold2     | 0Dh   | 0000 1111   | 0                                   | 0                  | 0     | 0      | Ch12  | Ch11 | Ch10 | Ch9  |

| Cal_hold1    | 0Eh   | 0000 0000   | Ch8                                 | Ch7                | Ch6   | Ch5    | Ch4   | Ch3  | Ch2  | Ch1  |

| Cal_hold2    | 0Fh   | 0000 0000   | 0                                   | 0                  | 0     | 0      | Ch12  | Ch11 | Ch10 | Ch9  |

| Output1      | 10h   | 0000 0000   | OU                                  | OUT4 OUT3          |       | OU     | T2    | OU   | T1   |      |

| Output2      | 11h   | 0000 0000   | OU                                  | Т8                 | OU    | T 7    | OU    | T6   | OU   | T5   |

| Output3      | 12h   | 0000 0000   | OU                                  | T12                | OU.   | T11    | OU    | T10  | OU   | Т9   |

# 8.1 I<sup>2</sup>C Register Map

## 8.2 Sensitivity Control Register

| <mark>Sen</mark><br>Address (h<br>Type: R/W |      |           |      |       |      |           |      |

|---------------------------------------------|------|-----------|------|-------|------|-----------|------|

| Bit7                                        | Bit6 | Bit5      | Bit4 | Bit3  | Bit2 | Bit1      | Bit0 |

| Ch2HL                                       |      | Ch2M[2:0] |      | Ch1HL |      | Ch1M[2:0] |      |

#### Description

The sensitivity of channel 1 and 2 are adjustable by Sensitivity\_1 register. ChxM[2:0] allows various middle sensitivity and also the high and low sensitivities are decided with ChxHL.

| Bit name  | Reset | Function                                                                                                                                          |

|-----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| ChxM[2:0] | 011   | Middle sensitivity T (= thickness of PC) @Cs = 0pF                                                                                                |

| ChxHL     | 1     | High and Low sensitivity selection for channel x0: $HS = MS - (MS * 0.2)$ $LS = MS + (MS * 0.2)$ 1: $HS = MS - (MS * 0.3)$ $LS = MS + (MS * 0.3)$ |

#### Sensitivity2

#### Channel 3 & 4 Sensitivity Control

| Address (hex): 03h |  |  |  |  |  |

|--------------------|--|--|--|--|--|

| Type: R/W          |  |  |  |  |  |

| Bit7 Bit6 Bit5     |  |  |  |  |  |

| Ch4HL Ch4M[2:0]    |  |  |  |  |  |

# Bit6Bit5Bit4Bit3Bit2Ch4M[2:0]Ch3HL

#### Description

The sensitivity of channel 3 and 4 are adjustable by Sensitivity\_2 register. ChxM[2:0] allows various middle sensitivity and also the high and low sensitivities are decided with ChxHL.

| Bit name  | Reset | Function                                           |

|-----------|-------|----------------------------------------------------|

|           |       | Middle sensitivity T (= thickness of PC) @Cs = 0pF |

|           |       | 🜲 000: 14~16T 🛛 👫 100: 7~9T                        |

| ChxM[2:0] | 011   | 🖕 001: 12~14T 🖌 101: 6~8T                          |

|           |       | 🞍 010: 10~12T 🛛 4 110: 5~7T                        |

|           |       | 🜲 011: 08~10T 🛛 4 111: 3~5T                        |

|           |       | High and Low sensitivity selection for channel x   |

|           |       | 0: $HS = MS - (MS * 0.2)$                          |

| ChxHL     | 1     | LS = MS + (MS * 0.2)                               |

|           |       | 1: $HS = MS - (MS * 0.3)$                          |

|           |       | LS = MS + (MS * 0.3)                               |

Bit0

Bit1

Ch3M[2:0]

| <mark>Sen</mark><br>Address (ł | i <mark>sitivity3</mark><br>nex): 04h | Ch        | annel 5 8 | 6 Sensitiv | vity Contro | bl        |      |

|--------------------------------|---------------------------------------|-----------|-----------|------------|-------------|-----------|------|

| Type: R/W                      | 1                                     |           |           |            |             |           |      |

| Bit7                           | Bit6                                  | Bit5      | Bit4      | Bit3       | Bit2        | Bit1      | Bit0 |

| Ch6HL                          |                                       | Ch6M[2:0] |           | Ch5HL      |             | Ch5M[2:0] |      |

#### Description

The sensitivity of channel 5 and 6 are adjustable by Sensitivity\_3 register. ChxM[2:0] allows various middle sensitivity and also the high and low sensitivities are decided with ChxHL.

| Bit name  | Reset | Function                                           |  |  |  |

|-----------|-------|----------------------------------------------------|--|--|--|

|           |       | Middle sensitivity T (= thickness of PC) @Cs = 0pF |  |  |  |

|           |       | ♣ 000: 14~16T ♣ 100: 7~9T                          |  |  |  |

| ChxM[2:0] | 011   | ♣ 001: 12~14T ♣ 101: 6~8T                          |  |  |  |

|           |       | 📥 010: 10~12T 🛛 📥 110: 5~7T                        |  |  |  |

|           |       | ♣ 011: 08~10T ♣ 111: 3~5T                          |  |  |  |

|           |       | High and Low sensitivity selection for channel x   |  |  |  |

|           |       | 0: HS = MS - (MS * 0.2)                            |  |  |  |

| ChxHL     | 1     | LS = MS + (MS * 0.2)                               |  |  |  |

|           |       | 1: HS = MS - (MS * 0.3)                            |  |  |  |

|           |       | LS = MS + (MS * 0.3)                               |  |  |  |

## Channel 7 & 8 Sensitivity Control

Sensitivity4 Address (hex): 05h Type: R/W

| Bit7  | Bit6 | Bit5      | Bit4 | Bit3  | Bit2 | Bit1      | Bit0 |

|-------|------|-----------|------|-------|------|-----------|------|

| Ch8HL |      | Ch8M[2:0] |      | Ch7HL |      | Ch7M[2:0] |      |

#### Description

The sensitivity of channel 7 and 8 are adjustable by Sensitivity\_4 register. ChxM[2:0] allows various middle sensitivity and also the high and low sensitivities are decided with ChxHL.

| Bit name  | Reset | Function                                           |

|-----------|-------|----------------------------------------------------|

|           |       | Middle sensitivity T (= thickness of PC) @Cs = 0pF |

|           |       | o00: 14~16T ↓ 100: 7~9T                            |

| ChxM[2:0] | 011   | i 001: 12∼14T i 101: 6~8T                          |

|           |       | ♣ 010: 10~12T ♣ 110: 5~7T                          |

|           |       | 🞍 011: 08~10T 🛛 🕌 111: 3~5T                        |

|           |       | High and Low sensitivity selection for channel x   |

|           |       | 0: $HS = MS - (MS * 0.2)$                          |

| ChxHL     | 1     | LS = MS + (MS * 0.2)                               |

|           |       | 1: HS = MS - (MS * 0.3)                            |

|           |       | LS = MS + (MS * 0.3)                               |

| <mark>Sen</mark><br>Address (h<br>Type: R/W |            | Ch   | annel 9 8 | 10 Sensit | ivity Conti | rol       |      |

|---------------------------------------------|------------|------|-----------|-----------|-------------|-----------|------|

| Bit7                                        | Bit6       | Bit5 | Bit4      | Bit3      | Bit2        | Bit1      | Bit0 |

| Ch10HL                                      | Ch10M[2:0] |      |           | Ch9HL     |             | Ch9M[2:0] |      |

#### Description

The sensitivity of channel 9 and 10 are adjustable by Sensitivity\_5 register.ChxM[2:0] allows various middle sensitivity and also the high and low sensitivities are decided with ChxHL.

| Bit name  | Reset | Function                                           |  |  |  |

|-----------|-------|----------------------------------------------------|--|--|--|

|           |       | Middle sensitivity T (= thickness of PC) @Cs = 0pF |  |  |  |

|           |       | ♣ 000: 14~16T ♣ 100: 7~9T                          |  |  |  |

| ChxM[2:0] | 011   | ♣ 001: 12~14T ♣ 101: 6~8T                          |  |  |  |

|           |       | 📥 010: 10~12T 🛛 🐇 110: 5~7T                        |  |  |  |

|           |       | ♣ 011: 08~10T ♣ 111: 3~5T                          |  |  |  |

|           |       | High and Low sensitivity selection for channel x   |  |  |  |

|           |       | 0: HS = MS - (MS * 0.2)                            |  |  |  |

| ChxHL     | 1     | LS = MS + (MS * 0.2)                               |  |  |  |

|           |       | 1: HS = MS - (MS * 0.3)                            |  |  |  |

|           |       | LS = MS + (MS * 0.3)                               |  |  |  |

| Channel 11 | & 12 Sensitivity | Control |

|------------|------------------|---------|

|------------|------------------|---------|

Sensitivity6 Address (hex): 07h Type: R/W

| Bit7   | Bit6 | Bit5       | Bit4 | Bit3   | Bit2 | Bit1       | Bit0 |

|--------|------|------------|------|--------|------|------------|------|

| Ch12HL |      | Ch12M[2:0] |      | Ch11HL |      | Ch11M[2:0] |      |

#### Description

The sensitivity of channel 11 and 12 are adjustable by Sensitivity\_6 register. ChxM[2:0] allows various middle sensitivity and also the high and low sensitivities are decided with ChxHL.

| Bit name  | Reset | Function                                           |

|-----------|-------|----------------------------------------------------|

|           |       | Middle sensitivity T (= thickness of PC) @Cs = 0pF |

|           |       | 📥 000: 14~16T 🛛 🕌 100: 7~9T                        |

| ChxM[2:0] | 011   | 🜲 001: 12~14T 🔹 101: 6~8T                          |

|           |       | ♣ 010: 10~12T ♣ 110: 5~7T                          |

|           |       | 🞍 011: 08~10T 🛛 🗍 111: 3~5T                        |

|           |       | High and Low sensitivity selection for channel x   |

|           |       | 0: $HS = MS - (MS * 0.2)$                          |

| ChxHL     | 1     | LS = MS + (MS * 0.2)                               |

|           |       | 1: $HS = MS - (MS * 0.3)$                          |

|           |       | LS = MS + (MS * 0.3)                               |

# 8.3 General Control Register1

CTRL1

TSM12 General Control Register1

Address (hex): 08h Type: R/W

| Type: n/w |          |      |      |      |          |      |      |  |

|-----------|----------|------|------|------|----------|------|------|--|

| Bit7      | Bit6     | Bit5 | Bit4 | Bit3 | Bit2     | Bit1 | Bit0 |  |

| MS        | FTC[1:0] |      | ILC[ | 1:0] | RTC[2:0] |      |      |  |

#### Description

The calibration speed just after power on reset is very high during the time which is defined by FTC[1:0] to have a good adoption against unstable external environment.

| Bit name | Reset | Function                                                                                                                                                                                                     |  |  |  |

|----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MS       | 0     | Mode Selection<br>0: auto alternate (fast/slow) mode<br>1: fast mode                                                                                                                                         |  |  |  |

| FTC[1:0] | 01    | First Touch Control<br>Below time stands on VDD = 3V / Rb = 300KΩ<br>00: 5 sec<br>01: 10 sec<br>10: 15 sec<br>11: 20 sec                                                                                     |  |  |  |

| ILC[1:0] | 00    | Interrupt Level Control<br>00: Interrupt is on middle or high output.<br>01: Interrupt is on low or middle or high output.<br>10: Interrupt is on middle or high output.<br>11: Interrupt is on high output. |  |  |  |

| RTC[2:0] | 011   | Response Time Control<br>Response period = RTC[2:0] + 2                                                                                                                                                      |  |  |  |

## 8.4 General Control Register2

CTRL2

TSM12 General Control Register2

Address (hex): 09h Type: R/W

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2  | Bit1 | Bit0 |

|------|------|------|------|------|-------|------|------|

| 0    | 0    | 0    | 0    | SRST | SLEEP | 1    | 1    |

#### Description

All the digital blocks except analog and I2C block are reset when SRST is set. The SLEEP function allows getting very low current consumption when it is set. But the response time will be longer than normal operation. The bit0 and bit1 must be written with 0b'11 by host MCU.

| Bit name | Reset | Function                                                       |  |  |  |  |

|----------|-------|----------------------------------------------------------------|--|--|--|--|

|          |       | Software Reset                                                 |  |  |  |  |

| SRST     | 0     | 0: Disable Software Reset                                      |  |  |  |  |

|          |       | 1: Enable Software Reset                                       |  |  |  |  |

|          |       | Sleep Mode Enable                                              |  |  |  |  |

| SLEEP    | 1     | 0: Disable Sleep Mode                                          |  |  |  |  |

|          |       | 1: Enable Sleep Mode                                           |  |  |  |  |

| Bit[1:0] | XX    | These bits must be written by 0b'11 during a system initialize |  |  |  |  |

| DIL[1.0] |       | phase. (refer to the chapter 9 "initialize flow example")      |  |  |  |  |

## 8.5 Channel Reference Reset Control Register

| Ref_rst1Channel1~8 Reference Reset ControlAddress (hex): 0AhType: R/W |      |      |      |      | ontrol |      |      |

|-----------------------------------------------------------------------|------|------|------|------|--------|------|------|

| Bit7                                                                  | Bit6 | Bit5 | Bit4 | Bit3 | Bit2   | Bit1 | Bit0 |

| Ch8                                                                   | Ch7  | Ch6  | Ch5  | Ch4  | Ch3    | Ch2  | Ch1  |

#### Description

The reference value of each channel will be renewing when Chx is set.

| Bit name | Reset | Function                   |

|----------|-------|----------------------------|

| Chx      | 1     | 0: Disable reference reset |

|          | I     | 1: Enable reference reset  |

| Ch1      | 0     | 0: Disable reference reset |

|          |       | 1: Enable reference reset  |

## Ref\_rst2

#### Channel9~12 Reference Reset Control

Bit2

Ch11

Bit1

Ch10

Bit0

Ch9

Bit3

Address (hex): 0Bh Type: R/W Bit7 Bit6 0 0

0 0 0 0 Ch12

Bit5

Description

The reference value of each channel will be renewing when Chx is set.

Bit4

| Bit name | Reset | Function                                                |

|----------|-------|---------------------------------------------------------|

| Chx      | 1     | 0: Disable reference reset<br>1: Enable reference reset |

#### 8.6 Channel 1~8 Sensing Control Register

| Ch_hold1 Channel 1 ~ 8 Hold Enable Register<br>Address (hex): 0Ch<br>Type: R/W |      |      |      |      | ster |      |      |

|--------------------------------------------------------------------------------|------|------|------|------|------|------|------|

| Bit7                                                                           | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| Ch8                                                                            | Ch7  | Ch6  | Ch5  | Ch4  | Ch3  | Ch2  | Ch1  |

#### Description

The operation of each channel is independently available to control. A channel doesn't be worked and the calibration is paused when it is set.

| Bit name | Reset | Function                                                                                         |  |  |  |

|----------|-------|--------------------------------------------------------------------------------------------------|--|--|--|

| Chx      | 1     | 0: Enable operation (sensing + calibration)<br>1: Hold operation (No sensing + Stop calibration) |  |  |  |

|          |       |                                                                                                  |  |  |  |

| Ch1      |       | 0: Enable operation (sensing + calibration)                                                      |  |  |  |

|          |       | 1: Hold operation (No sensing + Stop calibration)                                                |  |  |  |

#### 8.7 Channel 9~12 Sensing Control Register

| Ch_<br>Address (h<br>Type: R/W |      | Ch   | Channel 9 ~ 12 Hold Enable Register |      |      |      |      |

|--------------------------------|------|------|-------------------------------------|------|------|------|------|

| Bit7                           | Bit6 | Bit5 | Bit4                                | Bit3 | Bit2 | Bit1 | Bit0 |

| 0                              | 0    | 0    | 0                                   | Ch12 | Ch11 | Ch10 | Ch9  |

#### Description

The operation of each channel is independently available to control. A channel doesn't be worked and the calibration is paused when it is set.

| Bit name | Reset | Function                                                                                         |  |  |  |

|----------|-------|--------------------------------------------------------------------------------------------------|--|--|--|

| CEx      | 1     | 0: Enable operation (sensing + calibration)<br>1: Hold operation (No sensing + Stop calibration) |  |  |  |

## 8.8 Channel 1~8 Calibration Control Register

| Cal_hold1Channel 1 ~ 8 Calibration Enable RegisterAddress (hex): 0Eh |      |      |      |      |      |      |      |

|----------------------------------------------------------------------|------|------|------|------|------|------|------|

| Type: R/W                                                            | ,    |      |      |      |      |      |      |

| Bit7                                                                 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| Ch8                                                                  | Ch7  | Ch6  | Ch5  | Ch4  | Ch3  | Ch2  | Ch1  |

#### Description

The calibration of each channel is independently available to control. Each channel is working even if a bit is set.

| Bit name | Reset | Function                                                    |

|----------|-------|-------------------------------------------------------------|

| Chx 0    | 0     | 0: Enable reference calibration (sensing + calibration)     |

|          | 0     | 1: Disable reference calibration (sensing + No calibration) |

## 8.9 Channel 9~12 Calibration Control Register

| <mark>Cal</mark><br>Address (h | <b>_hold2</b><br>nex): 0Fh | Channel 9 ~ 12 Calibration Enable Register |      |      |      |      | ər   |

|--------------------------------|----------------------------|--------------------------------------------|------|------|------|------|------|

| Type: R/W                      | ,                          |                                            |      |      |      |      |      |

| Bit7                           | Bit6                       | Bit5                                       | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

| 0                              | 0                          | 0                                          | 0    | Ch12 | Ch11 | Ch10 | Ch9  |

#### Description

The calibration of each channel is independently available to control. Each channel is working even if a bit is set.

| Bit name | Reset                                                   | Function                                                    |

|----------|---------------------------------------------------------|-------------------------------------------------------------|

| Chx 0    | 0: Enable reference calibration (sensing + calibration) |                                                             |

|          | 0                                                       | 1: Disable reference calibration (sensing + No calibration) |

# 8.10 Output Register

| Outr<br>Address (h |       | Channel   | 1 ~ 4 Out | put Regist | er   |      |       |

|--------------------|-------|-----------|-----------|------------|------|------|-------|

| Type: R<br>Bit7    | Bit6  | Bit5      | Bit4      | Bit3       | Bit2 | Bit1 | Bit0  |

| OUT4               | [1:0] | OUT3[1:0] |           | OUT2[1:0]  |      | OUT1 | [1:0] |

#### Description

The each channel output of TSM12 is compressed with 2 bits. It has 3 level output information that is low, middle and high.

| Bit name  | Reset | Function            |

|-----------|-------|---------------------|

|           |       | Output of channel 4 |

|           |       | 00: No output       |

| OUT4[1:0] | 00    | 01: low output      |

|           |       | 10: middle output   |

|           |       | 11: high output     |

|           |       | Output of channel 3 |

|           |       | 00: No output       |

| OUT3[1:0] | 00    | 01: low output      |

|           |       | 10: middle output   |

|           |       | 11: high output     |

|           |       | Output of channel 2 |

|           |       | 00: No output       |

| OUT2[1:0] | 00    | 01: low output      |

|           |       | 10: middle output   |

|           |       | 11: high output     |

|           |       | Output of channel 1 |

|           |       | 00: No output       |

| OUT1[1:0] | 00    | 01: low output      |

|           |       | 10: middle output   |

|           |       | 11: high output     |

## Output2 Channel 5 ~ 8 Output Register

OUT7[1:0]

| Address (h | ex): 11h |  |

|------------|----------|--|

| Type: R    |          |  |

| Bit7       | Bit6     |  |

OUT8[1:0]

| Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 |

|------|------|------|------|------|------|

#### Description

The each channel output of TSM12 is compressed with 2 bits. It has 3 level output information that is low, middle and high.

OUT6[1:0]

| Bit name  | Reset | Function            |

|-----------|-------|---------------------|

|           |       | Output of channel 8 |

|           |       | 00: No output       |

| OUT8[1:0] | 00    | 01: low output      |

|           |       | 10: middle output   |

|           |       | 11: high output     |

|           |       | Output of channel 7 |

|           |       | 00: No output       |

| OUT7[1:0] | 00    | 01: low output      |

|           |       | 10: middle output   |

|           |       | 11: high output     |

|           |       | Output of channel 6 |

|           |       | 00: No output       |

| OUT6[1:0] | 00    | 01: low output      |

|           |       | 10: middle output   |

|           |       | 11: high output     |

|           |       | Output of channel 5 |

|           |       | 00: No output       |

| OUT5[1:0] | 00    | 01: low output      |

|           |       | 10: middle output   |

|           |       | 11: high output     |

Bit0

OUT5[1:0]

# Output3 Channel 9~ 12 Output Register

| Address | (hex): | 12 | h |

|---------|--------|----|---|

| Type: R |        |    |   |

| Type: R |        |      |        |      |        |      |        |

|---------|--------|------|--------|------|--------|------|--------|

| Bit7    | Bit6   | Bit5 | Bit4   | Bit3 | Bit2   | Bit1 | Bit0   |

| OUT1:   | 2[1:0] | OUT1 | 1[1:0] | OUT1 | 0[1:0] | OUTS | 9[1:0] |

#### Description

The each channel output of TSM12 is compressed with 2 bits. It has 3 level output information that is low, middle and high.

| Bit name   | Reset | Function             |

|------------|-------|----------------------|

|            |       | Output of channel 12 |

|            |       | 00: No output        |

| OUT12[1:0] | 00    | 01: low output       |

|            |       | 10: middle output    |

|            |       | 11: high output      |

|            |       | Output of channel 11 |

|            |       | 00: No output        |

| OUT11[1:0] | 00    | 01: low output       |

|            |       | 10: middle output    |

|            |       | 11: high output      |

|            |       | Output of channel 10 |

|            |       | 00: No output        |

| OUT10[1:0] | 00    | 01: low output       |

|            |       | 10: middle output    |

|            |       | 11: high output      |

|            |       | Output of channel 9  |

|            |       | 00: No output        |

| OUT9[1:0]  | 00    | 01: low output       |

|            |       | 10: middle output    |

|            |       | 11: high output      |

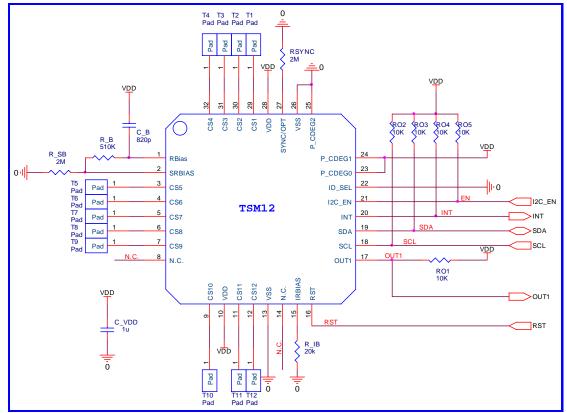

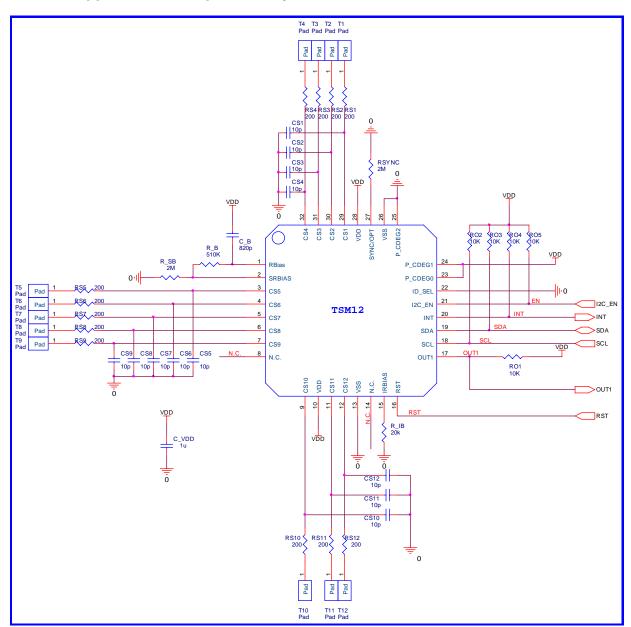

## 10 Recommended Circuit Diagram

#### 10.1 Application Example in clean power environment

TSM12 Application Example Circuit (Clean power environment)

- In PCB layout, R\_B should not be placed on touch pattern. If not, C\_B has to be connected. The R\_B pattern should be routed as short as possible.

- The CS patterns also should be routed as short as possible and the width of line might be about 0.25mm.

- The capacitor that is between VDD and GND is an obligation. It should be located as close as possible from TSM12.

- + The CS pattern routing should be formed by bottom metal (opposite metal of touch PAD).

- The empty space of PCB must be filled with GND pattern to strengthen GND pattern and to prevent external noise from interfere with sensing frequency.

- The TSM12 is reset if RST Pin is high. (See 6.5 Reset implementation chapter)

- The TSM12 is working with single output mode if the SYNC/OPT pin is high and it will be in multi output mode when it's low. The resistor which is connected with GND should be connected with SYNC pin when the application is required over two TSM12 devices (Multi output mode).

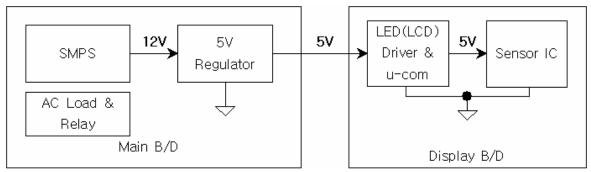

10.2 Application Example in noisy environment

TSM12 Application Example Circuit (Noisy environment)

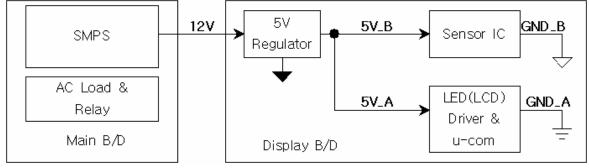

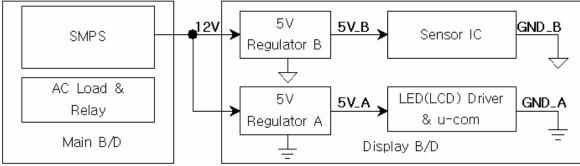

- The VDD periodic voltage ripple over 50mV and the ripple frequency is lower than 10 kHz can cause wrong sensitivity calibration. To prevent above problem, power (VDD, GND) line of touch circuit should be separated from other circuit. Especially LED driver power line or digital switching circuit power line certainly should be treated to be separated from touch circuit.

- The smaller R\_B is recommended in noisy environments.

## 10.3 Example - Power Line Split Strategy PCB Layout

#### A. Not split power Line (Bad power line design)

- ♣ The noise that is generated by AC load or relay can be loaded at 5V power line.

- A big inductance might be appeared in case of the connection line between main board and display board is too long, moreover the voltage ripple could be generated by LED (LCD) display driver at VDD (5V).

#### B. Split power Line (One 5V regulator used) – Recommended

## C. Split power Line (Separated 5V regulator used) – Strongly recommended

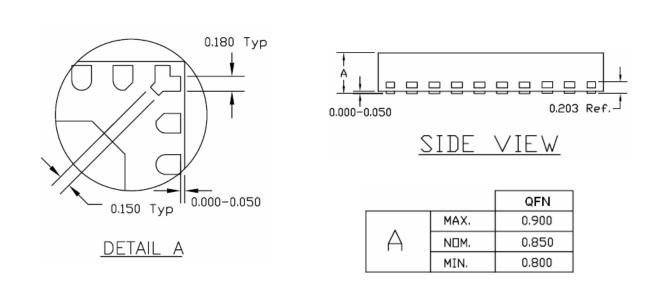

NOTE: Dimensions are in millimeters

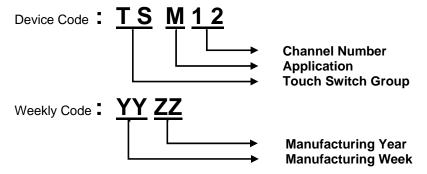

# **12 MARKING DESCRIPTION**

LIFE SUPPORT POLICY

touchSEMI PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES NOR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF THE EPSILLON COMPANY. touchSEMI IS MEMBER OF EPSILLON COMPANY.

touchSEMI Sales Office

www.touchsemi.com

Tel.: (+420) 212247491 Fax: (+420) 212247466

Na mokrině 45, 130 00 Prague 3 Czech Republic, EU