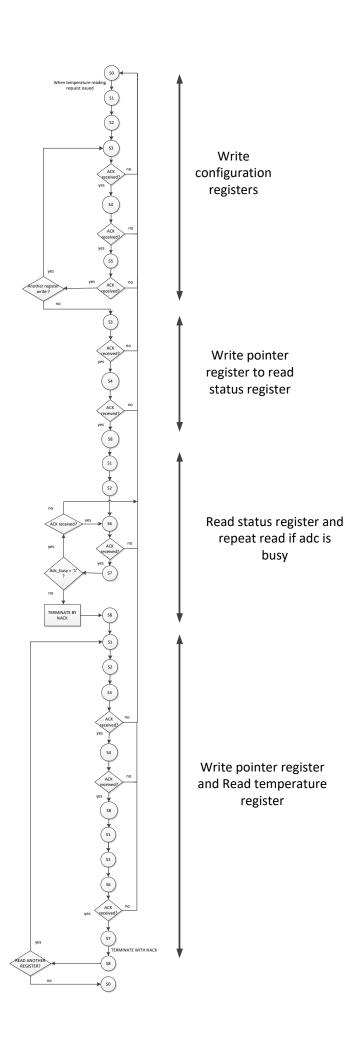

Below is the diagram describing the design flow. It is a state machine with the following 8 states.

SO: SDA = '1', SCLK = '1'

**S1: START CONDITION**

S2: SWITCH TO HS-MODE - 0000 1XXXX

S3: SLAVE ADDRESSS AND WRITE BIT

1001 1100, expects an ACK in 9<sup>th</sup> clock cycle

S4: POINTER REGISTER BYTE, expects an ACK in 9<sup>th</sup> clock cycle

S5: WRITE THE CONFIGURATION REGISTER

S6: SLAVE ADDRESSS AND READ BIT

1001 1101, expects an ACK in 9th clock cycle

S7: READ THE REGISTER VALUE, in the 9<sup>th</sup> clock cycle, issues nack to terminate read otherwise expects ack to continue reading the same register

**S8: STOP CONDITION**

The Configuration registers are written initially and then the status register is checked to see the status of adc. If adc is busy then repeat the read of the status register else, read the temperature registers.