# PARADE TECHNOLOGIES INC.

TEL: 408-329-5540 FAX: 408-329-5541 Email: sales@paradetech.com Website: www.paradetech.com

PS8811

# USB 3.1 Gen 2 10Gbps Retimer with DCI Support

V1.0

Aug. 14, 2018

#### Notice

All information provided in this document is on an "AS IS" basis without any guarantee or warranty. Information in this document is provided in relation to Parade products and is subject to change without notice. No intellectual rights or licenses are implied.

Do Not Distribute Without Permission

#### **KEY FEATURES**

- Supports USB 3.1 Gen 2 10Gbps retiming

- Supports USB 3.1 full power management with automatic power saving

- CrystalFree no external crystal or clock needed

- High input jitter tolerance and low output jitter

- UniEye™ Adaptive Equalizer to compensate channel loss

- Very low latency

- DCI support

- Low power consumption

- Ultra low standby power

- 4.2x4.2 mm 36-pin QFN Halogen free RoHS

Package

- 3.3V and 1.2V power supply

- ESD: 7kV Human Body Mode

#### **APPLICATIONS**

- Notebook/PCs

- · Tablets and mobile devices

- Docking stations and active cables

#### DESCRIPTION

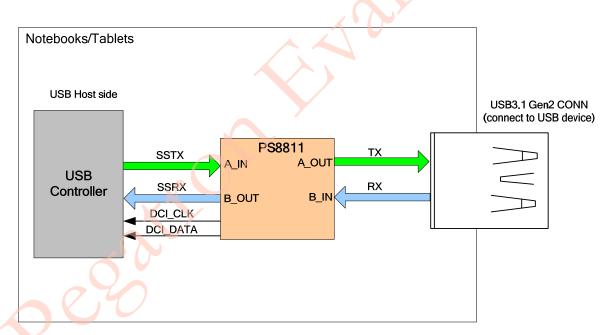

PS8811 is a one-port bidirectional USB 3.1 Gen 2 retimer that integrates the UniEye equalizer and retimer to re-condition USB 3.1 signals for long media link application. It supports USB 3.1 Gen 2 with operation speed up to 10Gbps as well as Gen 1 operation at 5Gbps.

PS8811 supports Intel DCI (Direct Connect Interface) for closed chassis debugging over USB port.

#### **Retiming/Redriving mode for USB3.1**

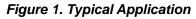

PS8811 supports retiming operation mode for USB3.1. It includes clock and data recovery (CDR) circuit and automatically locks its internal clock to the incoming data by detecting its data stream bit transactions. By removing jitter frequency out of the PLL bandwidth, the CDR circuit reduces the output jitter and allows PS8811 to achieve the excellent jitter performance in retiming mode.

For USB 3.1 Gen 1 and Gen 2 data rates, PS8811 is configured to support retiming for Gen 2 speed and redriving for Gen 1 speed. Gen 1 and Gen 2 speeds are automatically detected.

#### **Receiver Equalization**

PS8811 implements equalizers for all USB 3.1 receiving channels, offering outstanding performance for different PCB trace or cable lengths. PS8811 is capable of working for a variety of systems with different input PCB trace and cable conditions, providing signal compensation and regenerating high quality signals with minimal timing jitter.

#### **Programmable Transmitter Equalization**

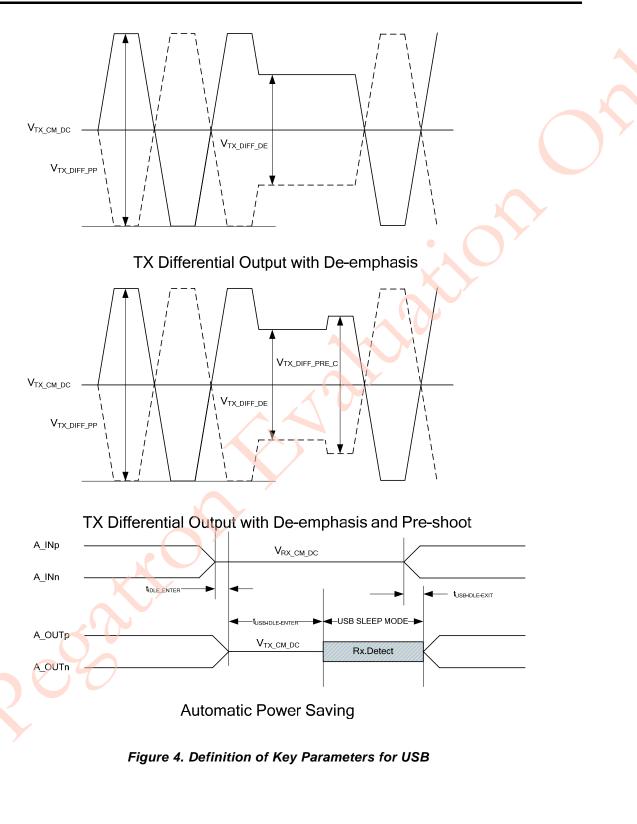

PS8811 supports programmable transmitter equalization for all USB 3.1 output channels. A two-tap Tx equalization (De-emphasis) is used for Gen 1 speed, and a three-tap Tx equalizer including De-emphasis and Pre-shoot is applied for Gen 2 speed.

#### **Automatic Squelch**

PS8811 implements automatic squelch circuitry internally, which will drive the output to the common mode voltage when input signals fall below the threshold level at the input of each channel. PS8811 also implements the USB power saving features.

#### **DCI Support**

PS8811 has built-in level shifters and supporting circuitry for DCI debugging. Integrator can control DCI\_EN pin to enable or disable auto DCI feature for implementation.

#### **Power Management**

PS8811 has very low standby power, which is essential to battery-operated devices such as notebooks and tablets.

Power states that PS8811 supports are described below:

- Standby mode

PS8811 enters into standby mode to consume the least power whenever the EN pin is de-asserted.

- Idle mode

Upon assertion of EN signal, PS8811 will exit from standby mode and enter idle mode.

In the idle mode, the USB channels of PS8811 are at Rx.Detect state to check for the existence of a USB 3.1 device, and will exit from idle mode upon successful detection of far-end termination from a USB device.

#### - USB Sleep mode

At USB link idle(U3 state), when the input signal amplitude on USB channel falls below the squelch threshold level for longer than a pre-defined period, the USB channel will be powered down; thereafter the channel will enter sleep mode. Upon valid signal detection, PS8811's USB channel will go back to the normal operation mode immediately.

- Normal Operation (Active) Mode

In this mode, PS8811 is fully operational.

# FUNCTIONAL BLOCK DIAGRAM

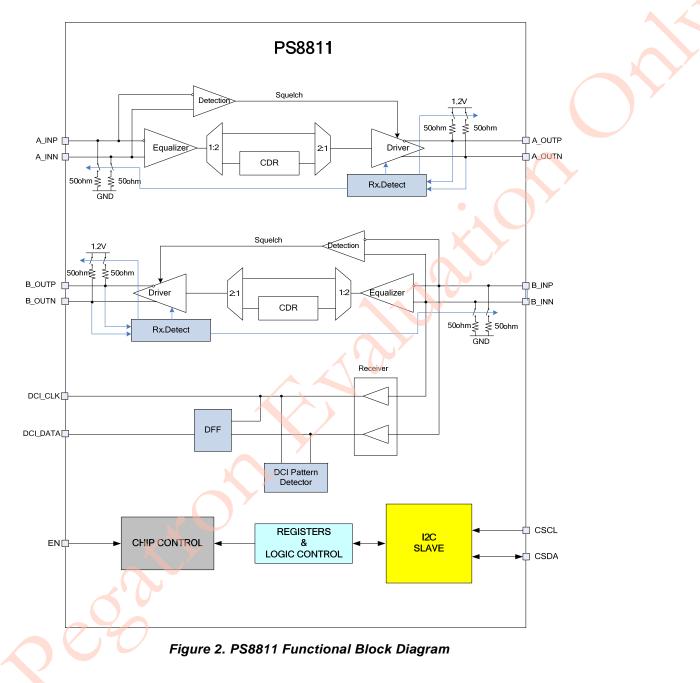

#### **PIN ASSIGNMENT & DESCRIPTION: PS8811**

Figure 3. PS8811 Pin Assignment (Top View)

| Pin   | Name                        | I/O | Description                                                                              |

|-------|-----------------------------|-----|------------------------------------------------------------------------------------------|

| 2,3   | A_INP                       | I   | HOST facing port USB SuperSpeed/SuperSpeedPlus differential input                        |

|       | A_INN                       |     |                                                                                          |

| 8,9   | B_OUTP                      | 0   | HOST facing port USB SuperSpeed/SuperSpeedPlus differential output                       |

|       | B_OUTN                      |     |                                                                                          |

| 27,26 | A_OUTP                      | 0   | Connector facing port USB SuperSpeed/SuperSpeedPlus differential output                  |

|       | A_OUTN                      |     |                                                                                          |

| 21,20 | B_INP                       | Ι   | Connector facing port USB SuperSpeed/SuperSpeedPlus differential input                   |

|       | B_INN                       |     |                                                                                          |

| 11    | EN                          | Ι   | Chip enable, active high, 3.3V input. Internal pull-down at $150 k\Omega$ .              |

| 29    | REXT                        | I/O | External resistor for output swing adjustment.                                           |

|       |                             |     | Connected to a 4.99k $\Omega$ resistor for normal output swing.                          |

| 33,32 | CSCL                        | I/O | CSCL /CSDA are local I <sup>2</sup> C control bus: Clock and Data. Open drain structure. |

|       | CSDA                        |     | 3.3V tolerant.                                                                           |

|       |                             |     | PS8811 supports I <sup>2</sup> C operation speed up to 1MHz.                             |

| 16    | RESET#                      | I   | Reset. Active low, 3.3V input. Internal pull-up at ~100kΩ.                               |

| 6     | DCI_CLK                     | 0   | CLK signal output of DCI interface. Tolerant to VDDIO.                                   |

| 7     | DCI_DATA                    | 0   | DATA signal output of DCI interface. Tolerant to VDDIO.                                  |

| 36,35 | ADDR0                       | I   | I <sup>2</sup> C address setting. Internal pull down at 150kΩ, 3.3V I/O.                 |

|       | ADDR1                       |     | [ADDR1,ADDR0]=                                                                           |

|       |                             |     | LL: 0x50~0x53 (default)                                                                  |

|       |                             |     | LH: 0x54~0x57                                                                            |

|       |                             |     | HL: 0xE0~0xE3                                                                            |

|       |                             |     | HH: 0xE4~0xE7                                                                            |

| 12    | DCI_EN                      |     | Auto DCI enable or disable control. Internally tied to VDD33/2, 3.3V I/O.                |

|       | X                           |     | L: Disable                                                                               |

|       |                             |     | M: Disable(Default)                                                                      |

|       |                             |     | H: Enable                                                                                |

| 15    | BDE                         | I   | In pin control mode, this pin is used as USB HOST facing Tx channel                      |

|       | $(\mathcal{O},\mathcal{V})$ |     | De-emphasis setting; 3-state input.                                                      |

|       |                             |     | Internally tied to VDD33/2, 3.3V I/O.                                                    |

|       |                             |     | L: 0dB                                                                                   |

|       |                             |     | M: -3.5dB (default)                                                                      |

|       |                             |     | H: -6.0dB                                                                                |

|       |                             |     | In I2C mode, this pin has higher priority; it should be disabled before register         |

|       |                             |     | setting.                                                                                 |

| 25    | AEQ                         | I   | In Pin Control mode, this pin is used for USB HOST facing Rx channel                     |

|       |                             |     | receiver equalization setting; 3-state input. Internally tied to VDD33/2, 3.3V           |

#### Table 1. PS8811 Pin Descriptions

TEL: 408-329-5540 FAX: 408-329-5541 Email: Sales@paradetech.com

For Customer Internal Use Only

|        |        |   | I/O.                                                                             |

|--------|--------|---|----------------------------------------------------------------------------------|

|        |        |   | L: Compensation for channel loss up to 10.5dB                                    |

|        |        |   | M: Compensation for channel loss up to 13dB (default)                            |

|        |        |   | H: Compensation for channel loss up to 19dB                                      |

|        |        |   | In I2C mode, this pin has higher priority; it should be disabled before register |

|        |        |   | setting.                                                                         |

| 14     | BEQ    | 1 | In Pin Control mode, this pin is used as USB connector facing Rx channel         |

| 14     | DEQ    | 1 | receiver equalization setting; 3-state input. Internally tied to VDD33/2, 3.3V   |

|        |        |   |                                                                                  |

|        |        |   | L: Compensation for channel loss up to 10.5dB                                    |

|        |        |   | M: Compensation for channel loss up to 12dB (default)                            |

|        |        |   | H: Compensation for channel loss up to 18dB                                      |

|        |        |   | In I2C mode, this pin has higher priority; it should be disabled before register |

|        |        |   | setting.                                                                         |

| 17     | TEST   |   | Test Mode control; NC for normal operation                                       |

| 30     | MODE   |   | Operation mode:                                                                  |

| 30     | MODE   | 1 |                                                                                  |

|        |        |   | L: 5G redriver mode, 10G retimer mode, adaptive EQ.                              |

|        |        |   | M: 5G redriver mode, 10G retimer mode, fixed EQ (default).<br>H: Reserve         |

| F      |        |   |                                                                                  |

| 5      | VDDDCI | Ρ | Power supply for DCI Interface in a range of 1.8V ~ 3.3V.                        |

| 0.4    |        | - | Connect to VDD33 if DCI is not used.                                             |

| 34     | VDDD   | P | Connect to external 1.2V power supply                                            |

| 10,19, | VDDM   | Р | Connect to external 1.2V power supply                                            |

| 28     |        |   |                                                                                  |

| 4      | VDDAX  | Р | Connect to external 1.2V power supply                                            |

| 24     | VDDAA  | Р | Connect to external 1.2V power supply                                            |

| 22     | VDDBX  | Р | Connect to external 1.2V power supply                                            |

| 23     | VDDBA  | Р | Connect to external 1.2V power supply                                            |

| 1,18   | VDD33  | Р | Connect to external 3.3V power supply                                            |

|        |        |   | I/O supply                                                                       |

| 13,31  | GND    |   | Ground                                                                           |

|        | ePAD   |   | Ground                                                                           |

#### ABSOLUTE MAXIMUM RATINGS

| Parameters                        | Comments             | Unit             |

|-----------------------------------|----------------------|------------------|

| Supply Voltage Range, VDD33       |                      | -0.5 V to 3.6 V  |

| Supply Voltage Range, VDD_xx      |                      |                  |

| (VDDD, VDDM, VDDAX, VDDAA, VDDBX, |                      | -0.5 V to 1.32 V |

| VDDBA)                            |                      |                  |

| Normal I/O Voltage Range          |                      | -0.5 V to 3.6 V  |

| ESD                               | Human Body Mode:     | +/- 7000V        |

|                                   | Machine Mode:        | +/- 400          |

|                                   | Charged Device Mode: | +/- 2000V        |

ESD Standard:

Human Body Model: JS-001-2012

Machine Model: JESD22-A115-C

Charged Device Model: JESD22-C101-E

Latch-up Standard: JESD78D; I-Test: +/- 200mA; V-Test: 1.5X of Vcc

## NORMAL OPERATING CONDITIONS AND POWER CONSUMPTION

| Parameter                              | Conditions    | Min  | Тур | Max  | Unit |

|----------------------------------------|---------------|------|-----|------|------|

| Supply Voltage, VDD33                  |               | 3.0  | 3.3 | 3.6  | V    |

| Supply Voltage, VDD_xx                 |               | 1.14 | 1.2 | 1.26 | V    |

| (VDDD, VDDM, VDDAX, VDDAA, VDDBX,      |               |      |     |      |      |

| VDDBA )                                |               |      |     |      |      |

| Ambient Temperature, Ta                |               | 0    |     | 85   | °C   |

| Junction Temperature, Tj               |               | 0    |     | 125  | °C   |

| USB Active Mode                        | VDD_xx=1.2V   |      |     |      |      |

|                                        | VDD33=3.3V    |      |     |      |      |

|                                        | REXT = 4.99KΩ |      | •   |      | ~    |

|                                        |               |      |     |      |      |

| Normal Supply Current, IDD             | @VDD_xx       |      | 306 | 367  | mA   |

| @ 10Gbps                               | @VDD33        |      | 23  | 28   | mA   |

| USB Sleep Mode                         |               |      |     |      |      |

| Sleep mode Current, I <sub>sleep</sub> | @VDD_xx       |      | 430 | 650  | uA   |

| (U3 state)                             | @VDD33        |      | 83  | 125  | uA   |

| USB Idle Mode                          |               |      |     |      |      |

| Idle mode Current, I <sub>idle</sub>   |               |      |     |      |      |

| (Far end termination removed)          | @VDD_xx       |      | 1.0 | 2.0  | mA   |

|                                        | @VDD33        |      | 0.2 | 0.5  | mA   |

| Standby Mode                           |               |      |     |      |      |

| Standby Current, Istdby                | @VDD_xx       |      | 0.1 | 1.0  | uA   |

| (EN=L)                                 | @VDD33        |      | 3.2 | 5.0  | uA   |

| Power Consumption                      |               |      |     |      |      |

| USB Active Mode                        |               |      | 443 | 533  | mW   |

| Power Consumption                      |               |      |     |      |      |

| USB Sleep Mode                         |               |      | 0.8 | 1.2  | mW   |

| USB Idle Mode                          |               |      | 1.9 | 4.1  | mW   |

| Power Consumption                      |               |      |     |      |      |

| Standby Mode                           |               |      |     | 18   | uW   |

# PACKAGE DISSIPATION RATING

| 36-pin QFN                                             | Still air, 4-layer PCB |

|--------------------------------------------------------|------------------------|

| $\theta_{JA}$ – Junction to Ambient Thermal Resistance | 45°C/W                 |

| $\theta_{JC}$ – Junction to Case Thermal Resistance    | 25°C/W                 |

| Maximum Power Dissipation Rating, Ta = 85 °C           | 889mW                  |

#### **DC CHARACTERISTICS**

|                      | Parameter                                   | Test Conditions               | Min | Typ <sup>d</sup> | Мах   | Unit |  |  |

|----------------------|---------------------------------------------|-------------------------------|-----|------------------|-------|------|--|--|

| Control              | Control pins (3.3V I/O):ADDR0,ADDR1         |                               |     |                  |       |      |  |  |

| VIH I                | LVTTL input High-level voltage              |                               | 2   |                  | VDD33 | V    |  |  |

| VIL I                | LVTTL input Low-level voltage               |                               | GND |                  | 0.8   | V    |  |  |

| Ін  І                | Input High-level current                    | V <sub>IH</sub> = 2V to VDD33 |     |                  | 40    | μA   |  |  |

| I <sub>IL</sub>   I  | Input Low-level current                     | $V_{IL}$ = GND to 0.8V        |     |                  | 10    | μΑ   |  |  |

| Control              | Control pins (3.3V I/O): EN                 |                               |     |                  |       |      |  |  |

| VIH I                | LVTTL input High-level voltage              |                               | 2   |                  | 3.6   | V    |  |  |

| VIL I                | LVTTL input Low-level voltage               |                               | GND |                  | 0.8   | V    |  |  |

| I <sub>IH</sub>      | Input High-level current                    | V <sub>IH</sub> = 2V to 3.6V  |     |                  | 50    | μA   |  |  |

| lı⊾  I               | Input Low-level current                     | V <sub>IL</sub> = GND to 0.8V |     |                  | 30    | μA   |  |  |

| Control              | I <sup>2</sup> C Pins: CSDA, CSCL(3.3V I/O) | •                             |     |                  | Y     |      |  |  |

| V <sub>IH</sub> I    | High-level input voltage                    |                               | 1.6 |                  | 3.6   | V    |  |  |

| VIL I                | Low-level input voltage                     |                               | GND |                  | 1     | V    |  |  |

| V <sub>OL</sub> I    | Low-level output voltage                    | I <sub>OL</sub> = 8 mA        | GND |                  | 0.4   | V    |  |  |

| Resistor             | Resistors                                   |                               |     |                  |       |      |  |  |

| REXT                 | External reference resistor                 |                               | 0   | 4.99             |       | kΩ   |  |  |

| <b>R</b> RX-TERM     | Differential input termination resistor     |                               |     | 100              |       | Ω    |  |  |

| R <sub>TX-TERM</sub> | Differential output termination resistor    |                               |     | 100              |       | Ω    |  |  |

$^{\rm d}$  All typical values are measured at 25 °C and 3.3V / 1.2V power supply.

#### **AC CHARACTERISTICS**

| Parameter                                                                          | Test Conditions          | Min | Тур | Max   | Unit |

|------------------------------------------------------------------------------------|--------------------------|-----|-----|-------|------|

| USB Receiver                                                                       |                          |     |     |       |      |

| $V_{\text{RX\_EYE\_HEIGHT}}\text{Rx}$ input signal eye height                      | After Ref. Rx EQ @10Gbps | 70  |     |       | mV   |

| Tj <sub>Rx</sub> Rx input total jitter                                             | After Ref. Rx EQ @10Gbps |     |     | 0.671 | UI   |

| R <sub>RX_HIZ</sub> Rx high impedance                                              |                          | 10  |     |       | kΩ   |

| R <sub>RX_DC_CM</sub> Rx DC common mode impedance                                  |                          | 18  |     | 30    | Ω    |

| R <sub>RX_DIFF_DC</sub> Rx DC differential impedance                               |                          |     | 100 |       | Ω    |

| V <sub>RX_CM_DC</sub> Rx common mode voltage                                       |                          |     | 0   |       | V    |

| $V_{\text{RX\_LFPS\_DETLFPS}}$ signal detection threshold                          |                          | 100 |     | 300   | mV   |

| $t_{\mbox{USB-IDLE-ENTER}}$ Bus idle time before entering USB Idle                 |                          |     |     | 450   | ms   |

| mode                                                                               |                          |     |     |       |      |

| $t_{\mbox{USB-IDLE-EXIT}}$ USB Idle mode to normal operation exit                  |                          |     |     | 150   | ns   |

| time                                                                               | •                        |     |     |       |      |

| USB Transmitter                                                                    |                          |     |     |       |      |

| $V_{\text{TX\_DIFF\_PP}}$ Differential peak to peak output voltage                 | RLOAD=100Ω               | 800 |     | 1200  | mV   |

|                                                                                    | REXT = 4.99KΩ            |     |     |       |      |

| $R_{\text{TX\_DIFF\_DC}}DC$ differential impedance                                 | Normal operation         |     | 100 |       | Ω    |

| $V_{\text{TX}\_\text{CM}\_\text{DC}}$ Tx common mode voltage                       |                          |     |     | 1.2   | V    |

| $V_{\text{TX\_CM\_AC}}$ Tx AC common mode voltage                                  |                          |     |     | 100   | mVpp |

| $t_{\text{RISE}\text{/}}t_{\text{FALL}}Tx$ output 20% to 80% rise time / fall time |                          |     | 50  |       | ps   |

| T <sub>SKEW_INTRA</sub> Tx output intra-pair skew                                  |                          |     |     | 10    | ps   |

| t <sub>PROPAGATION</sub> Differential propagation delay                            |                          |     | 2.1 |       | ns   |

| Reation                                                                            |                          |     |     |       |      |

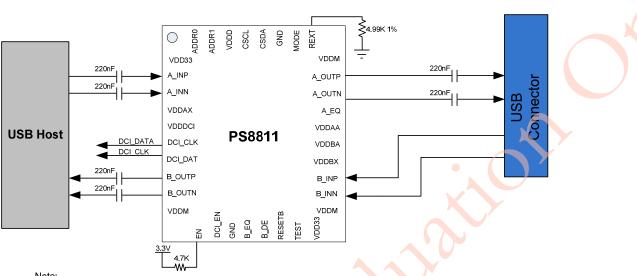

# **TYPICAL APPLICATION DIAGRAM**

Note:

1. Connect VDDD/VDDM/VDDAX/VDDAA/VDDBX/VDDBA to 1.2V Power supply. Connect VDD33 to 3.3V power supply. Connect VDDDCI to 3.3V if DCI is not used. Connect EPAD to GND. 2. For High speed signals connection, A INP/A INN & B\_OUTP/B\_OUTN should have to connect to Host side and A\_OUTP/A\_OUTN & B\_INP/B\_INN should have to connect to Connector side.

Figure 5. Typical Application Diagram

#### LAYOUT GUIDELINES

#### High Speed Interfaces

- Select proper PCB stack up and trace width at 85 Ω differential transmission line impedance for the high speed USB signals

- Avoid tight bends for the high speed USB signals

- Match intra-pair traces length within each differential pair

- Keep uninterrupted ground plane beneath USB signals

- Keep wide and shortest traces for both power and ground path to PS8811

#### **Filtering Capacitors**

Place 0.1 uF, 0.01 uF decoupling capacitors close to each power pin

#### **Analog Current Bias Resistor**

Place a 4.99k Ω 1% precision resistor close to REXT pin and connect to GND solidly

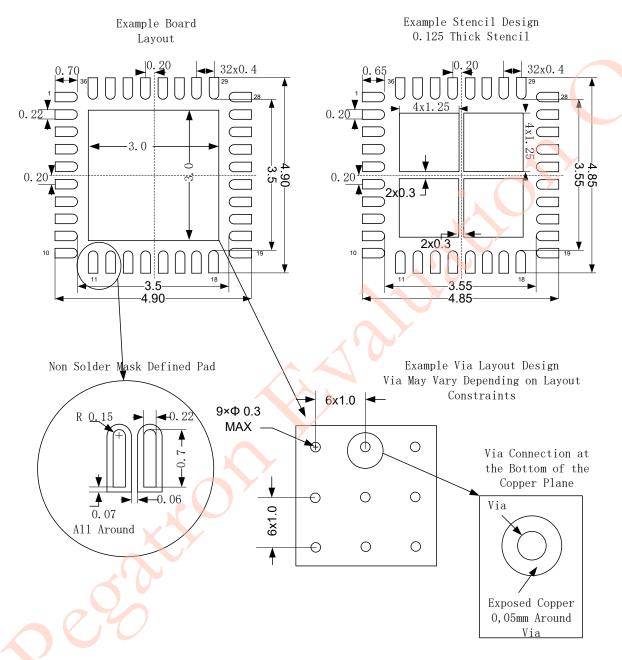

#### PAD LAYOUT PATTERN GUIDELINES: 36-PIN 4.2x4.2mm QFN

#### NOTES:

- 1. All dimensions are in millimeters.

- 2. The drawing is subject to change without notice.

- 3. Customers should contact their board fabrication site for recommend solder mask tolerances and via tenting recommendations for vias placed in the thermal pad.

#### Figure 6. Exposed Thermal Pad Layout Guidelines for PS8811

TEL: 408-329-5540 FAX: 408-329-5541 Email: Sales@paradetech.com For Customer Internal Use Only

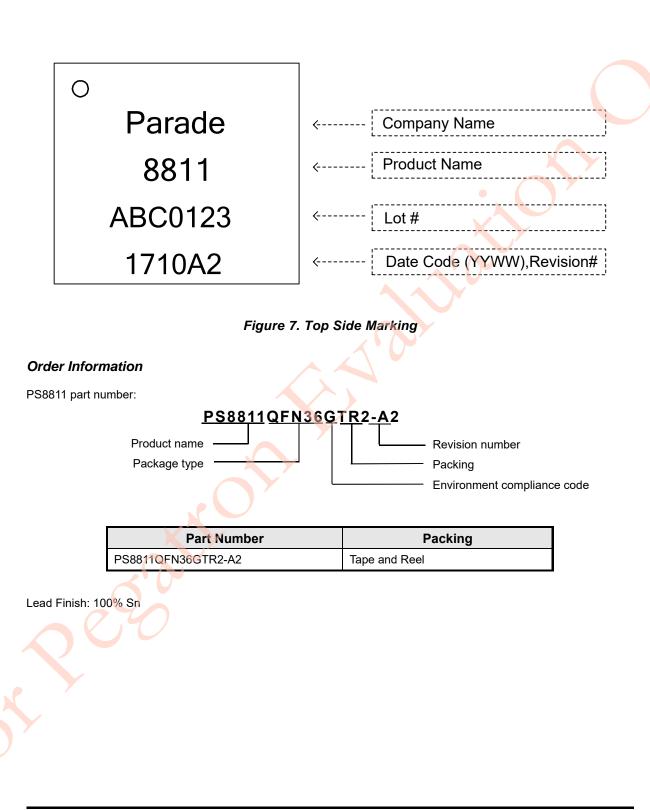

#### **ORDER & PACKAGING INFORMATION**

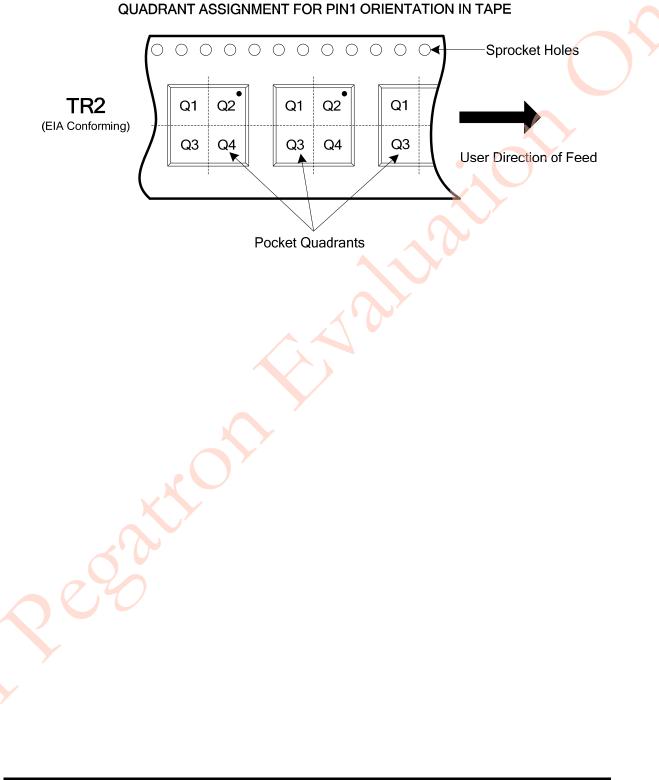

#### TAPE AND REEL PACKING PIN1 ORIENTATION

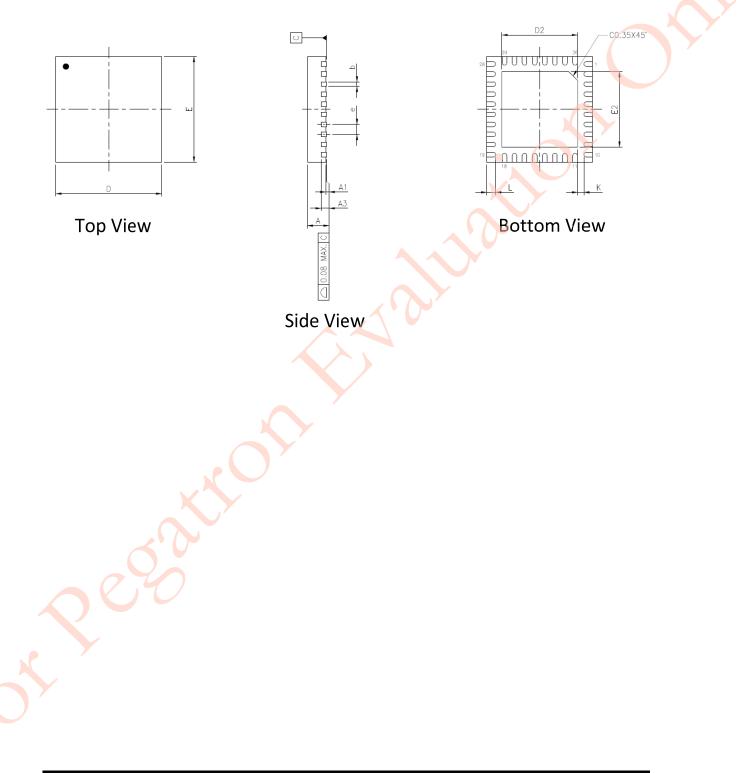

# PHYSICAL DIMENSION

# 36-pin QFN 4.2x4.2 mm<sup>2</sup>

#### PS8811 USB 3.1 Gen 2 10Gbps Retimer with DCI Support

| Parameter | MIN   | NOM          | MAX   | Unit |

|-----------|-------|--------------|-------|------|

| А         | 0.700 | 0.750        | 0.800 | mm   |

| A1        | 0.000 | 0.02         | 0.050 | mm   |

| A3        |       | mm           |       |      |

| b         | 0.150 | 0.200        | 0.250 | mm   |

| D         | 4.10  | 4.20         | 4.30  | mm   |

| D2        | 2.95  | 3.00         | 3.05  | mm   |

| E         | 4.10  | 4.20         | 4.30  | mm   |

| E2        | 2.95  | 95 3.00 3.05 |       | mm   |

| е         |       | mm           |       |      |

| К         | 0.20  |              | •     | mm   |

| L         | 0.30  | 0.35         | 0.40  | mm   |

TEL: 408-329-5540 FAX: 408-329-5541 Email: Sales@paradetech.com

## **REVISION HISTORY**

| Version     | Date       | Items                                                                                                                      |

|-------------|------------|----------------------------------------------------------------------------------------------------------------------------|

| Preliminary | 2017/07/25 | Initial release                                                                                                            |

| V0.7        | 2017/09/25 | Update PACKAGE DISSIPATION RATING<br>Update AC/DC characteristic<br>Update power consumption                               |

| V0.9        | 2018/05/14 | Update Power consumption<br>Update DCI description<br>Update PAD layout guidelines<br>Update order & packaging information |

| V1.0        | 2018/08/14 | Update order & packaging information<br>Update Pin description and change ADE to DCI_EN<br>Updated Power consumption       |