| REVISIONS                                                                                                                                                  |             |                                                   |                               |        |                |                                             |                                                                      |                                        |   |       |                  |                      |                                |                                        |                                                    |                                                |                             |                                              |                                    |                                   |              |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------------------------------|-------------------------------|--------|----------------|---------------------------------------------|----------------------------------------------------------------------|----------------------------------------|---|-------|------------------|----------------------|--------------------------------|----------------------------------------|----------------------------------------------------|------------------------------------------------|-----------------------------|----------------------------------------------|------------------------------------|-----------------------------------|--------------|-----|

| LTR                                                                                                                                                        |             |                                                   |                               |        |                | DE                                          | SCRIP                                                                | TION                                   |   |       |                  |                      |                                | D                                      | ATE (                                              | YR-M                                           | D-DA)                       |                                              | /                                  | APPRO                             | OVED         |     |

| A                                                                                                                                                          | Rem         | ove pa                                            | aramet                        | ers wi | th typic       |                                             | ues fro                                                              |                                        |   | - TTM | 1                |                      |                                |                                        |                                                    | -05-20                                         |                             |                                              |                                    |                                   | A. Ak        | oar |

| THE ORIGINAI<br>Revision Status                                                                                                                            | L FIRS      | T SHE                                             |                               |        |                |                                             |                                                                      |                                        |   |       |                  |                      |                                |                                        |                                                    |                                                |                             |                                              |                                    |                                   |              |     |

| REV                                                                                                                                                        | A           | A                                                 | A                             |        |                |                                             |                                                                      |                                        |   |       |                  |                      |                                |                                        |                                                    |                                                |                             |                                              |                                    |                                   |              |     |

| SHEET                                                                                                                                                      | 23          | 24                                                | 25                            |        |                |                                             |                                                                      |                                        |   |       |                  |                      |                                |                                        |                                                    |                                                |                             |                                              |                                    |                                   |              |     |

| REV                                                                                                                                                        | Α           | Α                                                 | Α                             | Α      | Α              | Α                                           | A                                                                    | Α                                      | A | Α     | Α                | Α                    | A                              | А                                      | Α                                                  | А                                              | Α                           | Α                                            | Α                                  | Α                                 | Α            | A   |

| SHEET                                                                                                                                                      | 1           | 2                                                 | 3                             | 4      | 5              | 6                                           | 7                                                                    | 8                                      | 9 | 10    | 11               | 12                   | 13                             | 14                                     | 15                                                 | 16                                             | 17                          | 18                                           | 19                                 | 20                                | 21           |     |

| PMIC N/A<br>STANDARD<br>MICROCIRCUIT<br>DRAWING<br>THIS DRAWING IS AVAILABLE<br>FOR USE BY ALL DEPARTMENTS<br>AND AGENCIES OF THE<br>DEPARTMENT OF DEFENSE |             |                                                   |                               |        |                |                                             |                                                                      |                                        |   |       |                  |                      |                                |                                        |                                                    |                                                |                             |                                              |                                    |                                   | 22           |     |

| MICE<br>DI<br>THIS DRAV<br>FOR USE BY<br>AND AG                                                                                                            | ROCI<br>RAW | IRCU<br>/ING<br>IS AVA<br>DEPAF<br>ES OF          | JIT<br>AILABL<br>RTMEN<br>THE | NTS    | CH             | Tays<br>ECKE<br>Tays<br>PROV<br>Muh         | sa Mar<br>'ED BY<br>namma<br>G APP                                   | kus<br>kus<br>d Akb                    |   | ſE    | IMN<br>PH        | RO(<br>IUNI          | https<br>CIRC<br>TY, 1<br>AL L | <b>OLUI</b><br>:://wv<br>UIT,<br>10/10 | WBUS<br>WW.dl<br>RAC                               | <b>S, OF</b><br>a.mi<br>0IATI<br>00 M          | IIO<br>/Lan<br>ON I<br>1B/S | HARIT<br>43218<br>Idano<br>HAR<br>ETH<br>ER, | 8-399<br>Mar<br>DEN                | <mark>itime</mark><br>IED,<br>NET | HIGH         | 1   |

| MICE<br>DI<br>THIS DRAV<br>FOR USE BY<br>AND AG<br>DEPARTM                                                                                                 | ROCI<br>RAW | IRCU<br>/ING<br>IS AVA<br>DEPAR<br>ES OF<br>DF DE | JIT<br>AILABL<br>RTMEN<br>THE | NTS    | CH<br>AP<br>DR | Tays<br>ECKE<br>Tays<br>PROV<br>Muh<br>AWIN | Sa Mar<br>D BY<br>Sa Mar<br>(ED BY<br>amma<br>G APF<br>21-1<br>N LEV | kus<br>kus<br>d Akb<br>PROV/<br>I 1-10 |   | ſE    | IMN<br>PH<br>SIL | CROC<br>IUNI<br>YSIC | https<br>CIRC<br>TY, 1<br>AL L | <b>OLUI</b><br>:://wv<br>UIT,<br>10/10 | WBU:<br>ww.dl<br>RAC<br>00/10<br>R TR<br>ODE<br>88 | <b>S, OH</b><br>a.mil<br>DIATI<br>00 M<br>RANC | IIO<br>/Lan<br>ON I<br>1B/S | 43218<br>Idano<br>HAR<br>ETH<br>ER,<br>59    | 8-399<br>Mar<br>DEN<br>IERI<br>MOI | <mark>itime</mark><br>IED,<br>NET | HIGH<br>THIC | 1   |

## 1. SCOPE

1.1 <u>Scope</u>. This drawing documents two product assurance class levels consisting of high reliability (device classes Q and M) and space application (device class V). A choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of Radiation Hardness Assurance (RHA) levels is reflected in the PIN.

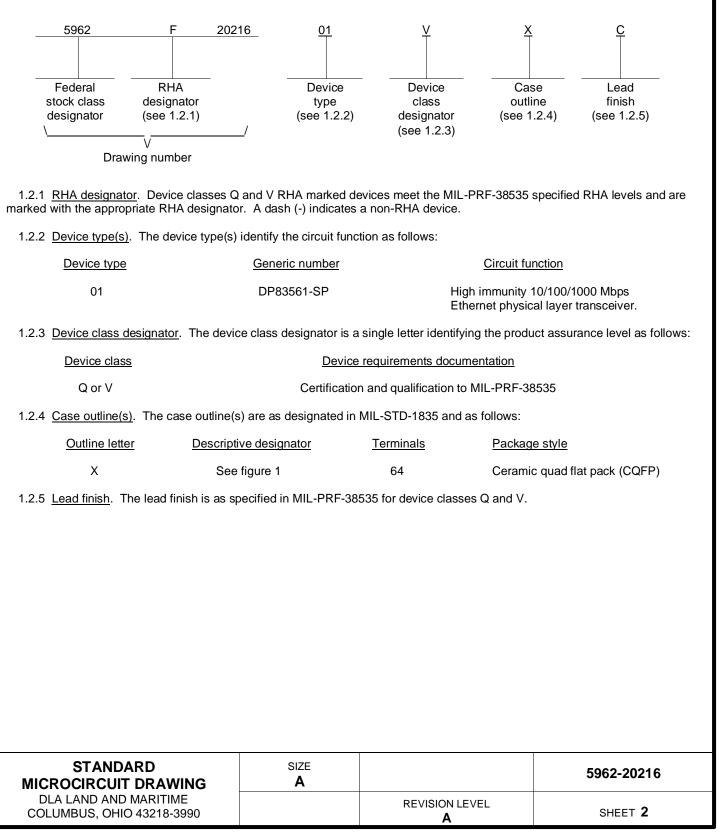

1.2 <u>PIN</u>. The PIN is as shown in the following example:

# 1.3 Absolute maximum ratings. 1/2/3/4/

| Power supply voltage (AVDD 2.5 V)                                | -0.3 to 3.0 V       |

|------------------------------------------------------------------|---------------------|

| Power supply voltage (AVDD 1.8 V)                                | -0.3 to 2.16 V      |

| Power supply voltage (AVDD 1.1 V)                                |                     |

| Power supply voltage (VDDIO 3.3 V option)                        |                     |

| Power supply voltage (VDDIO 2.5 V option)                        |                     |

| Power supply voltage (VDDIO 1.8 V option)                        |                     |

| Maximum junction temperature (TJ)                                |                     |

| Storage temperature range (T <sub>STG</sub> )                    |                     |

| PINS media dependent interface (MDI)                             |                     |

| PINS (MAC interface, MDIO, MDC, GPIO)                            |                     |

| PINS (EN, RESET_N)                                               | -0.3 to VDDIO+0.3 V |

| Electrostatic discharge (ESD) rating: 5/6/                       |                     |

| Human-body model (HBM), All Pins except MDI Pins 2/              | ±2500 V             |

| Human-body model (HBM), MDI Pins                                 |                     |

| IEC 61000-4-2 contact discharge, MDI Pins                        |                     |

| Thermal characteristics: 7/                                      |                     |

| Thermal resistance, junction-to-ambient (RθJA)                   | 22.5°C/W            |

| Thermal resistance, junction-to-case, top (ReJC(top))            |                     |

|                                                                  |                     |

| Thermal resistance, junction-to-case, bottom (ReJC(bot))         |                     |

| Thermal resistance, junction-to-board ( $R_{\theta JB}$ )        |                     |

| Junction-to-top characterization parameter, $(\psi_{\text{JT}})$ | 2°C/W               |

| Junction-to-board characterization parameter ( $\psi_{JB}$ )     | 7.8°C/W             |

|                                                                  |                     |

## 1.4 Recommended operating conditions.

| Power supply voltage (2.5 V analog supply)  | +2.375 V to +2.625 V |

|---------------------------------------------|----------------------|

| Power supply voltage (1.8 V analog supply)  | +1.710 V to +1.890 V |

| Power supply voltage (1.1 V digital supply) | +1.045 V to +1.155 V |

| Power supply voltage (VDDIO 3.3 V option)   | +3.145 V to +3.465 V |

| Power supply voltage (VDDIO 2.5 V option)   | +2.375 V to +2.625 V |

| Power supply voltage (VDDIO 1.8 V option)   | +1.710 V to +1.890 V |

| Operating free air temperature range (TA)   | 55°C to +125°C       |

1/ Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

- 2/ All voltages are measured with respect to ground terminal.

- 3/ Short-circuits can cause excessive heating. Destructive dissipation can result from short-circuits on outputs.

4/ Absolute maximum ratings are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits.

5/ JEDEC document JEP155 states that 500-V HBM allow s safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions. Pins listed as ±8 V and/or ±2 V may actually have higher performance.

6/ JEDEC document JEP157 states that 250-V CDM allow s safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions. Pins listed as ±500 V may actually have higher performance.

<u>7</u>/ For more information about traditional and new thermal metrics, see Texas Instruments IC Package Thermal Metrics application report, SPRA953.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                     | 5962-20216 |

|----------------------------------------------------|------------------|---------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>A | SHEET 3    |

# 1.5 <u>Radiation features</u>. Maximum total dose available (high dose rate = 50 – 300 rad(Si)/s) ...... 300 krads(Si) <u>1</u>/ Heavy ion single event phenomenon (SEP):

No Single event latch-up (SEL) occurs at effective LET (see 4.4.5.3)  $\leq$  121 MeV·cm<sup>2</sup>/mg 2/

2/ Heavy ion single event effects (SEE) test was performed at the TAMU Cyclotron Radiation Effects facility using a superconducting cyclotron and an advanced electron cyclotron resonance (ECR) ion source. No single event latch-up (SEL) was observed under <sup>197</sup>Au ions at angle 43° at Vmax supply voltages and operating temperature 125°C corresponding to an effective LET of 121 MeV·cm<sup>2</sup>/mg. For more information on SEP test results, customers are requested to contact the manufacturer.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                     | 5962-20216     |

|----------------------------------------------------|------------------|---------------------|----------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>A | SHEET <b>4</b> |

<sup>&</sup>lt;u>1</u>/ The manufacturer supplying device type 01 has performed characterization testing in accordance with MIL-STD-883 method 1019, condition A to a maximum total dose of 300 krads(Si). The radiation end points limits for the noted parameters are guaranteed only for the conditions as specified in MIL-STD-883, method 1019, condition A to a maximum total dose of 300 krads(Si).

## 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

## DEPARTMENT OF DEFENSE SPECIFICATION

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

### DEPARTMENT OF DEFENSE STANDARDS

MIL-STD-883 - Test Method Standard Microcircuits. MIL-STD-1835 - Interface Standard Electronic Component Case Outlines.

#### DEPARTMENT OF DEFENSE HANDBOOKS

MIL-HDBK-103 - List of Standard Microcircuit Drawings. MIL-HDBK-780 - Standard Microcircuit Drawings.

(Copies of these documents are available online at https://quicksearch.dla.mil.)

2.2 <u>Non-Government publications</u>. The following document(s) form a part of this document to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

#### ASTM INTERNATIONAL (ASTM)

ASTM F1192 - Standard Guide for the Measurement of Single Event Phenomena (SEP, SEU) Induced by Heavy Ion Irradiation of semiconductor Devices.

(Copies of these documents are available online at https://www.astm.org.)

JEDEC Solid State Technology Association

JEDEC PUB 95 - Registered and Standard Outlines for Semiconductor Devices JEDEC JEP 163 - Selection of burn-in/life test conditions and critical parameters for QML microcircuits

(Copies of these documents are available online at https://www.jedec.org/.)

#### ANSI/ESDA/JEDEC JOINT STANDARD

ANSI/ESDA/JEDEC JS-001 - For Electrostatic Discharge Sensitivity Testing – Human Body Model (HBM) - Component Level. ANSI/ESDA/JEDEC JS-002 - For Electrostatic Discharge Sensitivity Testing – Charged Device Model (CDM) - Device Level.

(Non-Government standards and other publications are normally available from the organizations that prepare of distribute the documents. These documents may also be available in or through libraries or other informational services.)

2.3 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br>A |                     | 5962-20216     |

|----------------------------------------------------|-----------|---------------------|----------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL<br>A | SHEET <b>5</b> |

## 3. REQUIREMENTS

3.1 <u>Item requirements</u>. The individual item requirements for device classes Q and V shall be in accordance with MIL-PRF-38535 as specified herein, or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein.

3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535 and herein for device classes Q and V.

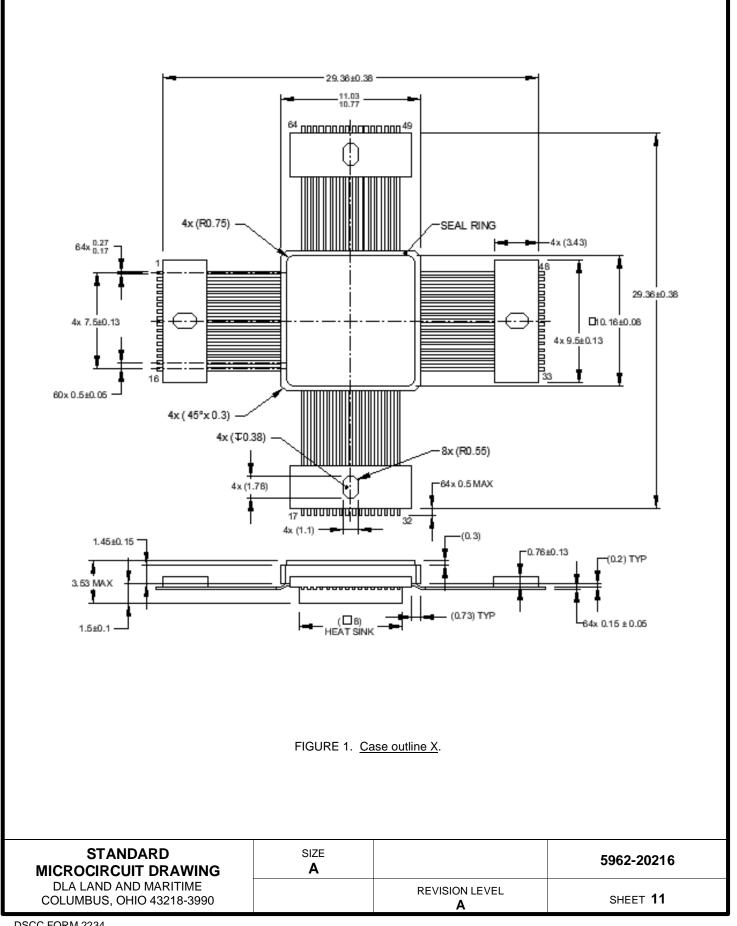

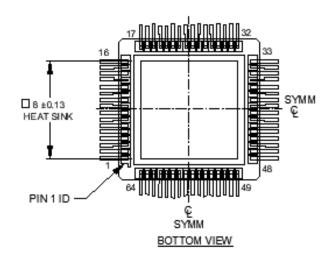

3.2.1 <u>Case outline</u>. The case outline shall be in accordance with 1.2.4 herein and figure 1.

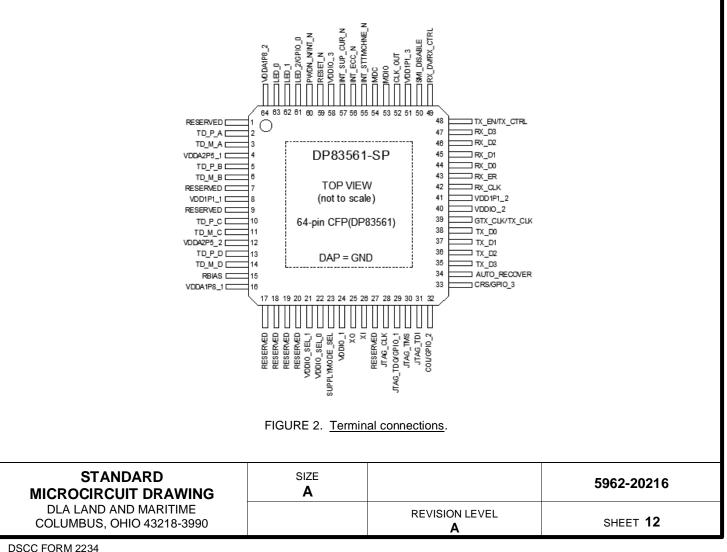

3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 2.

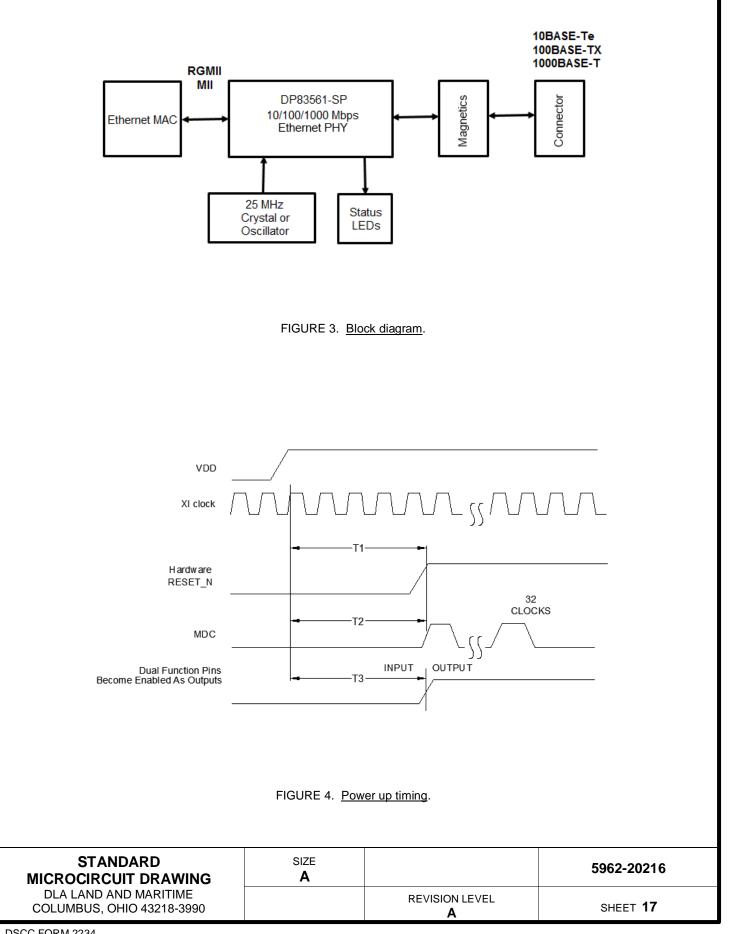

3.2.3 <u>Block diagram</u>. The block diagram shall be as specified on figure 3.

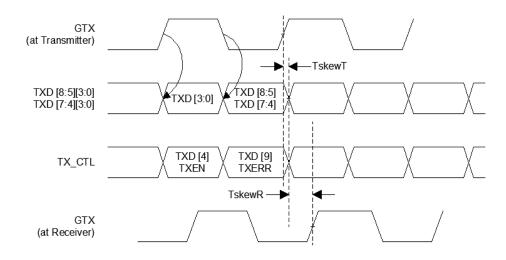

3.2.4 <u>Power up timing</u>. The power up timing shall be as specified on figure 4.

3.2.5 <u>Reset timing</u>. The reset timing shall be as specified on figure 5.

3.2.6 100-Mbps MII transmit timing. The 100-Mbps MII transmit timing shall be as specified on figure 6.

3.2.7 100-Mbps MII receive timing. The 100-Mbps MII receive timing shall be as specified on figure 7.

3.2.8 <u>RGMII transmit multiplexing and timing diagram.</u> The RGMII transmit multiplexing and timing diagram shall be as specified on figure 8.

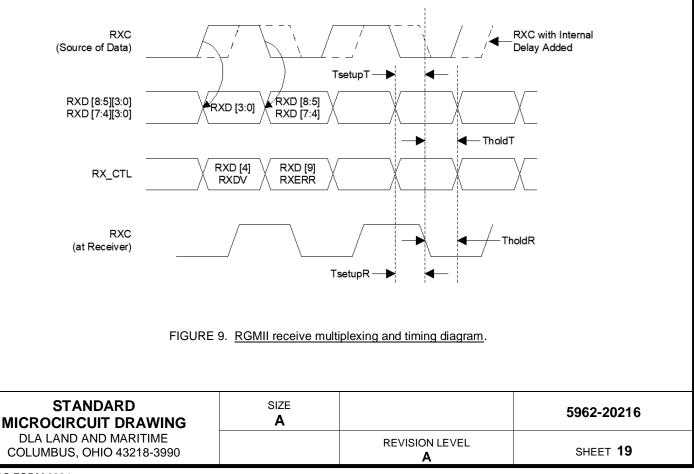

3.2.9 <u>RGMII receive multiplexing and timing diagram.</u> The RGMII receive multiplexing and timing diagram shall be as specified on figure 9.

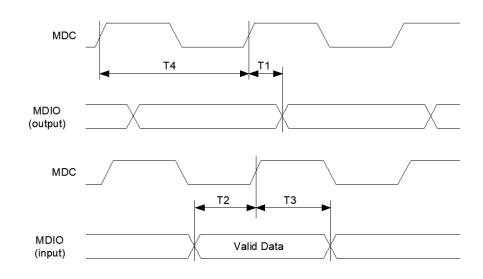

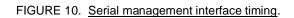

3.2.10 Serial management interface timing. The serial management interface timing shall be as specified on figure 10.

3.2.11 <u>Radiation exposure circuit</u>. The radiation exposure circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing and acquiring activity upon request.

3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table IA and shall apply over the full a mbient operating temperature range.

3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table IIA. The electrical tests for each subgroup are defined in table IA.

3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked. For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device. For RHA product using this option, the RHA designator shall still be marked. Marking for device classes Q and V shall be in accordance with MIL-PRF-38535.

3.5.1 <u>Certification/compliance mark</u>. The certification mark for device classes Q and V shall be a "QML" or "Q" as required in MIL-PRF-38535.

3.6 <u>Certificate of compliance</u>. For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.6.1 herein). The certificate of compliance submitted to DLA Land and Maritime-VA prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device classes Q and V, the requirements of MIL-PRF-38535 and herein.

3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device classes Q and V in MIL-PRF-38535 shall be provided with each lot of microcircuits delivered to this drawing.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br>A |                     | 5962-20216 |

|----------------------------------------------------|-----------|---------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL<br>A | SHEET 6    |

| Test                                                         | Symbol | $\begin{array}{l} Conditions \ \underline{1}/ \ \underline{3}/ \\ -55^{\circ}C \leq T_A \leq +125^{\circ}C \end{array}$ | Group A<br>subgroups | Limits          | 1               | Test |

|--------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------|-----------------|------|

|                                                              |        | $1.1V \le AVDD \le +2.5V$ unless otherwise specified                                                                    |                      | Min             | Max             |      |

| IEEE Tx conformance<br>(1000BaseT)                           |        |                                                                                                                         |                      |                 |                 |      |

| Output differential voltage                                  |        | Normal mode, all channels                                                                                               | 1,2,3                | 0.67            | 0.82            | V    |

| IEEE Tx conformance<br>(100BaseTx)                           |        |                                                                                                                         |                      |                 |                 |      |

| Output differential voltage <u>2</u> /                       |        | Normal mode, channels A and B                                                                                           | 1,2,3                | 0.95            | 1.05            | V    |

| Bootstrap DC characteristics<br>(4 level) (PHY address pins) |        |                                                                                                                         |                      |                 | 1               |      |

| Mode 0 strap voltage range                                   | VMODE0 |                                                                                                                         | 1,2,3                | 0               | 0.093xV<br>DDIO | V    |

| Mode 1 strap voltage range                                   | VMODE1 |                                                                                                                         | 1,2,3                | 0.136x<br>VDDIO | 0.184x<br>VDDIO | V    |

| Mode 2 strap voltage range                                   | VMODE2 |                                                                                                                         | 1,2,3                | 0.219x<br>VDDIO | 0.280x<br>VDDIO | V    |

| Mode 3 strap voltage range                                   | VMODE3 |                                                                                                                         | 1,2,3                | 0.600x<br>VDDIO | 0.888x<br>VDDIO | V    |

| Bootstrap DC characteristics<br>(2 level)                    |        |                                                                                                                         |                      |                 |                 |      |

| Mode 0 strap voltage range                                   | VMODE0 |                                                                                                                         | 1,2,3                | 0               | 0.18x<br>VDDIO  | V    |

| Mode 1 strap voltage range                                   | VMODE1 |                                                                                                                         | 1,2,3                | 0.50x<br>VDDIO  | 0.88x<br>VDDIO  | V    |

| IO characteristics                                           |        |                                                                                                                         |                      |                 |                 |      |

| High level input voltage                                     | Vih    | VDDIO = 3.3V ±5%                                                                                                        | 1,2,3                | 2               |                 | V    |

| Low level input voltage                                      | VIL    | VDDIO = 3.3V ±5%                                                                                                        | 1,2,3                |                 | 0.8             | V    |

| high level output voltage                                    | Vон    | I <sub>OH</sub> = -2mA, VDDIO = 3.3V ±5%                                                                                | 1,2,3                | 2.4             |                 | V    |

| Low level output voltage                                     | Vol    | I <sub>OL</sub> = 2mA, VDDIO = 3.3V ±5%                                                                                 | 1,2,3                |                 | 0.4             | V    |

| High level input voltage                                     | Vін    | VDDIO = 2.5V ±5%                                                                                                        | 1,2,3                | 1.7             |                 | V    |

| Low level input voltage                                      | VIL    | VDDIO = 2.5V ±5%                                                                                                        | 1,2,3                |                 | 0.7             | V    |

| high level output voltage                                    | Vон    | I <sub>OH</sub> = -2mA, VDDIO = 2.5V ±5%                                                                                | 1,2,3                | 2               |                 | V    |

| Low level output voltage                                     | Vol    | $I_{OL} = 2mA$ , VDDIO = 2.5V ±5%                                                                                       | 1,2,3                |                 | 0.4             | V    |

| High level input voltage                                     | Vін    | VDDIO = 1.8V ±5%                                                                                                        | 1,2,3                | 0.65*<br>VDDIO  |                 | V    |

| Low level input voltage                                      | VIL    | VDDIO = 1.8V ±5%                                                                                                        | 1,2,3                |                 | 0.35*<br>VDDIO  | V    |

| high level output voltage                                    | Vон    | I <sub>OH</sub> = -2mA, VDDIO = 1.8V ±5%                                                                                | 1,2,3                | VDDIO-<br>0.45  |                 | V    |

| Low level output voltage                                     | Vol    | I₀∟ = 2mA, VDDIO = 1.8V ±5%                                                                                             | 1,2,3                |                 | 0.45            | V    |

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                            | 5962-20216 |

|----------------------------------------------------|------------------|----------------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br><b>A</b> | SHEET 7    |

| TAE                                                                                               | BLE IA. <u>EI</u> | ectrical performance characteristics                                          | <u>s</u> – Continued |        |       |      |

|---------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------|----------------------|--------|-------|------|

| Test                                                                                              | Symbol            | Conditions $\underline{1}/ \underline{3}/$<br>-55°C ≤ T <sub>A</sub> ≤ +125°C | Group A<br>subgroups | Limits |       | Unit |

|                                                                                                   |                   | $1.1V \le AVDD \le +2.5V$ unless otherwise specified                          |                      | Min    | Max   |      |

| IO characteristics – Continued                                                                    | -                 | -                                                                             |                      |        | -     | -    |

| Input high current                                                                                | Іін               | Input high current                                                            | 1,2,3                | -55    | 55    | μA   |

| Input low current                                                                                 | lı∟               | $T_A = -55^{\circ}C$ to $125^{\circ}C$ , $V_{IN} = GND$                       | 1,2,3                | -35    | 35    | μA   |

| Tri-state output high current                                                                     | Іогн              | T <sub>A</sub> = -55°C to 125°C, V <sub>OUT</sub> =GND                        | 1,2,3                | -55    | 55    | μA   |

| Tri-state output low current                                                                      | Iozl              | T <sub>A</sub> = -55°C to 125°C, V <sub>OUT</sub> =GND                        | 1,2,3                | -35    | 35    | μA   |

| Internal pull down resistor                                                                       | Rpulldn           |                                                                               | 1,2,3                | 6.75   | 11.25 | kΩ   |

| High level input voltage                                                                          | XI Vih            |                                                                               | 1,2,3                | 1.2    | VDDIO | V    |

| Low level input voltage                                                                           | XI VIL            |                                                                               | 1,2,3                |        | 0.6   | V    |

| Power-up timing<br>(2, 3 supply mode)                                                             |                   |                                                                               |                      |        |       |      |

| Supply ramp rate: For all supplies                                                                |                   |                                                                               | 9,10,11              | 0.5    | 100   | ms   |

| Supply ramp delay offset: For all supplies                                                        |                   |                                                                               | 9,10,11              | 0      | 50    | ms   |

| Last supply power rail ramp to<br>RESET_N                                                         | T1                |                                                                               | 9,10,11              | 200    |       | ms   |

| Reset timing                                                                                      |                   |                                                                               |                      |        |       |      |

| Reset to SMI ready: Post reset<br>stabilization time prior to MDC<br>preamble for register access | T1                |                                                                               | 9,10,11              | 30     |       | μs   |

| RESET PULSE width: minimum<br>reset pulse width to be able to<br>reset                            | ТЗ                |                                                                               | 9,10,11              | 720    |       | ns   |

| MII 100M timing                                                                                   |                   |                                                                               |                      |        |       |      |

| TX_CLK high/low time                                                                              | T1                |                                                                               | 9,10,11              | 16     | 24    | ns   |

| TX_D[3:0], TX_ER, TX_EN<br>setup to TX_CLK                                                        | T2                |                                                                               | 9,10,11              | 10     |       | ns   |

| TX_D[3:0], TX_ER, TX_EN hold from TX_CLK                                                          | Т3                |                                                                               | 9,10,11              | 0      |       | ns   |

| RX_CLK high/low time                                                                              | T1                |                                                                               | 9,10,11              | 16     | 24    | ns   |

| RX_D[3:0], RX_DV delay from<br>RX_CLK rising                                                      | T2                |                                                                               | 9,10,11              | 10     | 30    | ns   |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br>A |                | 5962-20216 |

|----------------------------------------------------|-----------|----------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL | SHEET 8    |

| Test                                                  | Symbol                        | Conditions <u>1</u> / <u>3</u> /<br>-55°C ≤ TA ≤ +125°C |         |      | Limits |     | Limits | Unit |

|-------------------------------------------------------|-------------------------------|---------------------------------------------------------|---------|------|--------|-----|--------|------|

|                                                       |                               | $1.1V \leq AVDD \leq +2.5V$ unless otherwise specified  |         | Min  | Max    |     |        |      |

| RGMII output timing (1G)                              |                               |                                                         |         |      |        |     |        |      |

| Data to clock output skew<br>(non-delay mode)         | T <sub>skewT</sub>            |                                                         | 9,10,11 | -600 | 625    | ps  |        |      |

| Data to clock output setup (delay mode: 2 ns default) | T <sub>skewT</sub><br>(delay) |                                                         | 9,10,11 | 1.5  | 2.5    | ns  |        |      |

| Data to clock output setup<br>(delay mode)            | TsetupT                       |                                                         | 9,10,11 | 1.2  |        | ns  |        |      |

| Data to clock output hold<br>(delay mode)             | $T_{holdT}$                   |                                                         | 9,10,11 | 1.2  |        | ns  |        |      |

| Clock cycle duration                                  | T <sub>cyc</sub>              |                                                         | 9,10,11 | 7.2  | 8.8    | ns  |        |      |

| Duty cycle                                            |                               |                                                         | 9,10,11 | 45   | 58     | %   |        |      |

| Rise / Fall time (20% to 80%)                         |                               |                                                         | 9,10,11 |      | 0.85   | ns  |        |      |

| RGMII input timing (1G)                               |                               |                                                         |         |      |        |     |        |      |

| TX data to clock input setup                          | T <sub>setupR</sub>           |                                                         | 9,10,11 | 1    |        | ns  |        |      |

| TX clock to data input hold                           | T <sub>holdR</sub>            |                                                         | 9,10,11 | 1    |        | ns  |        |      |

| SMI timing                                            |                               |                                                         |         |      |        |     |        |      |

| MDC to MDIO (Output) delay time<br>(25 pF load)       | T1                            |                                                         | 9,10,11 | 0    | 20     | ns  |        |      |

| MDIO (Input) to MDC setup time                        | T2                            |                                                         | 9,10,11 | 10   |        | ns  |        |      |

| MDIO (Input) to MDC hold time                         | Т3                            |                                                         | 9,10,11 | 10   |        | ns  |        |      |

| MDC frequency (25 pF load)                            | T4                            |                                                         | 9,10,11 |      | 24     | MHz |        |      |

| Output clock timing<br>(25 MHz clkout)                |                               |                                                         |         |      |        |     |        |      |

| Frequency (PPM)                                       |                               |                                                         | 9,10,11 | -100 | 100    | -   |        |      |

| Duty cycle                                            |                               |                                                         | 9,10,11 | 40   | 60     | %   |        |      |

| 25 MHz input clock tolerance                          |                               |                                                         |         |      |        |     |        |      |

| Frequency tolerance                                   |                               |                                                         | 9,10,11 | -100 | +100   | ppm |        |      |

| Rise / fall time (10% - 90%)                          |                               |                                                         | 9,10,11 |      | 8      | ns  |        |      |

| Duty cycle                                            |                               |                                                         | 9,10,11 | 40   | 60     | %   |        |      |

<u>1</u>/ Power dissipation measurements: Traffic: 100%, packet size: 1512, random content, temperature: -55 to 125°C, voltage range: ±5%.

2/ In mirror mode, channel D & C are used for Tx and Rx. Please refer to mirror mode selection for additional configuration, for output differential voltage.

3/ For RGMII interface, please refer to RGMII timing and IBIS mode based signal integrity simulation (add reference to section).

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br><b>A</b> |                     | 5962-20216 |

|----------------------------------------------------|------------------|---------------------|------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |                  | REVISION LEVEL<br>A | SHEET 9    |

## TABLE IB. SEP test limits. 1/2/3/

| Device type | Bias VDDIO = 3.465 V for SEL test $\frac{4}{}$<br>No SEL occurs at effective LET |

|-------------|----------------------------------------------------------------------------------|

| All         | LET ≤ 121 MeV⋅cm²/mg                                                             |

1/ For single event phenomena (SEP) test conditions, see 4.4.5.3 herein.

2/ Technology characterization and model verification supplemented by in-line data may be used in lieu of end of line testing. Test plan must be approved by TRB and qualifying activity.

3/ Heavy ion single event effects (SEE) test was performed at the TAMU Cyclotron Radiation Effects facility using a superconducting cyclotron and an advanced electron cyclotron resonance (ECR) ion source. No single event latch-up (SEL) was observed under <sup>197</sup>Au ions at angle 43° at Vmax supply voltages and operating temperature 125°C corresponding to an effective LET of 121 MeV·cm<sup>2</sup>/mg. For more information on SEP test results, customers are requested to contact the manufacturer.

<u>4</u>/ Tested for latch-up at worst case temperature,  $TA = +125^{\circ}C \pm 10^{\circ}C$ .

| STANDARD<br>MICROCIRCUIT DRAWING                   | SIZE<br>A |                     | 5962-20216      |

|----------------------------------------------------|-----------|---------------------|-----------------|

| DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL<br>A | SHEET <b>10</b> |

## NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This package is hermetically sealed with a metal lid.

- 3. Ground pad to be electronic connected to heat sink and seal ring.

- 4. The leads are gold plated and can be solder dipped.

|     | PIN            | I/O | TYPE | DESCRIPTION                                                                                                                                                                                                                                         |  |

|-----|----------------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO. | NAME           |     |      |                                                                                                                                                                                                                                                     |  |

| 1   | Reserved       | I/O |      | Reserved. Keep it NC.                                                                                                                                                                                                                               |  |

| 2   | TD_P_A         | I/O | А    | Differential transmit and receive signals.                                                                                                                                                                                                          |  |

| 3   | TD_M_A         | I/O | А    | Differential transmit and receive signals.                                                                                                                                                                                                          |  |

| 4   | VDDA2P5_1      | Ι   | А    | 2.5-V analog supply ( $\pm$ 5%). Each pin requires a 1- $\mu$ F and 0.1- $\mu$ F capacitor to GND.                                                                                                                                                  |  |

| 5   | TD_P_B         | I/O | А    | Differential transmit and receive signals.                                                                                                                                                                                                          |  |

| 6   | TD_M_B         | I/O | А    | Differential transmit and receive signals.                                                                                                                                                                                                          |  |

| 7   | Reserved       | Ι   | А    | Reserved. Keep it NC.                                                                                                                                                                                                                               |  |

| 8   | VDD1P1_1       | Ι   | А    | 1.1-V digital supply (±5%). Each pin requires a 1- $\mu$ F and 0.1- $\mu$ F capacitor to GND.                                                                                                                                                       |  |

| 9   | Reserved       | Ι   | А    | Reserved. Keep it NC.                                                                                                                                                                                                                               |  |

| 10  | TD_P_C         | I/O | А    | Differential transmit and receive signals.                                                                                                                                                                                                          |  |

| 11  | TD_M_C         | I/O | А    | Differential transmit and receive signals.                                                                                                                                                                                                          |  |

| 12  | VDDA2P5_2      | I   | А    | 2.5-V analog supply (±5%). Each pin requires a 1- $\mu$ F and 0.1- $\mu$ F capacitor to GND.                                                                                                                                                        |  |

| 13  | TD_P_D         | I/O | А    | Differential transmit and receive signals.                                                                                                                                                                                                          |  |

| 14  | TD M D         | I/O | А    | Differential transmit and receive signals.                                                                                                                                                                                                          |  |

| 15  | RBIAS          | I   | A    | Bias resistor connection. An $10-k\Omega \pm 1\%$ resistor should be connected RBIAS to GND. A 90-pF $\pm 10\%$ capacitor should be connected in para with the bias resistor.                                                                       |  |

| 16  | VDDA1P8_1      | Ι   | A    | In three-supply mode, an external 1.8-V ( $\pm$ 5%) supply can be connected to these pins. When using an external supply, each pin requires a 1-µF and 0.1-µF capacitor to GND.<br>In two supply mode, no external supply is required for this pin. |  |

|     |                |     |      | When unused, no connections should be made to these pins.                                                                                                                                                                                           |  |

| 17  | Reserved       | _   | A    | Reserved. Keep it NC.                                                                                                                                                                                                                               |  |

| 18  | Reserved       |     | A    | Reserved. Keep it NC.                                                                                                                                                                                                                               |  |

| 19  | Reserved       | —   | А    | Reserved. Keep it NC.                                                                                                                                                                                                                               |  |

| 20  | Reserved       | —   | А    | Reserved. Keep it NC.                                                                                                                                                                                                                               |  |

| 21  | VDDIO_SEL_1    | I   | A, S | VDDIO_SEL1/VDDIO_SEL0:<br>00 (default): VDDIO 3V3<br>01: Reserve                                                                                                                                                                                    |  |

| 22  | VDDIO_SEL_0    | I   | A, S | 10: VDDIO 2V5<br>11: VDDIO 1V8                                                                                                                                                                                                                      |  |

| 23  | SUPPLYMODE_SEL |     | S    | 0 = Dual supply mode (VDDA1P8 left floating) (Default)<br>1 = Triple supply mode (VDDA1P8 supplied by system)                                                                                                                                       |  |

| 24  | VDDIO_1        | Ι   | А    | I/O power: 1.8V (±5%), 2.5V (±5%) or 3.3V (±5%). Each pin requires a 1- $\mu$ F and 0.1- $\mu$ F capacitor to GND                                                                                                                                   |  |

| 25  | хо             | 0   | А    | CRYSTAL OSCILLATOR OUTPUT: Second terminal for 25-MHz crystal.<br>Must be left floating if a clock oscillator is used.                                                                                                                              |  |

FIGURE 2. <u>Terminal connections</u> – Continued.

| STANDARD<br>MICROCIRCUIT DRAWING<br>DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 | SIZE<br><b>A</b> |                     | 5962-20216      |

|----------------------------------------------------------------------------------------|------------------|---------------------|-----------------|

|                                                                                        |                  | REVISION LEVEL<br>A | SHEET <b>13</b> |

|     | PIN             | I/O | TYPE  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|-----------------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME            |     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 26  | XI              | Ι   | A     | CRYSTAL OSCILLATOR INPUT: 25-MHz oscillator or crystal input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 27  | Reserved        | _   | А     | Reserved. Keep it NC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 28  | JTAG_CLK        | Ι   | PU    | JTAG TEST CLOCK: IEEE 1149.1 test clock input, primary clock source for all test logic input and output controlled by the testing entity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 29  | JTAG_TDO/GPIO_1 | 0   | PD    | JTAG TEST DATA OUTPUT: IEEE 1149.1 test data output pin, the most recent test results are scanned out of the device via TDO.<br>General Purpose I/O: This signal provides a multi-function configurable I/O Please refer to the GPIO_MUX_CTRL register for details.<br>This pin should be pulled down by a 2.49-kΩ resistor.                                                                                                                                                                                                                                                                                            |

| 30  | JTAG_TMS        | I   | PU    | JTAG TEST MODE SELECT: IEEE 1149.1 test mode select pin, the TMS pin sequences the tap controller (16-state FSM) to select the desired test instruction. Recommend the user apply 3 clock cycles with JTAG_TMS high to reset the JTAG.                                                                                                                                                                                                                                                                                                                                                                                  |

| 31  | JTAG_TDI        | Ι   | PU    | JTAG TEST DATA INPUT: IEEE 1149.1 Test Data Input pin, test data is scanned into the device through the TDI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 32  | COL/GPIO_2      | I/O | PD    | COLLISION DETECT: Asserted high to indicate detection of a collision<br>condition (assertion of CRS due to simultaneous transmit and receive<br>activity) in half-duplex modes. This signal is not synchronous to either MII<br>clock (GTX_CLK, TX_CLK or RX_CLK).<br>(Default) general purpose I/O: This signal provides a multi-function<br>configurable I/O.<br>Refer to the GPIO_MUX_CTRL register for details.                                                                                                                                                                                                     |

| 33  | COL/GPIO_3      | I/O | PD, S | CARRIER SENSE: CRS is asserted high to indicate the presence of a carrier due to receive or transmit activity in Half-Duplex mode.<br>(Default) General Purpose I/O: This signal provides a multi-function configurable I/O.<br>Please refer to the GPIO_MUX_CTRL register for details.                                                                                                                                                                                                                                                                                                                                 |

| 34  | AUTO_RECOVER    | I   | PD, S | <ul> <li>0 = DP8356-SP will take no automatic action based on SEFI. SEFI event interrupts will be generated normally. (Default)</li> <li>1 = Configures the DP8356-SP to automatically apply RESET signal to PHY logic when a SEFI is detected by one of the monitors configured (STATE_MACHINE, temperature monitor, PLL lock, ECC registers). Default register values will be reloaded and pin options. SEFI event interrupts will be generated normally.</li> </ul>                                                                                                                                                  |

| 35  | TX_D3           | Ι   | PD    | TRANSMIT DATA: Signal TX_D [3:0] carries data from the MAC to the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 36  | TX_D2           | I   | PD    | PHY in RGMII mode and MII mode. Data is synchronous to the transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 37  | TX_D1           | I   | PD    | clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 38  | TX_D0           | Ι   | PD    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 39  | GTX_CLK/TX_CLK  | I/O | PD/O  | RGMII TRANSMIT CLOCK: This continuous clock signal is sourced from<br>the MAC layer to the PHY. Nominal frequency is 125 MHz in 1000-Mbps<br>mode. This pin will be input in RGMII mode.<br>MII TRANSMIT CLOCK: In MII mode, this pin provides a 25-MHz reference<br>clock for 100-Mbps speed and a 2.5-MHz reference clock for 10-Mbps<br>speed. This pin will be output in MII mode.<br>This pin will be GTX_CLK by default and can be changed to TX_CLK by<br>register configurations. Selection of the MII MAC interface also changes th<br>GTX_CLK/TX_CLK selection without any additional register writes needed. |

| STANDARD<br>MICROCIRCUIT DRAWING<br>DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 | SIZE<br><b>A</b> |                     | 5962-20216      |

|----------------------------------------------------------------------------------------|------------------|---------------------|-----------------|

|                                                                                        |                  | REVISION LEVEL<br>A | SHEET <b>14</b> |

| PIN |                | PIN I/O TYPE |       | DESCRIPTION                                                                                                                                                                                                                                                                                      |  |  |

|-----|----------------|--------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. | NAME           |              |       |                                                                                                                                                                                                                                                                                                  |  |  |

| 40  | VDDIO_2        | Ι            | А     | I/O power: 1.8V (±5%), 2.5V (±5%) or 3.3V (±5%). Each pin requires a 1- $\mu$ F and 0.1- $\mu$ F capacitor to GND.                                                                                                                                                                               |  |  |

| 41  | VDD1P1_2       | I            | А     | 1.1-V digital supply (±5%). Each pin requires a 1- $\mu$ F and 0.1- $\mu$ F capacitor to GND.                                                                                                                                                                                                    |  |  |

| 42  | RX_CLK         | 0            | PD    | RECEIVE CLOCK: Provides the recovered receive clocks for different<br>modes of operation:<br>125 MHz in 1000-Mbps RGMII mode.<br>25 MHz in 100-Mbps RGMII/MII mode.<br>2.5 MHz in 10-Mbps RGMII/MII mode.<br>When PHY is not linked, this pin provides 2.5 MHz clock for both<br>RGMII/MII mode. |  |  |

| 43  | RX_ER          | 0            | PD    | MII Mode: In MII mode this pin will be configured as RX_ER. This pin is asserted high synchronously to rising edge of RX_CLK. Use of this pin is optional.                                                                                                                                       |  |  |

| 44  | RX_D0          | 0            | PD, S | RECEIVE DATA: Signal RX_D [3:0] carries data from the PHY to the MAC                                                                                                                                                                                                                             |  |  |

| 45  | RX_D1          | 0            | PD, S | in RGMII mode and in MII mode. Symbols received on the cable are                                                                                                                                                                                                                                 |  |  |

| 46  | RX_D2          | 0            | PD    | decoded and presented on these pins synchronous to RX_CLK.                                                                                                                                                                                                                                       |  |  |

| 47  | RX_D3          | 0            | PD    | RX_D2 and RX_D3 should be pulled down by a 2.49-k $\Omega$ resistor.                                                                                                                                                                                                                             |  |  |

| 48  | TX_EN/TX_CTRL  | Ι            | PD    | TX_EN: In MII mode, this pin will function as TX_EN.<br>TRANSMIT CONTROL: In RGMII mode, TX_CTRL combines the trans<br>enable and the transmit error signal inputs from the MAC using both clo<br>edges.                                                                                         |  |  |

| 49  | RX_DV/RX_CTRL  | 0            | PD, S | RX_DV: In MII mode, this pin will function as RX_DV.<br>RECEIVE CONTROL: In RGMII mode, the receive data available and<br>receive error are combined (RXDV_ER) using both rising and falling edges<br>of the receive clock (RX_CLK).                                                             |  |  |

| 50  | SMI_DISABLE    | Ι            | PD, S | 0 = SMI (MDIO) writes are enabled. (Default)<br>1 = Station Management Interface (MDIO) writes are disabled.                                                                                                                                                                                     |  |  |

| 51  | VDD1P1_3       | I            | A     | 1.1-V digital supply (±5%). Each pin requires a 1- $\mu$ F and 0.1- $\mu$ F capacitor to GND.                                                                                                                                                                                                    |  |  |

| 52  | CLK_OUT        | 0            | 0     | CLOCK OUTPUT: Output clock                                                                                                                                                                                                                                                                       |  |  |

| 53  | MDIO           | I/O          | _     | MANAGEMENT DATA I/O: Bi-directional management instruction/data signal that may be sourced by the management station or the PHY. This open-drain pin requires a 2.2-k $\Omega$ pull-up resistor.                                                                                                 |  |  |

| 54  | MDC            | Ι            | _     | MANAGEMENT DATA CLOCK: Synchronous clock to the MDIO serial management input/output data. This clock may be asynchronous to the MAC transmit and receive clocks. The maximum clock rate is 25-MHz. There is no minimum clock rate.                                                               |  |  |

| 55  | INT_STTMCHNE_N | 0            | OD    | STATE MACHINE INTERRUPT: This pin will be asserted low when an invalid state machine transition, condition, or other invalid condition is detected. When operating this pin as an open-drain interrupt, an external 2.2- $k\Omega$ resistor connected to the VDDIO supply is recommended.        |  |  |

FIGURE 2. <u>Terminal connections</u> - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING<br>DLA LAND AND MARITIME<br>COLUMBUS, OHIO 43218-3990 | SIZE<br><b>A</b> |                     | 5962-20216      |

|----------------------------------------------------------------------------------------|------------------|---------------------|-----------------|

|                                                                                        |                  | REVISION LEVEL<br>A | SHEET <b>15</b> |

| PIN |               | PIN I/O TYPE <u>2</u> / |       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-----|---------------|-------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO. | NAME          |                         |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 56  | INT_ECC_N     | 0                       | OD    | ECC INTERRUPT: This pin will be asserted low when a configuration register error is detected or corrected by register ECC. When operating this pin as an open-drain interrupt, an external 2.2-k $\Omega$ connected to the VDDIO supply is recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 57  | INT_SUP_CUR_N | 0                       | OD    | SUPPLY CURRENT INTERRUPT: This pin will be asserted low when an abnormal supply current is detected during normal operation. When operating this pin as an open- drain interrupt, an external $2.2k\Omega$ connected to the VDDIO supply is recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 58  | VDDIO_3       | Ι                       | А     | I/O Power: 1.8V (±5%), 2.5V (±5%) or 3.3V (±5%). Each pin requires a 1- $\mu$ F and 0.1- $\mu$ F capacitor to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 59  | RESET_N       | Ι                       | PU, S | RESET_N: This pin is an active-low reset input that initializes or re-<br>initializes all the internal registers of the DP83561-SP. Asserting this pin<br>low for at least 1µs will force a reset process to occur.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |