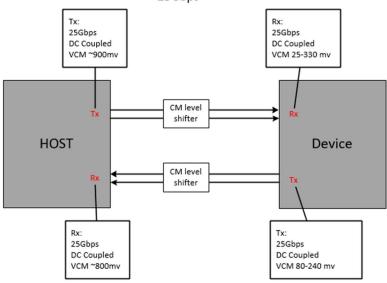

My system is composed with Host and Device.

The host is Xilinx FPGA interfacing its GTY SerDes with UFS device as described below.

## **UFS** lanes

- 100R differential

- DC Coupling

- 25Gbps

UFS Device is DC couple device with next parameters:

- Rx DC common mode allowed: 25-330 mv

- Tx DC common is 80-240 mv.

## FPGA is DC couple host with next parameters:

- Tx DC common mode output: ~900mv

- Rx DC common mode allowed: ~800mv

In order to set desired DC common mode for both FPGA and Device, I need to level shift DC CM in both directions – UFS Tx to FPGA Rx and FPGA Tx to UFS Rx.

I may use an adjustable CM differential Amp / Redriver with CM adjust option or any other IC to overcome the electrical DC CM issue.

Please advise.