# SCANSTA101 STA Master

Design Guide

2010 Revision 1.0

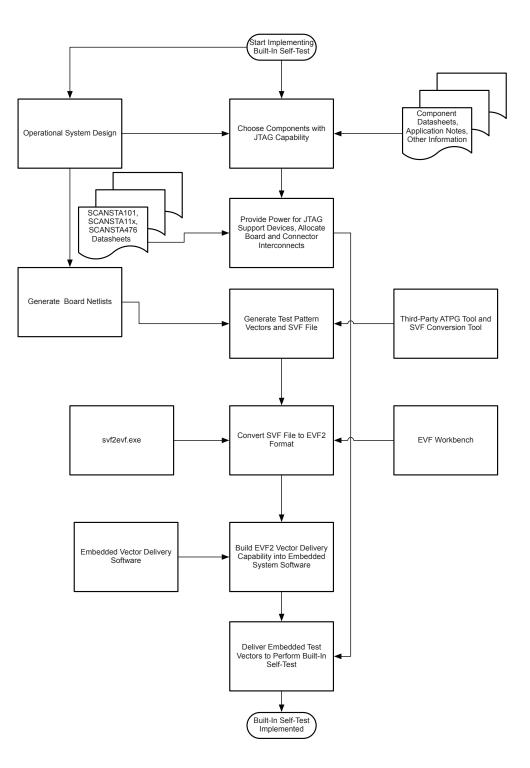

# Developing a System with Embedded IEEE 1149.1 Boundary-Scan Self-Test

national.com/scan

# **Table of Contents**

| A  | cknowledge  | ments                                                                    | 4 |

|----|-------------|--------------------------------------------------------------------------|---|

| A  | Word about  | the Automatic Test Pattern Generator Tools                               | 5 |

| 1. | Introductio | n and Scope                                                              | 6 |

|    | 1.1.        | About this Design Guide                                                  | 6 |

|    | 1.2.        | An Engineer's Historical Perspective                                     | 6 |

|    | 1.3.        | Purpose of this Design Guide                                             | 7 |

| 2. | A Brief Int | oduction to Boundary Scan                                                |   |

|    | 2.1.        | National's Boundary Scan Family                                          |   |

|    | 2.2.        | The IEEE 1149.1 Standard                                                 |   |

|    | 2.3.        | Boundary Scan Basics                                                     |   |

|    | 2.3.1.      | Elements of the IEEE 1149.1 Test Access Port (TAP)                       |   |

|    | 2.3.2.      | Architecture of the IEEE 1149.1 TAP                                      |   |

|    | 2.3.3.      | Use of the IEEE 1149.1 TAP                                               |   |

|    | 2.4.        | Summary and Conclusions                                                  |   |

| 3. | Test Syster | n Description                                                            |   |

|    | 3.1.        | The SCANSTAEVK Demonstration Kit                                         |   |

|    | 3.1.1.      | PCI-1149.1/101 SCANSTA101 PC Card                                        |   |

|    | 3.1.2.      | SCANSTAEVK Demonstration Kit Backplane                                   |   |

|    | 3.1.3.      | SCANSTA111 Intermediate Board                                            |   |

|    | 3.1.4.      | Target SerDes Board                                                      |   |

|    | 3.1.5.      | Demonstration Kit Summary                                                |   |

|    | 3.2.        | Test Development and Deployment Software                                 |   |

|    | 3.2.1.      | Automatic Test Pattern Generation                                        |   |

|    | 3.2.2.      | Conversion to EVF2 Format                                                |   |

|    | 3.2.3.      | Embedded Platform Software                                               |   |

|    | 3.2.4.      | ScanVec                                                                  |   |

|    | 3.3.        | Summary                                                                  |   |

| 4. |             | Design Considerations for Built-In Self-Test                             |   |

|    | 4.1.        | System Function and Built-In Self-Test                                   |   |

|    | 4.1.1.      |                                                                          |   |

|    | 4.1.2.      |                                                                          |   |

|    | 4.1.3.      | Delivery of the Test Vectors                                             |   |

|    | 4.1.4.      | TAP Connections                                                          |   |

|    |             | . Single JTAG TAP over the Backplane                                     |   |

|    |             | . Multiple JTAG TAPs over the Backplane                                  |   |

|    |             | . Parallel-Port Communication over the Backplane                         |   |

|    | 4.2.        | Test Implementation                                                      |   |

|    | 4.2.1.      | Place and Route the JTAG Support Devices                                 |   |

|    | 4.2.2.      | Connect the Parallel Processor Interface of the SCANSTA101 STA Master(s) |   |

|    | 4.2.3.      | Connect the TAP                                                          |   |

|    | 4.2.4.      | Asynchronous Reset TRST*                                                 |   |

|    | 4.2.5.      | Test Clock (TCK)                                                         |   |

# **Table of Contents**

|    | 4.2.6.                            | Test Mode Select (TMS)                            | 28 |

|----|-----------------------------------|---------------------------------------------------|----|

|    | 4.2.7.                            | Test Data In (TDI) and Test Data Out (TDO)        | 29 |

|    | 4.3.                              | Summary                                           | 30 |

| 5. | Developme                         | ent of a Boundary Scan Test Pattern               | 31 |

|    | 5.1.                              | ATPG Tool Selection                               | 31 |

|    | 5.2.                              | Producing the Netlist                             | 31 |

|    | 5.3.                              | Entering the Netlist into the ATPG Tool           | 32 |

|    | 5.4.                              | Adding Information to the Netlist                 | 33 |

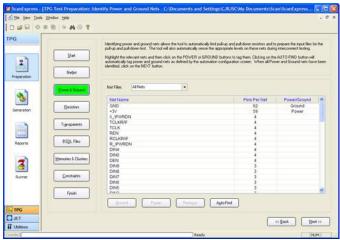

|    | 5.4.1.                            | Power and Ground Nets                             | 33 |

|    | 5.4.2.                            | Resistors                                         | 33 |

|    | 5.4.3.                            | Transparent Devices                               | 34 |

|    | 5.4.4.                            | Adding BSDL Models                                | 34 |

|    | 5.4.5.                            | Modifying the Connections in the Netlist          | 36 |

|    | 5.5.                              | Generation of the Boundary Scan Test and SVF File | 37 |

|    | 5.5.1.                            |                                                   |    |

|    | 5.5.2.                            | Serial Vector Format                              |    |

|    | 5.6.                              | Generation of an EVF2 File using EVF Workbench    |    |

| 6. | Embedded                          | Vector Delivery Software                          |    |

|    | 6.1.                              | Development of the System Controller Software     |    |

|    |                                   | National Semiconductor Code                       |    |

|    |                                   | Interface to the EVF2 File and Error Handling     |    |

|    |                                   | . EVF2 File Read Function                         |    |

|    |                                   | . Error Handler                                   |    |

|    |                                   | . Fail Handler                                    |    |

|    |                                   | . Register Trace Handler                          |    |

|    |                                   | . Debug Handler                                   |    |

|    |                                   | . Polling Handler                                 |    |

|    |                                   | . Timeout Value                                   |    |

|    |                                   | . User Pointer Arguments                          |    |

|    | 6.2.                              | 5                                                 |    |

| 7. | Dissecting the Built-In Self-Test |                                                   |    |

|    |                                   | The SVF File                                      |    |

|    | 7.2.                              | The EVF2 File                                     |    |

| 8. | •                                 | ll Together                                       |    |

|    | 8.1.                              | Demonstration of the Built-In Self-Test           |    |

|    | 8.2.                              | Summary and Conclusions                           |    |

| 9. | •                                 | es                                                |    |

|    | 9.1.                              | BSDL Files                                        |    |

|    | 9.2.                              | SVF File                                          |    |

|    | 9.3.                              | EVF2 File                                         |    |

| 10 | ). References                     | 3                                                 | 75 |

Permission to use screen capture images and listings was provided by Corelis, JTAG Technologies, and Flynn Systems Corporation. Engineers from these companies also provided valuable assistance and consulting in the development of the material presented in this design guide. Their help is gratefully acknowledged. This design guide focuses on built-in self-test. The Joint Test Action Group (JTAG) Test Access Port (TAP) can be used for much more than built-in self-test, but this is beyond the scope of this design guide. For the built-in self-test example in this design guide, Automatic Test Pattern Generator (ATPG) tools from three vendors were used. The three tools were JTAG Technologies ProVision, Flynn Systems onTAP, and Corelis ScanExpress TPG.

Each ATPG tool vendor supplies test hardware designed to work with that vendor's ATPG tool. All three vendors provide their ATPG tools as part of a complete test system. These test systems are useful for manufacturing test, engineering debug, and any other areas where the JTAG TAP finds application beyond built-in self-test.

The procedures for using these tools described in this design guide focus on the use of the tools to produce 'static' Serial Vector Format (SVF) files. These files are generated prior to system deployment using an ATPG tool, which is external to the system to be tested. The files are then used for built-in self-test on multiple units of the system to be tested. This procedure generally produces limited diagnostic information. Extensive diagnostic information requires a more dynamic approach. All of the ATPG tool/test hardware systems are designed to enable extensive diagnostics by performing dynamic, flexible, and powerful board tests using the JTAG TAP. These diagnostic tests can be tailored by the ATPG systems "on the fly" to zero in on a detected fault and diagnose it. For most applications, the use of these tools for manufacturing test provides capabilities beyond those that can be reasonably implemented in a built-in self-test.

The design guide focuses on the use of these tools to produce 'static' SVF files for deployment on embedded test hardware for the purposes of built-in self-test. All of these tools can be used for and perform equally well for this purpose. The selection of an ATPG tool is a matter of personal preference and company history. Nothing in this design guide is intended to, or should be interpreted to suggest that one or the other of these tools is preferred for built-in self-test. They can all perform the job described in this design guide, and they can all do much more.

Discussion of the capabilities and merits of the various tools is beyond the scope of this design guide. For further information on the ATPG tools and the associated test systems, it is suggested that the reader contact the various tool vendors.

# 1.1. About this Design Guide

This design guide provides a roadmap for implementing IEEE 1149.1 boundary scan functionality on a printed circuit board. The guide is divided into several major chapters:

- Introduction and Scope This chapter provides a brief historical introduction to boundary scan techniques and describes the purpose and scope of the design guide itself.

- A Brief Introduction to Boundary Scan National's SCANSTA family of boundary scan support devices is introduced in this chapter. This chapter also provides a high-level summary of IEEE 1149.1 operations.

- Test System Description This chapter describes the system used as an example in the guide. The system includes hardware and software. It is meant to model, in a simplified way, an operational system that might include IEEE 1149.1 built-in self-test.

- Hardware Design Considerations for Built-In Self-Test The hardware design considerations involved in implementing built-in self-test using the IEEE 1149.1 TAP are described. The conclusion of this chapter is that IEEE 1149.1 operation is very easy to implement from a hardware standpoint.

- Development of a Boundary Scan Test Pattern This chapter describes the steps involved in using commercially-available Automatic Test Pattern Generator (ATPG) software to generate IEEE 1149.1 boundary scan test patterns for built-in self-test.

- Embedded Vector Delivery Software The embedded vector delivery software to be implemented on the system controller is outlined in this chapter. The software provided by National Semiconductor for embedded vector delivery is straightforward to implement and flexible.

- Dissecting the Built-In Self-Test This chapter takes a closer look at the mechanics of the IEEE 1149.1 operation. The "behind-the-scenes" look at boundary scan included in this chapter is meant to provide deeper insight into how boundary scan works.

- Putting It All Together All of the design considerations presented earlier are summarized. In this chapter, an example of a boundary scan built-in self-test in operation is presented.

- Sample Files The sample file listings provide complete listings of the data files required for the IEEE 1149.1 built-in self-test development and deployment.

- **References** This section provides references used in the text and additional information.

Note: Active low signals are designated in this design guide by a trailing asterisk. For example, the active low asynchronous reset line is designated TRST\*. Other conventions commonly used for this type of signal are an overbar, which is used in some of the figures in this design guide, and a trailing slash.

# 1.2. An Engineer's Historical Perspective

In the early days of printed circuit (PC) board design and development, PC boards were simple enough to be layed out by hand. 1/8 inch tape and pre-cut pad shapes were used to lay out boards with through-hole devices at 2x or 4x scale on sheets of Mylar. By the standards of the time, this process of cutting tape and placing pads with a #11 X-acto knife was state of the art.

Then, over the next twenty years, devices went from throughhole to surface mount, and then to advanced chip-scale packages and ball-grid arrays. PC boards went from one or two layers to fifteen, twenty, or more. Contact pitches got smaller as did the pads on the board. It became difficult even to touch a scope probe to a pad on a device for testing because the pad was smaller than the probe tip – often much smaller. On many traces the pads were underneath the device, or on an interior layer that wasn't accessible.

PC boards became denser and their functions became more sophisticated. Engineers could and did design much more functionality into much less space. Twenty boards with twenty integrated circuits each were replaced by one much smaller board with ten integrated circuits of greater functionality and higher cost. Testing these highly-integrated boards was more critical, because of the relatively higher cost of the sophisticated boards, and more difficult because of their small geometries and buried circuitry. PC board testing was a problem waiting for a creative solution.

The creative solution came about in the form of the IEEE 1149.1 boundary scan test standard<sup>1</sup>, also known as JTAG (for Joint Test Action Group, the working group that originally formulated it). The standard is a set of design rules for integrated circuits (principally digital integrated circuits at first but now, increasingly, other integrated circuits as well) which is designed to facilitate board-level testing. The standard does this by specifying an auxiliary test port on each integrated circuit called the Test Access Port or TAP and protocols to address and use it. Through the TAP, many, most, or even all of the pins of an integrated circuit are accessible for testing. If a pin on a device is supposed to be connected by a board trace to a pin on another device, and if both pins are accessible for testing through the TAP, then the connection between them can be tested. And if many, or most, or all of the connections on the board can be tested then many board failures can be detected, diagnosed, and perhaps even repaired early in the manufacturing process where test and debug are less expensive.

Since the JTAG standard was first formulated, new applications for it have proliferated. For example, JTAG is now widely used for in-system programming of programmable devices as described by IEEE Standard 1532<sup>2</sup>. JTAG is also used to provide built-in self-test capability for modern high-density PC boards. To assist in the deployment of these systems, National Semiconductor has developed a family of JTAG support devices. These include the SCANSTA101 JTAG System Test Access (STA) master<sup>3</sup>, the SCANSTA111<sup>4</sup> and SCANSTA112<sup>5</sup> JTAG Scan Bridge multiplexers, and the SCANSTA476 analog voltage monitor<sup>6</sup>. These devices solve system problems that are difficult to attack by any other means.

# 1.3. Purpose of this Design Guide

Development of a useful boundary scan test is the classic journey of 1000 miles that begins with a single step. This design guide describes how to take that first step - and how to take the next several steps as well.

This design guide describes a case study: a simple board designed specifically to demonstrate boundary scan test. The design guide describes the board features enabling boundary scan test. As the board is described it will become apparent that, from a hardware perspective, the addition of boundary scan test to the board requires very little additional engineering beyond that required for the board's base functionality.

The design guide also describes the use of commerciallyavailable Automatic Test Pattern Generator (ATPG) tools to develop test patterns for the demonstration board. The look and feel of each tool is unique, but the use models for all of them are very similar – similar enough so that a detailed demonstration with one tool will also be instructive to users of other tools.

Once the test patterns have been generated, the design guide will take the reader behind the scenes to describe what the test patterns are really meant to accomplish. The design guide will also take the reader through the process of converting the test pattern output to a form useful for deployment in an on-board test application, and will show how to convert it back into a human-readable form to gain further insight into what the builtin test will really do when it is deployed. Finally, the design guide will describe one method of deploying the test pattern to the board, with the aim of providing a useful guide to the system engineer developing a similar built-in test for an operational board or system. It will describe how the test is conducted and what both success and (artificially-induced) failure look like. The design guide will conclude with some useful general conclusions and some suggestions on how to follow the example described here.

This design guide was written from the perspective of what a system designer would do in developing a boundary scan self-test. The objective was to show the reader what steps are required and where the pitfalls are so that the reader can avoid these when he/ she develops a boundary scan-based board self-test.

# 2.1. National's Boundary Scan Family

National manufactures a family of digital integrated circuits targeted at board- and system-level applications using the IEEE 1149.1 system test access port, also known as boundary scan. These devices include:

- SCANSTA101 Low-Voltage IEEE 1149.1 System Test Access (STA) Master

- SCANSTA111 Three-Port Addressable Multidrop IEEE 1149.1 JTAG Multiplexer

- SCANSTA112 Seven-Port Addressable Multidrop IEEE 1149.1 JTAG Multiplexer

- SCANSTA476 Eight-Input IEEE 1149.1 Analog Voltage Monitor

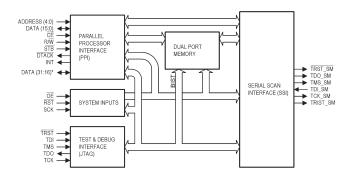

These devices enhance the functionality and ease-ofuse of the IEEE 1149.1 system test access port. National's SCANSTA101 low-voltage IEEE 1149.1 STA master, for example, enables in-system IEEE 1149.1 boundary scan and in-system programming for programmable devices. Its primary function is to present to an on-board or external controller a simplified parallel interface to the serial IEEE 1149.1 boundary scan chain. The SCANSTA101 STA master is supported by National software that simplifies the interface to the on-board microcontroller and to the design tools that generate the boundary scan test vectors.

National's boundary scan support software includes:

- EVF Workbench which provides a graphical user interface for converting Serial Vector Format (SVF) files to Embedded Vector Format 2 (EVF2) files

- SVF2EVF which is the SVF to EVF2 compiler

- EVF2 vector delivery -- the suite of embedded functions that drive the SCANSTA101 STA master from the EVF2 file

National's SCANSTA111 and SCANSTA112 addressable multidrop IEEE 1149.1 STA multiplexers enable simplification of system designs by breaking long boundary scan chains into multiple, shorter chains. This capability is supported in Automatic Test Pattern Generator (ATPG) software from several major software vendors. These devices enable faster, easier-toimplement, and more robust in-system test access.

National's SCANSTA476 eight-input IEEE 1149.1 analog voltage monitor extends the digital IEEE 1149.1 into the analog domain. The SCANSTA476 monitor enables the monitoring of analog voltages for in-system test using protocols similar to those of the standard IEEE 1149.1 system test access port.

# 2.2. The IEEE 1149.1 Standard

The system Test Access Port (TAP) was defined in IEEE Standard 1149.1-1990<sup>17</sup>. As the name indicates, this standard was ratified in 1990, nearly two decades ago as of this writing. This standard and its subsequent updates defined a set of design rules, mostly meant to apply to integrated circuits, which were intended to facilitate board-level tests. Dense, multi-layer printed circuit boards with surface-mounted components, often on both sides, were becoming increasingly common. This made it difficult to ensure that a conventional board tester would be able to access all the required test points. The standard provides a remarkably ingenious solution to this problem. The cost of the ingenuity of the solution is that its implementation may be complex. This design guide describes how National's devices can be used to implement a boundary scan-based builtin self-test quickly and easily. These devices, and the software that supports them, are designed to reduce the complexity of the IEEE 1149.1 interface.

This design guide focuses on the IEEE 1149.1 system test access port and National's family of devices that support it. The design guide provides a roadmap for system designers implementing in-system boundary scan with National's IEEE 1149.1 support (SCAN) devices. It answers basic questions including:

- "What can National's SCAN devices do for me?"

- Section 2.3.3. Use of the IEEE 1149.1 TAP

"How do National's SCAN devices work?"

- Section 3.1.1. PCI-1149.1/101 SCANSTA101 PC Card

- Section 3.1.3. SCANSTA111 Intermediate Board

- "How do I implement National's SCAN devices in my board design?"

- -Chapter 4. Hardware Design Considerations for Built-In Self-Test

"How do I generate the test vectors National's SCAN devices will use?"

- -Chapter 5. Development of a Boundary Scan Test Pattern

- "How do I convert the output of my Automatic Test Pattern Generator program to a format the National SCAN devices understand?"

- Section 5.6. Generation of an EVF2 File Using EVF Workbench

- "How can I deliver the test vectors to the SCANSTA101 master in my system?"

- Chapter 6. Embedded Vector Delivery Software

- "What is really going on 'under the hood' in the boundary scan process?"

- Chapter 7. Dissecting the Built-In Self-Test

- "What should I expect if my board is working correctly? What if it has a manufacturing defect?"

- Section 8.1. Demonstration of the Built-In Self-Test

This design guide is intended for engineers designing new systems with National's SCAN devices and for engineers supporting systems that already include National's SCAN devices. The information contained herein will enable system designers to more easily utilize National's SCAN devices in their designs, leading to improved ease-of-use, acceleration of design cycles, improved manufacturability, and superior system designs.

# 2.3. Boundary Scan Basics

The history of and motivation for boundary scan testing techniques is a fascinating subject, and is well worth an investment of several hours of research. The references in Chapter 10 include excellent treatments of these subjects. They are recommended reading for anyone contemplating the use of JTAG.

This design guide, however, begins with the assumption that the reader has already made the decision to use the IEEE 1149.1 TAP for in-system boundary scan testing or programming of programmable logic devices. In this section a generic example system is described and demonstrated, along with where and how boundary scan can be applied. Following is a brief description of the IEEE 1149.1 TAP and what it can do.

#### 2.3.1. Elements of the IEEE 1149.1 Test Access Port (TAP)

From a conceptual standpoint, the IEEE 1149.1 TAP consists of several functional units:

Four (or five) pins on each digital device in the system implementing the IEEE 1149.1 TAP. These pins form the test access port and they are separate from, and may not be shared with, any other functions of the device. The four required pins are Test Clock (TCK), Test Mode Select (TMS), Test Data In (TDI) and Test Data Out (TDO). The optional pin is an asynchronous, active low Test Reset (TRST\*).

- Digital circuitry which forms the TAP controller on each device implementing the IEEE 1149.1 TAP. The TAP controller is a finite state machine with functionality fully described in the standard.

- 3. An instruction register for the TAP on each device implementing the IEEE 1149.1 TAP. Conceptually, this register controls the behavior of the other registers in the device which are associated with the IEEE 1149.1 TAP.

- A one-bit bypass shift register which can be inserted (by using the instruction register) between the TDI and TDO pins.

- 5. Boundary register cells between each pin of the device and the internal logic connected to the pin. These devices form a boundary register which can be inserted (by using the instruction register) between the TDI and TDO pins. This is the key element of the IEEE 1149.1 standard.

- 6. Other registers and control logic, some required and some optional.

The boundary register cells provide an alternate way to control all the outputs of the device as seen from the device pins. They also provide a way to monitor all the inputs of the device as seen from the device pins. This is like having the ability to probe every line connected to every device (or at least every device that implements the IEEE 1149.1 TAP) in the system. Clearly this is an extremely powerful test capability.

But this is not all that the TAP provides. The boundary register cells can also control the inputs of the device as seen from its core logic, and they can also monitor the outputs of the device as seen from its core logic. This provides both the ability to test any device implementing the IEEE 1149.1 TAP, and the ability to control the inputs of any device independent of the other circuitry on the board.

Finally, the standard for the TAP provides extensibility. It permits device manufacturers to use the IEEE 1149.1 TAP for other purposes. One common use for the IEEE 1149.1 TAP is in-system programming of programmable devices.

#### 2.3.2 Architecture of the IEEE 1149.1 TAP

Seen from the viewpoint of the TDI and TDO pins, the IEEE 1149.1 TAP is a one-bit serial port. Data is clocked in to the TAP one bit at a time and clocked out one bit at a time. What happens between the TDI and TDO pins is controlled by an additional single control bit, the Test Mode Select (TMS). These three pins, along with the Test Clock (TCK), can be used to provide a remarkable range of behavior. The trick is to determine what sequence of bits on the two input pins will produce the desired behavior in the system and what sequence of bits to look for on the output pin to determine the results of the desired test. Fortunately this problem is amenable to a significant degree of automation.

Most modern digital devices are designed using software tools that provide additional levels of abstraction between the desired behavior (often described using a hardware description language such as VHDL or Verilog) and the digital circuitry required to implement it (gates, flip-flops, latches, multiplexers, etc., usually many of them connected in a complex fashion). Similarly, the IEEE 1149.1 TAP was conceived with the intent to rely on software tools to generate the required digital sequences to produce the desired behavior in the system. This simplifies the job of the system designer since he or she does not need to take the design down to the lowest level of operation (long sequences of bits). Nonetheless, understanding this lowest level of operation will help the system designer use National's SCAN devices effectively.

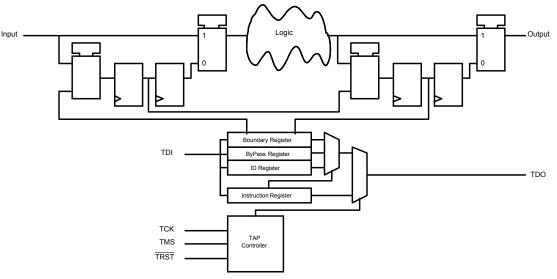

A conceptual design of the IEEE 1149.1 TAP is shown in *Figure* 2-1. The cloud labeled "Logic" represents all the internal logic of the device. The port labeled "Input" represents one of the input pins of the device and the port labeled "Output" represents one of the output pins. The flip-flops and multiplexers between the pins of the device and the internal logic represent a conceptual description of one cell in the boundary register. Each cell in the boundary register holds one bit. The input to each cell can be driven by (1) an output from the previous cell or (2) for an input pin, the input to the device at the pin, or (3) for an output pin, the output from the device's internal logic. When the output of one cell drives the input to the next, the boundary register looks like a shift register. The contents of the boundary register can be unloaded in a parallel operation into the internal logic inputs to the device or into the output pins of the device. This arrangement provides a powerful mechanism for test access.

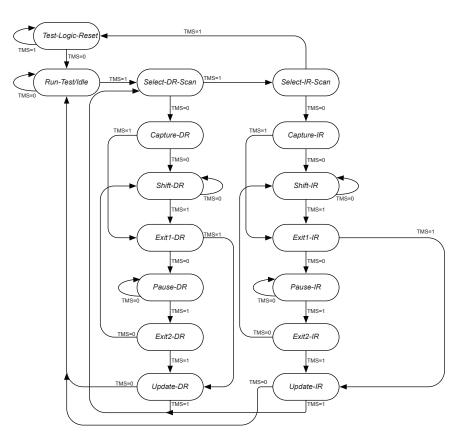

As seen in the figure, there are other registers that can be connected between TDI and TDO. The boundary register is made up of all the boundary cells, and it can be connected to the operational parts of the circuitry. Other registers such as the instruction register, the ID register, and the bypass register are not directly connected to the operational circuitry. The IEEE 1149.1 standard specifies that the TAP controller determines which register is connected between TDI and TDO and what data it shifts in and out of the TAP. The TAP controller is implemented as a 16-state finite state machine. A state diagram of the TAP controller is shown in *Figure 2-2*.

The labels on the state transition arrows are the values asserted on the TMS line by a JTAG controller such as National's SCANSTA101 STA master. To understand the operation of the TAP controller, what happens when the TMS line is held high for five clock cycles (this is called a "five high TMS reset") should be considered. Start from any state in the state diagram

Figure 2-1. Architecture of the IEEE 1149.1 Test Access Port (TAP)

Figure 2-2. State Diagram of the IEEE 1149.1 TAP Controller

and follow five transitions with the TMS line held high. The intermediate states through which the TAP controller state machine passes depend upon where it starts, but after five transitions with the TMS line held high the state machine will always be in the Test-Logic-Reset (TLR) state, and it will stay there as long as the TMS line is held high.

There are four "stable" states in the above diagram. These are states in which the TAP controller can remain for as many successive TCK cycles as desired by holding the TMS line at a given value. In these "stable" states, the only operations that occur in the TAP are operations that have been previously set up and activated. These states are Test-Logic-Reset, Run-Test/ Idle, Pause-Data-Register (Pause-DR), and Pause-Instruction-Register (Pause-IR). If the TAP controller is in any other state, it will either transition to a different state or it will shift data into the data or instruction register on the next TCK rising edge.

The Shift-Instruction-Register and Shift-Data-Register states are stable in a sense, in that the state machine can remain in these states as long as the TMS line is held low. When the TAP controller is in one of these states however, it is actively loading some register and the overall condition of the system is changing. For this reason, these states are not considered "stable" in the same sense that the four states previously described are considered stable.

Up to now only the TAP controller for a single device in the system implementing the IEEE 1149.1 TAP has been considered. For the case where there is only one boundary scan chain (i.e., where National's SCANSTA111 multiplexer or SCANSTA112 multiplexer is not used in the scan chain, or where these devices are used, but the multiple scan chains are all tied together), the TAP controllers for all the devices move from one state to the next in unison. If all the TAP controllers start out in the same state, they all remain in the same state. So it is really only necessary to consider a single TAP controller state for the entire scan chain.

With this state transition mechanism and the ability to shift data in and out of various shift registers, the IEEE 1149.1 TAP can produce a wide variety of complex behaviors. This provides a very powerful mechanism for in-system testing, programming, and diagnosis.

#### national.com/scan

Use of the IEEE 1149.1 TAP consists, in essence, of driving the TMS and TDI lines with the correct bit sequences to accomplish the desired functions, and monitoring the TDO line for the desired responses. These three lines and the test clock essentially comprise the IEEE 1149.1 boundary scan standard.

#### 2.3.3. Use of the IEEE 1149.1 TAP

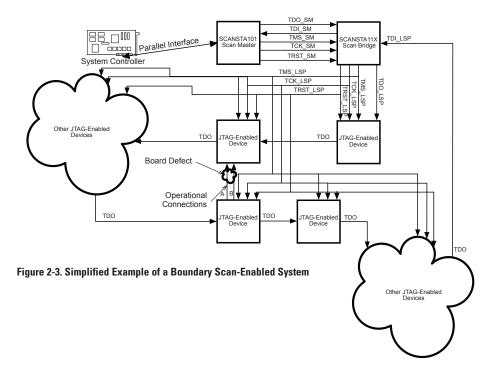

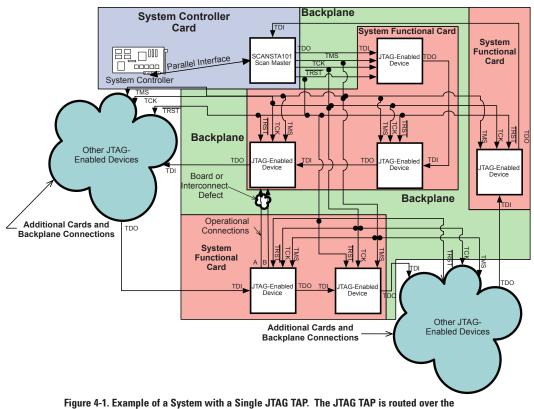

Given the simplicity of the architecture of the IEEE 1149.1 TAP, the question arises: What is its utility in a system? The answer is illustrated in the digital system example in *Figure 2-3*. The figure shows several devices implementing the IEEE 1149.1 TAP interconnected in an operational system. The desired functionality of the system is embodied in the interconnections between the input and output pins of the various devices. Even though the IEEE 1149.1 TAP pins are connected between the devices on the board, these connections could all, in principle, be removed without affecting the desired functionality of the system. This is a key point. The IEEE 1149.1 TAP is meant to function independently of what the system is otherwise designed to do.

The example of *Figure 2-3* is deliberately left generic and shown not to be greatly complex. Conceptually, however, a considerably more complex system could be represented in the same way as the system of *Figure 2-3*. Consider the connections labeled A and B in *Figure 2-3*. These connections might be traces on a printed circuit board, vias, wires, connectors, cables, or some combination of all of these. Suppose these two connections were shorted together because of some manufacturing defect in a particular unit. In this case, it is very likely that the unit would not work correctly, at least some of the time. Obviously the manufacturer of the system would prefer to identify and repair or discard the defective unit before it was shipped to a customer. This becomes even more critical as the system becomes more complex and, probably, more expensive. But it also becomes more difficult.

In a complex system, functional testing may not identify the problem with a faulty unit. Complex systems exhibit complex behaviors. (Simple systems can too, but complex systems almost always do. A complex system that exhibits simple behavior is likely to be replaced by a simpler system.) Testing a complex system to identify a manufacturing defect like the one described above by observing its normal functionality would require exercising enough of its complex behavior to ensure that some anomalous observation would occur should there be a manufacturing defect in the system. This becomes progressively more difficult, expensive, and time-consuming as the behavior of the system becomes progressively more complex. In addition, even if the presence of a given defect could be detected by observing some anomalous behavior in the system's normal functional environment, it is unlikely that the exact location and nature of the defect could be identified in this way. Many defects might produce the same anomalous observed behavior. As the system becomes more complex, just putting it through its normal operational paces becomes a less satisfactory method of testing and diagnosing faults.

What is really required to identify a manufacturing defect like that previously described is the ability to impose various signals at the driving nodes of connections A and B and to observe the signals received at the receiving nodes of those connections. If there is a defect in the connection, the received signal will be different from the driven signal. Also, if it is known which nodes were being driven and where the signals were being received, then it is also clear exactly which paths to examine in order to locate the defect.

This is what the IEEE 1149.1 TAP can do.

In principle, using the IEEE 1149.1 TAP, all of the driving boundary cells in the entire design (the ones that implement IEEE 1149.1 TAP, anyway) can be connected into a single, large shift register, and a desired data pattern can be shifted into that shift register. All of the receiving boundary cells can be connected in the same way into a large shift register (in practice, it's the same shift register for input and output boundary cells). The boundary cells can then be used to drive the desired data pattern onto the connections on the board and to receive the resulting pattern from the connections on the board. Then the received data can be shifted out of the receiving boundary cells and compared to the data that is expected.

If this is done for several different data patterns it is possible, in principle, to identify and isolate a large percentage of the possible faults in a system. Even in realistic, complex systems, fault coverage (the probability of identifying a defect this way) can be computed a-priori, and can approach 100%. If the system has device pins that are bidirectional (input and output), the pins can be exercised in both modes using different data patterns.

Problems can be diagnosed in the internal functionality of devices on the board by driving their input pins and observing their output pins using the boundary cells. Semiconductor devices are often tested this way in manufacturing. A device that implements the IEEE 1149.1 TAP can be tested after it has been installed in its target system application.

Programmable logic devices in the system also can be programmed using the IEEE 1149.1 TAP. The IEEE 1149.1 TAP provides a secondary I/O port to these devices and the IEEE 1149.1 standard is written to permit extensions of the standard to applications such as in-system programming.

All of this IEEE 1149.1 functionality can be implemented in the system itself, enabling self-test, health monitoring, and in-system programming updates. When this capability is integrated into the system itself, it requires a control mechanism of some sort and enough memory to store the required test patterns and expected data for comparison.

This is the application for which the SCANSTA101 STA master was designed and it is the subject of the present design guide. This will be described in more detail in the remainder of this guide.

# 2.4. Summary and Conclusions

As described in this introductory chapter, the IEEE 1149.1 TAP provides an independent mechanism for accessing the inputs and outputs of a device (at its "boundary"). In this way it enables precise and extensive testing for manufacturing defects in a system. It also permits extensive testing of individual devices either in a system or in isolation, as in a manufacturing test. It also permits in-system programming of programmable devices. These capabilities may be utilized by external equipment such as test systems or device programmers, or by devices within the system itself.

So far all the descriptions of the operation of the IEEE 1149.1 TAP have described low-level functionality; namely, functionality at the level of sequences of bits. This is analogous to the machine code that describes a computer program at the lowest level. The memory containing a computer program really just contains a sequence of bits. The meaning in the bit sequences is expressed when the computer retrieves them from memory and applies them to its (complex) internal structure.

Human beings could monitor and examine the bit sequences applied to the TDI and TMS pins of an IEEE 1149.1 TAP in order to understand the functions being performed by the TAP just as they might examine the bit sequences that make up a computer program. Extracting meaning from these bit sequences would be a difficult proposition in the general case. So one would do what human beings usually do in such cases – look for patterns and abstract common features from the low-level description represented by the bit sequences. This abstraction is inherent in the architecture of National's family of SCAN devices. How that abstraction is accomplished will be examined in this design guide.

#### national.com/scan

# 3.1. The SCANSTAEVK Demonstration Kit

National's family of boundary scan support devices provides a valuable built-in self-test capability for system implementations. National has developed a demonstration kit to help system designers evaluate the capability provided by this family of products.

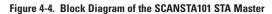

The demonstration kit includes a target board with two National boundary scan-enabled devices, a serializer and a deserializer, with relatively simple connections between them. It also includes a backplane with multiple JTAG port connections to accommodate multiple target boards and a set of intermediate boards for introducing the SCANSTA111 and SCANSTA112 JTAG multiplexers between the backplane and the target board. A PC-resident board with the SCANSTA101 STA master device for driving the JTAG ports completes the demonstration kit. In conjunction with the supplied, PC-based, vector delivery software, this demonstration kit can serve as a simplified model of a boundary scan-enabled operational system.

### 3.1.1. PCI-1149.1/101 SCANSTA101 PC Card

In an operational system implementing built-in self-test, a system controller would deploy test vectors to the boundary scan chain (or chains) by communicating, using simple parallel protocols, with one or more SCANSTA101 STA master devices. In the demonstration kit, the role of the system controller is emulated by a personal computer (PC). That the performance and characteristics of the PC are not important for the demonstration is one of the features that the demonstration kit is meant to illustrate.

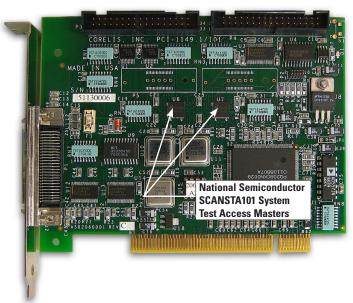

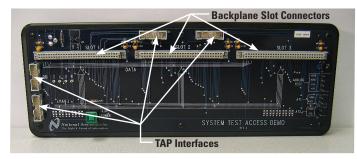

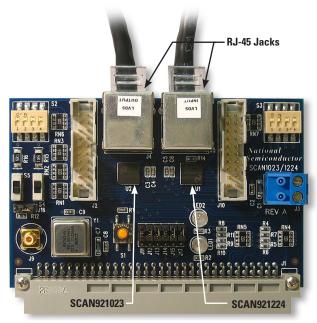

On the internal PCI bus of the PC in the demonstration system, which is running Windows, a Corelis PCI-1149.1/101 boundary scan controller is installed. A photograph of this device is shown in *Figure 3-1*. There are two National SCANSTA101 STA master devices on the PCI-1149.1/101.

The PC and the PCI-1149.1/101 boundary scan controller emulate the system controller and the SCANSTA101 STA master device in an operational system, but clearly an operational system would require much more limited capability to provide the builtin self-test function. The PC-based emulation subsystem used with the demonstration kit includes a GUI-driven vector delivery and evaluation software tool which communicates with the PCI-1149.1/101 using a low-level driver library supplied by Corelis. The driver library primarily provides simple functionality for reading and writing registers in the SCANSTA101 devices, just as it would be implemented in an operational system. In an operational system, the system controller would, when commanded to perform a system self-test, communicate with the in-system SCANSTA101 STA master. In such a system, all the system controller would be required to do is perform a sequence of register reads and writes via a 16-bit parallel data bus and an associated 5-bit register address bus to the SCANSTA101 STA master device. The sequence of register reads and writes would be stored on board in a compact binary format called Embedded Vector Format 2 (EVF2). An embedded software function, provided by National in source code form, would provide the interface between the EVF2 format and the SCANSTA101 STA master device. As will be demonstrated in this design guide, the PC and the PCI-1149.1/101 boundary scan controller emulate this functionality in an instructive manner.

Figure 3-1. The Corelis PCI-1149.1/101 JTAG Controller Card with Multiple National SCANSTA101 STA Master Devices

#### 3.1.2. SCANSTAEVK Demonstration Kit Backplane

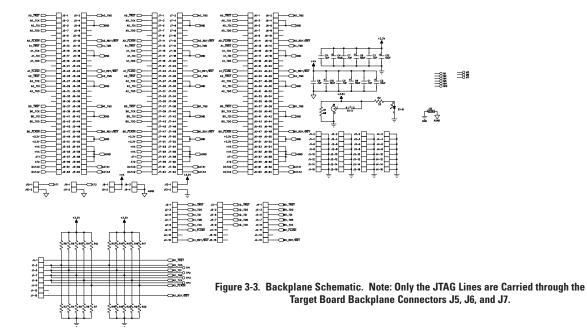

An operational system might include a backplane designed to provide connections between the various functional boards in the system. In such an operational system, the system controller, and perhaps the SCANSTA101 STA master device, might be located on a master board and might test the other boards in the system by communicating with them over the backplane. Such a backplane would have multiple connections for various functional boards, and each such connection would include lines for the JTAG TAP. The SCANSTAEVK backplane emulates this functionality. A photograph of the SCANSTAEVK backplane is shown in *Figure 3-2*. A schematic of the backplane is shown in *Figure 3-3*. This backplane is intended to demonstrate JTAG functionality. Accordingly, only the JTAG TAP lines are carried across the backplane, through the target card connectors, and to the target cards. In an operational system, signals associated with the primary function of the system would also be transported across the backplane and through the target card connectors. The SCANSTAEVK backplane, however, provides a realistic platform for testing the JTAG functionality. It is a key point of the IEEE 1149.1 JTAG standard that the TAP implemented in a device is independent of the primary function of the device. A backplane that does nothing but transport TAP signals is a reasonable vehicle for the development of a boundary scan built-in test application.

Figure 3-2. SCANSTAEVK Demonstration System Backplane with Three Target Card Connectors and Multiple JTAG Controller Ports

As can be seen in the schematic of *Figure 3-3*, there are multiple TAP interface connectors on the board for TAPs labeled A0, A1, A2, and B0. The Serializer/Deserializer (SerDes) target boards have multiple TAP connections which can be configured by jumpers on the board. When these target boards are used with a JTAG multiplexer card, such as the one carrying the SCANSTA111 multiplexer, the active JTAG port on the target card is selected through the multiplexer. When a multiplexer is not used, all the scan ports on the target card can still be exercised by using different TAP interface connectors.

Associated with the A0 and A1 TAPs are signals labeled, for example, A0\_FLASH\* and A0\_RDY/BSY\*. These are auxiliary signals passed through the multiplexer when it is used. They are intended as general-purpose I/Os, each associated with either a single local scan port from the multiplexer or with the backplane TAP connector. These I/Os are not used in the SCANSTAEVK demonstration system described in this design guide.

#### 3.1.3. SCANSTA111 Intermediate Board

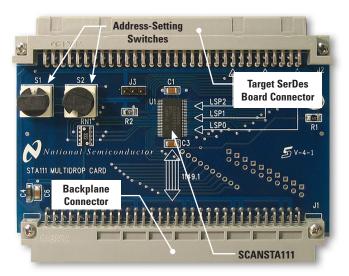

Inserted between the backplane connector and the target board in the demonstration system is an intermediate card carrying a SCANSTA111 Scan Bridge JTAG multiplexer. The card has a plug that fits the backplane connector and a socket with the same connection configuration as the backplane connector into which one of the target boards may be inserted. The Scan Bridge card intercepts the input A0 TAP from the backplane and routes it to the SCANSTA111 multiplexer. The outputs of the multiplexer are then routed to the A0, A1, and A2 TAP connections on the target board connector.

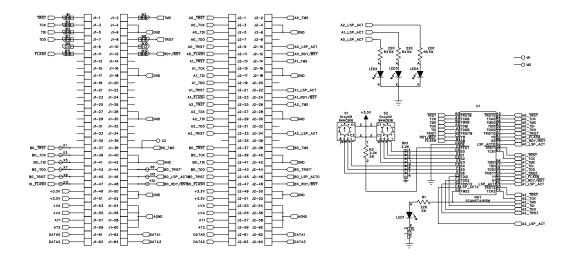

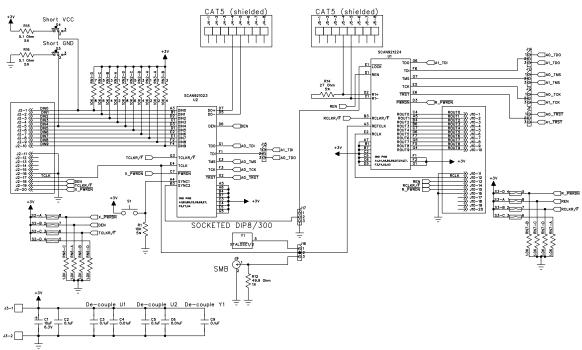

A photograph of the intermediate Scan Bridge multiplexer card is shown in *Figure 3-4*. A schematic of the card is shown in *Figure 3-5*. On this card, J1 is the backplane connector. It makes connection only to TAPs A0 and B0. TAP A0 is routed on the card to the backplane master TAP of the SCANSTA111 multiplexer. B0 is routed directly to the output connector J2 for use in cases where it is desired to bypass the SCANSTA111 multiplexer.

Figure 3-4. Intermediate Scan Bridge Multiplexer Card. Note the Address-Setting Switches on the Card and the Pass-Through Connector Arrangement.

The address of the SCANSTA111 multiplexer itself is set by switches S1 and S2. Selection of the SCANSTA111 multiplexer is accomplished by scanning an address matching the switch settings into the SCANSTA111 multiplexer's instruction register via the JTAG TAP.

Scan ports A0, A1, and A2 on the output connector, J2, are connected to the local scan port outputs of the SCANSTA111 multiplexer. The SCANSTA111 output port is selected by writing to the registers of the SCANSTA111 multiplexer through its JTAG master port, A0.

The selected local scan port of the SCANSTA111 multiplexer is routed out to the target card through the output connector. The connections on the output connector match those on the backplane. The target card can be connected directly to the backplane or to the output connector of the intermediate Scan Bridge card with no effect on the TAP operation of the target card. The software and the SCANSTA101 STA master must be aware of the SCANSTA111 multiplexer in order to control it and to account for the additional 1-bit delays it introduces in the TAP signaling, but the target card does not need to be aware of the presence of the SCANSTA111 multiplexer. As far as the target card is concerned, the Scan Bridge card is transparent.

Figure 3-5. Schematic of the Intermediate Scan Bridge Multiplexer Card

#### 3.1.4. Target SerDes Board

In the SCANSTAEVK demonstration system, the target SerDes board models the board to be tested using a built-in self-test in an operational system. The board includes National's serializer/ deserializer pair, the SCAN921023/SCAN921224<sup>8</sup>, both of which implement boundary scan. The SCAN921023 is an embedded clock 10-bit Low-Voltage Differential Signaling (LVDS) serializer. All of its digital inputs and outputs, including its primary differential LVDS output, are equipped with boundary scan cells. Similarly, the SCAN921224 is an embedded clock 10-bit LVDS deserializer designed to work with the SCAN921023 serializer. It, too, is equipped with boundary scan cells on all of its inputs and outputs including its primary differential LVDS input.

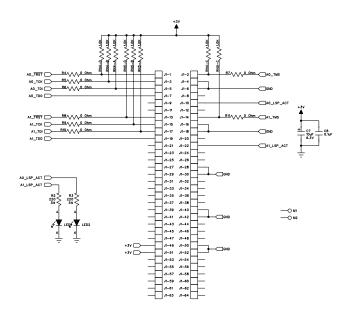

A photograph of the target SerDes board is shown in *Figure 3-6.* The two-page schematic for the board is shown in *Figure 3-7* and *Figure 3-8.* Reviewing the schematic will provide an indication of what could, in principle, be tested on this board if designing a built-in self-test.

Figure 3-6. Target SerDes Board. The SCAN921023 Serializer and SCAN921224 Deserializer on this Board implement the JTAG Boundary Scan TAP.

Figure 3-7. Target SerDes Board Schematic (Part 1). The Boundary Scan-Enabled Devices are the SCAN921023 Serializer and the SCAN921224 Deserializer.

# **Test System Description**

Figure 3-8. Target SerDes Board (Part 2). This Part shows the Backplane Connector.

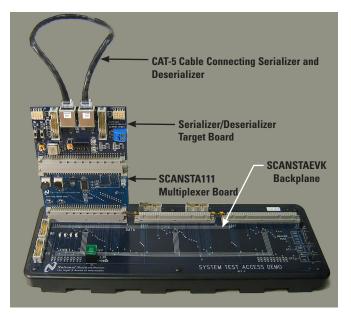

Figure 3-9. Complete Stackup for the SCANSTAEVK Demonstration Platform. This Stackup includes the Backplane, the Intermediate SCANSTA111 Multiplexer Board, and the SerDes Target Board. Note the CAT-5 Cable connecting the Serializer and Deserializer on the Target Board.

First, the parallel digital inputs on the SCAN921023 serializer, DIN0:DIN9, should be considered. If a data source isn't connected on connector J2, these inputs are all pulled up to +3V through RN1, RN2, and RN3. So detecting static high-input levels on these inputs to the SCAN921023 device should be possible, and, if detection is unsuccessful, that will indicate a fault in one of the resistor arrays or in one of the input lines. It is possible to introduce a fault deliberately by changing the setting of S5, and it should be possible to detect that deliberately-introduced fault.

Both the SCAN921023 serializer and the SCAN921224 deserializer have three inputs tied to static high levels by switches S2 and S3. The inputs are a PWRDN\* input, an enable input, and a rising/falling edge clock selection input. All three are held high in normal operation, so it should be possible to detect static high levels on these input pins. If the settings of these switches are changed, it should be possible to detect the fault that this introduces.

The Sync1 input of the SCAN921023 serializer is tied low through a pull-down resistor unless a fault is introduced by depressing momentary switch S1. If this switch is depressed, detection of the fault should be possible.

The LOCK\* output of the SCAN921224 deserializer can be connected by jumper J17 to the Sync2 input of the SCAN921023 serializer. If this connection is made, then it should be possible to drive this line from an output scan cell on the SCAN921224 deserializer and receive the signal driven at the SCAN921023 serializer. If the jumper is removed, a fault will be introduced (if looking for the presence of the jumper) that should be detectable.

Finally, a fault can be introduced in the connection between the serializer and deserializer on the SerDes target board. The SCAN921023 serializer has a differential LVDS output. The SCAN921224 deserializer has a differential LVDS input. In an operational system, the function of these two devices is to provide a two-wire serial data path between distant points in the system. Parallel data goes in to the SCAN921023 serializer and comes out as serial data. The serial data is routed to the SCAN921224 deserializer where it is recovered and output to the receiving system as parallel data. A serializer/deserializer pair in a system is used to reduce the number of connections needed to transmit data between distant points in the system.

In normal operation the differential LVDS output of the SCAN921023 serializer (DO+ and DO-) is connected through a cable to the differential LVDS input of the SCAN921224 deserializer (RI+ and RI-). In the SCANSTAEVK demonstration kit, this connection is made by means of a CAT-5 cable with RJ-45 connectors.

The differential LVDS output and input pins on the SCAN921023 serializer and SCAN921224 deserializer are equipped with differential boundary scan output and input cells, respectively. If a test pattern is generated that tests this connection between the two devices and then the cable is removed, detection of the resulting fault should be possible.

#### 3.1.5. Demonstration Kit Summary

If the SerDes target board of the SCANSTAEVK demonstration kit is used to model an operational system board then it is possible, by inspecting the schematic, to get an indication of what elements of the board structure are possible to test. In the case of this board, there is not much that can be tested some static inputs to the two boundary scan-enabled devices and a couple of interconnects between them, including one differential LVDS interconnect.

Even though this model is highly simplified in comparison to any real operational board, it does capture many instructive features of the boundary scan built-in self-test problem. It also has the advantage that, since it is quite simple, it may be possible to trace the development of the boundary scan test procedures and thereby gain some insight into how these tests are developed and how the test development software works.

The SCANSTAEVK demonstration kit includes the SCANSTA101 STA master JTAG controller and the SCANSTA111 Scan Bridge multiplexer. Using the SCANSTAEVK demonstration kit as a model for an operational system will allow better understanding of the operation of these devices as well.

# 3.2. Test Development and Deployment Software

Designing and building the hardware to support built-in self test, and hooking up the test access ports properly, is only the first step in developing a built-in self-test. The SCANSTAEVK demonstration kit described previously was designed by National to illustrate the operation of National's SCAN family of devices. It should be noted, however, that if such a system were designed from scratch, it would be necessary to know very little about the boundary scan operation to take the design to this point. All that was needed was to connect the TAP properly between the boundary scan-enabled devices.

It would not have been necessary to know anything about the boundary scan operation in order to use the SCANSTA111 Scan Bridge multiplexer either. The design was simply a matter of connecting the backplane TAP and one or more of the local scan ports of the device properly. Also, it was not necessary to know anything about the boundary scan operation to implement the SCANSTA101 STA master either. It was only necessary that the SCANSTA101 STA master was connected to the correct address and data lines on the parallel processor interface side and to the TAP on the serial scan interface side.

This is an important point. What this means is that the hardware for a boundary scan-enabled system can be designed and fabricated well before any details of the boundary scan operation and the software required to implement it are known. The interfaces to the boundary scan-enabled devices, specified in IEEE 1149.1, and the interfaces to National's family of boundary scan support devices are all sufficiently well described and specified so that the hardware design and the software design can proceed almost independently; and the hardware can proceed first, which is good, because it probably takes longer to fabricate the hardware than to generate a first cut at the software (although it probably takes longer in the end to get the software fully debugged than it does to get the hardware working).

In the modeling exercise, however, the point has been reached where the software can no longer be ignored. The system can, in principle, perform a built-in self-test. So the question becomes: What is needed in order to implement this test?

#### 3.2.1. Automatic Test Pattern Generation

All of the board faults have been described that could, in principle, be detected using a boundary scan built-in self-test. But how can these faults be detected in practice? What is needed is to scan in an appropriate pattern of bits into the boundary registers of the JTAG-enabled devices so that the outputs are correctly set, capture the pattern of bits at the inputs of these devices, and compare this to the expected data pattern. Conceptually it will probably take more than one cycle of setting the outputs and measuring the inputs to be sure that all the kinds of faults are detected that should be possible to detect. And this is a very simple board. How much more complicated will the process become when it is used on a more complex operational board?

The answer to these questions is an Automated Test Pattern Generator (ATPG) software tool. These tools are made by various manufacturers including Corelis, Flynn Systems, JTAG Technologies, Asset Intertech, and others. The tools are all different in their look and feel but all do the same job; namely, they generate test patterns that can be applied to the JTAG TAP to detect all or most of the faults that can, in principle, be detected on a JTAG-enabled board.

An example of generating test patterns with these tools will be discussed in Chapter 5, but for now it is sufficient to say that the next step is to take a description of the board (a netlist), descriptions of the boundary scan-enabled components on the board (Boundary Scan Description Language or BSDL files), and some additional information like jumper settings and cable connections which are not on the netlist, and to use one of these tools to generate a set of test vectors for the board.

The ultimate output of this process is a Serial Vector Format (SVF) file, which describes the operations to be performed by the TAP in a human-readable format. Once the SVF file is created, the next step is to convert the SVF file to an Embedded Vector Format 2 (EVF2) file which can be deployed to the SCANSTA101 STA master.

The SVF file produced for the target SerDes board will be discussed in some detail in Chapter 7. For now, however, it is important to note that the first software-intensive step in the process is to generate a SVF file using a third-party ATPG tool.

#### 3.2.2. Conversion to EVF2 Format

A SVF file contains instructions like STATE, which directs the TAP state machine to transition to a specified state, Scan Data Register (SDR), which scans data into and out of the TAP, Scan Instruction Register (SIR), which scans an instruction sequence into and out of the TAP, and other similar instructions. These are descriptive and complete, but the SCANSTA101 STA master requires instructions interpreted as a sequence of register reads and writes. This is the purpose of the EVF2 format.

The EVF2 format is a binary format consisting of data records that describe what data is to be written to what register in the SCANSTA101 STA master in order to accomplish each of the test sequences described in a SVF file. The binary format means that the EVF2 file consumes minimal storage in the embedded system's memory, an important feature for built-in self-test applications. National provides source code to be embedded in the system processor's code (actually this is just one C function) that interprets the EVF2 file records and sends out the appropriate address and data bits to set up the SCANSTA101 STA master.

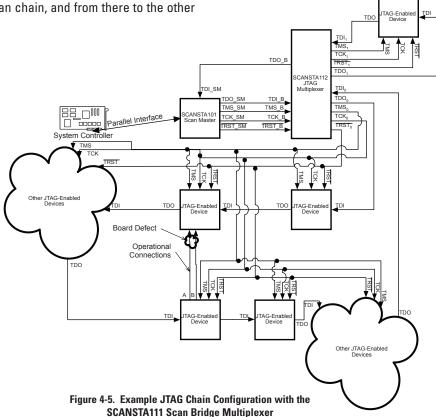

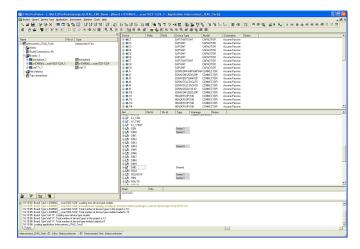

The conversion to EVF2 format is accomplished by a program supplied by National called EVF Workbench. A screen shot of

the main window is shown in *Figure 3-10*. An example of using the simple interface of EVF Workbench will be highlighted in Chapter 5. For now, however, the next step after producing the SVF file is to convert it to an EVF2 file using EVF Workbench.

| File Help                                                                                                                                                                                                         |                                                                                                                          |                                                                  |                                                                     |   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------|---|

| Configuration File<br>Config File<br>FILES\STA101.CFG Browse                                                                                                                                                      | SVF To EVF Conversion Options<br>Suppress Warnings and/or Error:<br>Suppress Warnings Suppre                             |                                                                  |                                                                     |   |

| Input SVF File<br>Input SVF File<br>VTERCONNECT.SVF<br>Browse<br>Output EVF File<br>Output EVF File                                                                                                               | Byte Order Option  Use Default (Platform Order)  Load-On-The-Fly Option  Force Load-On-The-Fly Assumed Initial TAP State | O Use Little Endian                                              | O Use Big Endian                                                    |   |

| VTERCONNECT.EVF Browse                                                                                                                                                                                            | OUNK - Unknown or Undefined     ORTI - Run Test Idle     OPDR - Pause DR     OSDR - Shift DR                             | O TLR - Test Logic Reset<br>O PIR - Pause IR<br>O SIR - Shift IR |                                                                     |   |

|                                                                                                                                                                                                                   | Desired Final TAP State UNK - Unknown or Undefined RTI - Run Test Idle PDR - Pause DR SDR - Shift DR                     | O TLR - Test Logic Reset<br>O PIR - Pause IR<br>O SIR - Shift IR |                                                                     |   |

| SEMICONDUCTOR CORPLEVF_WOR<br>CORPLEVF_WORKBENCH(EVF_DEM<br>NOTE: Converter version 2.100<br>NOTE: Generating ST101<br>********** Configuration Settings                                                          | IKBENCHISVF_DEMO_FILESUINTERCO<br>O_FILESUINTERCONNECT.EVF" -QW -                                                        | NNECT.SVF" "C:\PROGRAM FI                                        | TA101.CFG" "C:IPROGRAM FILESINATIONAL<br>LESINATIONAL SEMICONDUCTOR | î |

| CockDivider = 32<br>ClockFrequency = 33.3E+6<br>DeviceType = 5T101<br>EmulateUrmosiledCompare = true<br>MaximumNectors = 16<br>MaximumNectors = 4<br>ScanBridgeSupport = false<br>SequenceThterruptEnable = false |                                                                                                                          |                                                                  |                                                                     |   |

Figure 3-10. Main Window of EVF Workbench

After the file is converted to EVF2 format, it is possible to convert it to a human-readable representation of the EVF2 format. Normally this is neither required nor useful, but, in this case, it will provide some additional insight into how the SCANSTA101 STA master controls the self-test. A decompiled EVF2 file will be examined in Chapter 7.

#### 3.2.3. Embedded Platform Software

Once these operations are complete, an EVF2 file is produced that details the register reads and writes required for the SCANSTA101 STA master to perform the desired built-in selftest. There must be some system processing power somewhere (a system controller, a DSP engine, a FPGA, or something else) that can drive the address and data lines of the SCANSTA101 STA master to perform the desired built-in self-test.

For systems with an embedded controller programmed in C or C++, National provides a function library that implements a simple Application Programming Interface (API) for delivery of the EVF2 file. It consists of a single user-called function and some additional glue functions to implement it. Following is the function's argument list.

Most of the arguments to this function are function pointers to user-supplied, application-specific functions that handle the low-level operations of reading from memory and writing to the parallel address and data buses. This source code is added to the embedded processor code. When this function is called, at the appropriate time, it uses the passed function pointers to deliver the EVF2 file to the parallel port connected to the SCANSTA101 STA master.

In the demonstration system, this function is implemented in the PC software that controls the PCI-1149.1/101 card with the SCANSTA101 STA master on it. This implementation will be discussed in Chapter 6 and some analogies will be drawn between this implementation and a typical embedded application.

#### 3.2.4. ScanVec

ScanVec is the PC application that reads an EVF2 file (from disk) and delivers the vector information to the SCANSTA101 STA master on the Corelis PCI-1149.1/101 card. This is the equivalent, for the purposes of this design guide, of the embedded software in an operational system. This is the program that reads and writes the correct SCANSTA101 STA master registers to perform the built-in self-test. In Chapter 8, the use of ScanVec will be described along with what it looks like when the self-test completes successfully and when it detects a fault.

The designer of a system with boundary scan-based built-in self-test might use ScanVec as a debugging tool in the early stages of development. It must be emphasized, however, that the functions performed by ScanVec in this demonstration system would be performed by an embedded controller in an operational system which implements boundary scan-based self-test.

#### 3.3. Summary

The SCANSTAEVK demonstration kit and the associated software is meant to model, in a simplified way, an operational system implementing boundary scan-based built-in self-test. All of the elements required are present. There is a model of the application board which is to test itself, the target SerDes board. There is a Scan Bridge multiplexer such as might be used to isolate the scan chains in the target application. There is a SCANSTA101 STA master JTAG controller which performs the low-level JTAG TAP port manipulations to carry out the built-in self-test. And there is a system backplane over which the test vectors are delivered, just as there might be in an operational system.

The test patterns are generated by ATPG software just as they would be for an operational system. The test pattern output is converted to EVF2 format just as it would be for an operational system. And, just as in an operational system, a system controller delivers the EVF2 file to the SCANSTA101 STA master over parallel address and data buses by reading and writing the appropriate registers and memory locations.

Producing and deploying test vectors for built-in self-test of this simplified system should provide valuable insight into the process required to do the same thing in an operational system. The following sections of this design guide will describe the process of designing and implementing a built-in self-test and dissect the results in some detail. The intent is to provide a deeper understanding of the boundary scan development and deployment process. The SCANSTAEVK demonstration kit used as a test platform for this work was designed several years ago as a demonstration vehicle for National's family of JTAG support devices. The primary focus of the present effort was to develop and deploy a test vector sequence for use on this hardware in the same way that a system designer would for an operational system. Still, it is instructive to examine some of the considerations involved in the hardware design required for built-in self-test. The SCANSTAEVK demonstration kit will be treated as if it were designed today from scratch.

# 4.1. System Function and Built-In Self-Test

Built-in self-test is clearly always an adjunct to the primary function of a board or subsystem. So the first step in designing a board which will include built-in self-test is to design the board to perform its primary function. The IEEE 1149.1 boundary scan test standard is focused on providing test capability without compromising the primary function of the board or subsystem under test. Ideally, at the beginning of the design cycle, it should not be necessary for the system designer to consider built-in self-test at all.

National's family of boundary scan support devices was designed with this philosophy in mind. It is almost possible to add boundary scan support at the very end of the schematic design process, just before going to board layout. As a practical matter, of course, some consideration must be given to boundary scan earlier in the design process.

### 4.1.1. Selection of JTAG-Enabled Devices

It is obvious, though worth stating, that boundary scan is primarily capable of testing interconnects between devices that are equipped with the IEEE 1149.1 TAP. Testing of other interconnects is possible with boundary scan, but the test sequence becomes more complicated. Some ATPG tools can generate automatic test sequences for memory devices and for simple combinatorial logic. But the first requirement in designing a board for built-in self-test is to choose devices, to the extent possible, that are equipped with the IEEE 1149.1 TAP.

National has implemented the IEEE 1149.1 TAP on many devices, and the serializer/deserializer pair on the SCANSTAEVK SerDes target board are a good example. The SCAN921023 serializer and SCAN921224 deserializer are designed for boundary scan testing with input boundary scan cells on all of the CMOS digital inputs and output boundary scan cells on all of the CMOS digital outputs. In addition, these devices have differential boundary scan cells on their primary LVDS inputs and outputs. They also have built-in self-test modes that transmit known data patterns from the serializer to the deserializer to test the primary LVDS link at operational speed. This is an extension to the standard boundary scan tests. If this sort of at-speed test is desired, it must be added explicitly to the system test vectors.

The SCANSTAEVK SerDes target board is an ideal candidate for built-in self-test in this sense because all of the integrated circuits on the board (admittedly, there are only two of them) are equipped with the IEEE 1149.1 TAP.

#### 4.1.2. Selection of JTAG Support Devices

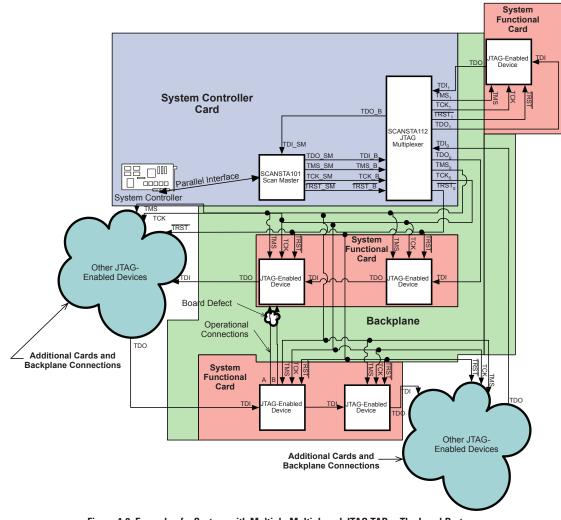

In order to implement board built-in self-test using National's family of JTAG support devices, a few preliminary system-level decisions must be made.

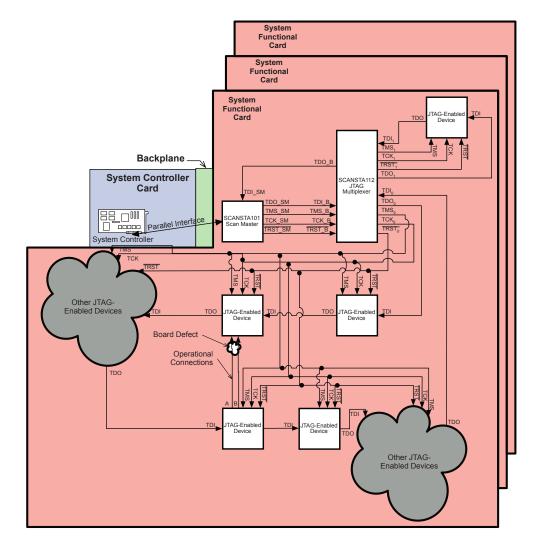

First is the location of the SCANSTA101 STA master. For many applications, locating this device at a single primary location on the backplane (on the system controller board, for example) will work fine. The limitation of this approach is that a single SCANSTA101 STA master can only drive one set of test vectors at a time. Even if a Scan Bridge multiplexer is located on the same card as the SCANSTA101 STA master, providing multiple JTAG scan chains on the backplane, either only one of the scan chains will be active at a time or all the scan chains will be doing the same thing. For systems where it is important that built-in self-test be performed as fast as possible, it may be preferable to locate a SCANSTA101 STA master on each board in the system. Once these devices are set up by the system controller, they can perform the required self-tests autonomously and report the results back to the system controller. This allows testing of the entire system in the fastest possible manner.

Once the decision has been made regarding how many STA masters to use and where to locate them, board space and power from the power supply must be allocated for these devices. This is done in the early stages of the system design.

The SCANSTA101 STA master is designed to require very little additional external logic, but depending upon the system design, some signal conditioning on the parallel processor interface handshake lines might be required. The system designer should have an architecture in mind for connecting the SCANSTA101 STA master(s) to the system controller and for accomplishing this handshaking. If external logic is anticipated, provision should be made for it early in the system design.

The next consideration is the implementation of multiple scan chains using the Scan Bridge multiplexers. If the decision of

how to implement the STA masters has implications for the speed of testing the entire system, the implementation of the Scan Bridge multiplexers has implications for the speed of testing any part of the system independently. A board with many JTAG-enabled devices and many interconnections to be tested might require a very long test time if the devices are connected in a single scan chain. It might be advantageous in this situation to implement multiple scan chains on this board using the SCANSTA111 or SCANSTA112 Scan Bridge multiplexers.

Considerations in the deployment of the Scan Bridge multiplexers include whether there are sections of the board with few operational interconnects between them. If there are sets of devices on the board that perform relatively independent functions in the operational system, these might be good candidates for local scan chains. Additionally, if the JTAG TAP is to be used to program a programmable logic device such as a FPGA, it will speed up the programming process to put the programmable logic device alone on a dedicated local scan chain. This will also simplify the programming of the device.