During some initial testing with the TPS65987D we found what appears to be an error in the datasheet.

According to the datasheet the I2C address for I2C1, and I2C2 are defined as follows:

Table 2. I<sup>2</sup>C Default Unique Address I2C1

| Default I <sup>2</sup> C Unique Address                                                                              |       |       |       |                         |       |       |       |

|----------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------------------------|-------|-------|-------|

| Bit 7                                                                                                                | Bit 6 | Bit 5 | Bit 4 | Bit 3                   | Bit 2 | Bit 1 | Bit 0 |

| 0                                                                                                                    | 1     | 0     | 0     | I2C_ADDR_DECODE[2:0] RA |       |       | R/W   |

| Note 1: Any bit is maskable for each port independently providing firmware override of the I <sup>2</sup> C address. |       |       |       |                         |       |       |       |

For the I2C2 interface, the unique I2C address is a fixed value as shown in Table 3.

Table 3. I<sup>2</sup>C Default Unique Address I2C2

| Default I <sup>2</sup> C Unique Address                                                                               |       |       |       |       |       |       |       |

|-----------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| Bit 7                                                                                                                 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| 0                                                                                                                     | 1     | 1     | 1     | 0     | 0     | 0     | R/W   |

| Note 1: Any bit is maskable for each port independently, providing firmware override of the I <sup>2</sup> C address. |       |       |       |       |       |       |       |

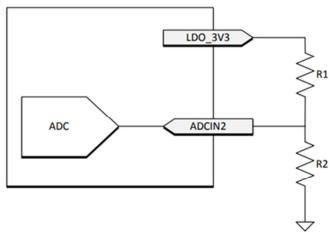

Figure 32. I<sup>2</sup>C Address Divider

Table 4 lists the external divider needed to set bits [3:1] of the I<sup>2</sup>C Unique Address.

Table 4. I<sup>2</sup>C Address Selection

| DI      | DIV = R2/(R1+R2) <sup>(1)</sup> |                 |  |  |  |

|---------|---------------------------------|-----------------|--|--|--|

| DIV_min | DIV_max                         | I2C_ADDR_DECODE |  |  |  |

| Sh      | Short ADCIN2 to GND             |                 |  |  |  |

| 0.20    | 0.38                            | 001b            |  |  |  |

| 0.40    | 0.58                            | 010b            |  |  |  |

| Short   | Short ADCIN2 to LDO_3V3         |                 |  |  |  |

Based on our testing though, I2C2 is behaving as I2C1 from and address perspective.

If "ADCIN2" is 3.3V I2C2 ACK's at 0x23, If "ADCIN2" is 0.0V I2C2 ACK's at 0x20.

This is what I would expect if we were interfacing to I2C1.

But since we are connected to I2C2. ADCIN2 should have no effect on I2C2 address, which based on the table should be fixed at 0x38.

Let me know what you think, and if I am missing something.