#### www.ti.com

## **Typical Application (continued)**

Added trace resistance/capacitance can reduce maximum frequency capability; use layout practices as directed in *Layout*.

### 9.2.2 Detailed Design Procedure

The 4-bit bus is connected directly to the 1A, 2A, 3A, and 4A ports (known as the xA port) on the SN74CBTLV3257, which essentially splits it into two busses, coming out of the xB1 and xB2 ports. When S is high, xB1 is the active bus, and when S is low, xB2 is the active bus. This means that Device 1 is connected to the bus controller when S is high, and Device 2 is connected to the bus controller when S is low. This setup is especially useful when two devices are hard coded with the same address and only one bus is available. The OE connection can be used to disconnect all devices from the bus controller if necessary.

The 0.1-µF capacitor on V<sub>CC</sub> is a decoupling capacitor and should be placed as close as possible to the device.

## 9.2.3 Application Curve

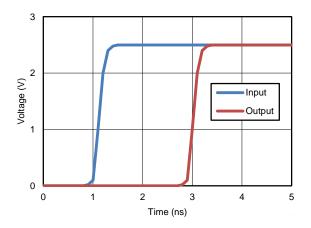

Propagation Delay ( $t_{pd}$ ) Simulation Result at V<sub>CC</sub> = 2.5 V.

# **10** Power Supply Recommendations

The power supply can be any voltage between the minimum and maximum supply voltage rating listed in the *Recommended Operating Conditions* table.

Each V<sub>CC</sub> terminal should have a good bypass capacitor to prevent power disturbance. For devices with a single supply, a 0.1- $\mu$ F bypass capacitor is recommended. If multiple pins are labeled V<sub>CC</sub>, then a 0.01- $\mu$ F or 0.022- $\mu$ F capacitor is recommended for each V<sub>CC</sub> because the V<sub>CC</sub> pins are tied together internally. For devices with dual-supply pins operating at different voltages, for example V<sub>CC</sub> and V<sub>DD</sub>, a 0.1- $\mu$ F bypass capacitor is recommended for each supply pins. To reject different frequencies of noise, use multiple bypass capacitors in parallel. Capacitors with values of 0.1  $\mu$ F and 1  $\mu$ F are commonly used in parallel. The bypass capacitor should be installed as close to the power terminal as possible for best results.

# 11 Layout

### **11.1 Layout Guidelines**

Reflections and matching are closely related to the loop antenna theory but are different enough to be discussed separately from the theory. When a PCB trace turns a corner at a 90° angle, a reflection can occur. A reflection occurs primarily because of the change of width of the trace. At the apex of the turn, the trace width increases to 1.414 times the width. This increase upsets the transmission-line characteristics, especially the distributed capacitance and self–inductance of the trace which results in the reflection. Not all PCB traces can be straight and therefore some traces must turn corners. Figure 2 shows progressively better techniques of rounding corners. Only the last example (BEST) maintains constant trace width and minimizes reflections.

Copyright © 1997–2015, Texas Instruments Incorporated