# PRODUCT SPECIFICATION

## **TFT LCD MODULE**

MODEL: KWH070KQ40-F09 Version: 1.0

|      | 1 | <b>Preliminary Specification</b> |

|------|---|----------------------------------|

| lack | 1 | Finally Specification            |

| CUSTOMER'S APPROVAL |       |

|---------------------|-------|

| SIGNATURE:          | DATE: |

|                     |       |

•It signifies that you fully understand and accept all the contents of this specification if you sign and send back the first page of this specifications.

| Designed by | R&D Checked by | Quality Department by | Approved by |

|-------------|----------------|-----------------------|-------------|

| LEO         |                |                       |             |

### **Prepared By:**

### FORMIKE ELECTRONIC CO.,LTD

Address: Flat 401-403, 4th Floor, Block B, iPARK Building, DengLiang Rd.,No.26, NanShan District, ShenZhen, 518054,China

TEL:(86) 755 88306921,88306931 FAX:(86) 755 88304615

Http://www.wandisplay.com

• This specification is subject to change without notice. Please contact FORMIKE or it's representative before designing your product based on this specification.

# **Table Of Contents**

| List | Description                            | Page No. |

|------|----------------------------------------|----------|

| 0    | Cover                                  | 1        |

| 0    | Table Of Contents                      | 2        |

| 1    | Revision Record                        | 3        |

| 2    | General Description                    | 4        |

| 3    | External Dimensions                    | 5        |

| 4    | Interface Description                  | 6        |

| 5    | Absolute Maximum Ratings               | 7        |

| 6    | Electrical Characteristics             | 7        |

| 7    | Timing Characteristics                 | 8        |

| 8    | Backlight Characteristics              | 9        |

| 9    | Optical Characteristics                | 10       |

| 10   | Reliability                            | 12       |

| 11   | Inspection Criterion                   | 13       |

| 12   | Precaution Relating & Product Handling | 17       |

| 13   | Others                                 | 18       |

# Revision record

| VER NO. | VER DATE   | CONTENTS  | Note  |

|---------|------------|-----------|-------|

| 1.0     | 2018-05-25 | NEW ISSUE | Leo   |

|         |            |           |       |

|         |            |           |       |

|         |            |           | \ \ \ |

|         |            |           |       |

|         |            |           | 9     |

|         |            |           |       |

|         |            |           |       |

|         |            |           |       |

|         |            |           |       |

|         |            |           |       |

|         |            |           |       |

|         |            | X         |       |

|         |            |           |       |

|         |            |           |       |

|         |            |           |       |

|         |            | >         |       |

|         |            |           |       |

|         |            |           |       |

|         |            |           |       |

|         | , 7        |           |       |

|         |            |           |       |

www.wandisplay.com 3/18 Ver.1.0

# 2. General Description

## 2.1 Description

KWH070KQ40-F09 is a Transmissive type color active matrix liquid crystal display (LCD), which uses amorphous thin film transistor (TFT) as switching devices. This product is composed of a TFT LCD panel, driver IC, FPC and backlight unit. The following table described the features of FORMIKE KWH070KQ40-F09.

## 2.2 Application

PDA,GPS, Multimedia products and other electronic Products Etc.

#### 2.3 Features:

| Features         | Description                     | UNITS |

|------------------|---------------------------------|-------|

| LCD type         | 7.0"TFT                         |       |

| Dot arrangement  | 1024 (RGB) ×600                 | dots  |

| Driver IC        | EK79001HB & EK73215BCGA         |       |

| Color Depth      | 16.7M                           |       |

| Interface        | LVDS                            |       |

| View Direction   | ALL                             |       |

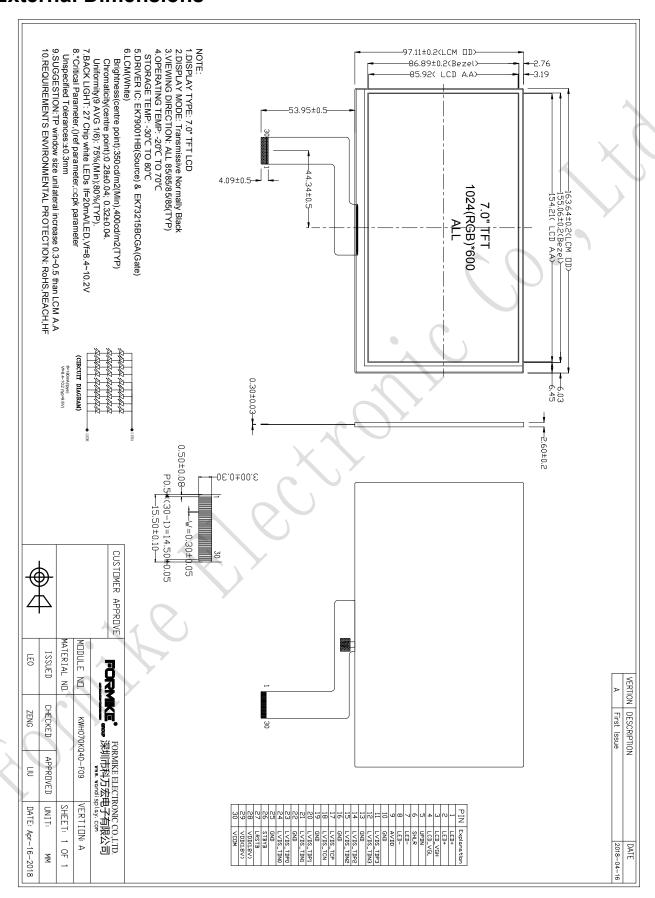

| Module size      | 163.64(W) ×97.11 (H)×2.60(T)    | mm    |

| Active area      | 154.21(W) ×85.92(H)             | mm    |

| Dot pitch        | 0.1506 (W) ×0.1432 (H)          | mm    |

| Back Light       | 27 White LED In serial/parallel |       |

| With/Without TSP | Without TSP                     |       |

| Weight(g)        | -                               |       |

www.wandisplay.com 4/18 Ver.1.0

## 3. External Dimensions

# 4. Interface Description

# For LCM

| Pin No. Symbol Power for LED backlight (Anode)  2 LED+ Power for LED backlight (Anode)  3 LCD_VGH Gate ON Voltage  4 LCD_VGL Gate OFF Voltage  5 UPDN Up/down selection  6 SHLR Left / right selection  7 LED- Power for LED backlight (Cathode)  8 LED- Power for LED backlight (Cathode)  9 AVDD Power for LED backlight (Cathode)  10 GND Power for Analog Circuit  11 LVDS_TDP3 LVDS DSI differential data pair. (Data lane 3)  12 LVDS_TDN3 LVDS DSI differential data pair. (Data lane 3)  13 GND Power ground.  14 LVDS_TDP2 LVDS DSI differential data pair. (Data lane 2)  15 LVDS_TDN2 LVDS DSI differential data pair. (Data lane 2)  16 GND Power ground.  17 LVDS_TDP2 LVDS DSI differential data pair. (Data lane 2)  18 LVDS_TDN2 LVDS DSI differential clock pair  19 GND Power ground.  20 LVDS_TDCP LVDS DSI differential clock pair  21 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1)  22 GND Power ground.  23 LVDS_TDN1 LVDS DSI differential data pair. (Data lane 1)  24 LVDS_TDP0 LVDS DSI differential data pair. (Data lane 1)  25 GND Power ground.  26 STBYB Display on/off.  27 LRSTB Global reset pin.  28 VDD(1.8V) Power for Digital Circuit(1.8V)  30 VCOM Common Voltage | Din No | Cymbol    | Functional                                     | Domork |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------|------------------------------------------------|--------|

| 2 LED+ Power for LED backlight (Anode) 3 LCD_VGH Gate ON Voltage 4 LCD_VGL Gate OFF Voltage 5 UPDN Up/down selection 6 SHLR Left / right selection 7 LED- Power for LED backlight (Cathode) 8 LED- Power for LED backlight (Cathode) 9 AVDD Power for LED backlight (Cathode) 10 GND Power ground. 11 LVDS_TDP3 LVDS DSI differential data pair. (Data lane 3) 12 LVDS_TDN3 LVDS DSI differential data pair. (Data lane 3) 13 GND Power ground. 14 LVDS_TDP2 LVDS DSI differential data pair. (Data lane 2) 15 LVDS_TDN2 LVDS DSI differential data pair. (Data lane 2) 16 GND Power ground. 17 LVDS_TDCP LVDS DSI differential clock pair 18 LVDS_TDCP LVDS DSI differential clock pair 19 GND Power ground. 20 LVDS_TDCN LVDS DSI differential clock pair 19 GND Power ground. 20 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1) 21 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1) 22 GND Power ground. 23 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 0) 24 LVDS_TDP0 LVDS DSI differential data pair. (Data lane 0) 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V)                                           |        |           |                                                | Remark |

| 3 LCD_VGH Gate ON Voltage 4 LCD_VGL Gate OFF Voltage 5 UPDN Up/down selection 6 SHLR Left / right selection 7 LED- Power for LED backlight (Cathode) 8 LED- Power for LED backlight (Cathode) 9 AVDD Power for Analog Circuit 10 GND Power ground. 11 LVDS_TDP3 LVDS DSI differential data pair. (Data lane 3) 12 LVDS_TDN3 LVDS DSI differential data pair. (Data lane 3) 13 GND Power ground. 14 LVDS_TDP2 LVDS DSI differential data pair. (Data lane 2) 15 LVDS_TDN2 LVDS DSI differential data pair. (Data lane 2) 16 GND Power ground. 17 LVDS_TDCP LVDS DSI differential data pair. (Data lane 2) 18 LVDS_TDN2 LVDS DSI differential clock pair 19 GND Power ground. 20 LVDS_TDCN LVDS DSI differential clock pair 21 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1) 22 GND Power ground. 23 LVDS_TDN1 LVDS DSI differential data pair. (Data lane 1) 24 LVDS_TDP0 LVDS DSI differential data pair. (Data lane 0) 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                              |        |           | <b>0</b> \                                     |        |

| 4 LCD_VGL Gate OFF Voltage 5 UPDN Up/down selection 6 SHLR Left / right selection 7 LED- Power for LED backlight (Cathode) 8 LED- Power for LED backlight (Cathode) 9 AVDD Power for Analog Circuit 10 GND Power ground. 11 LVDS_TDP3 LVDS DSI differential data pair. (Data lane 3) 12 LVDS_TDN3 LVDS DSI differential data pair. (Data lane 3) 13 GND Power ground. 14 LVDS_TDP2 LVDS DSI differential data pair. (Data lane 2) 15 LVDS_TDN2 LVDS DSI differential data pair. (Data lane 2) 16 GND Power ground. 17 LVDS_TDP2 LVDS DSI differential data pair. (Data lane 2) 18 LVDS_TDN2 LVDS DSI differential clock pair 19 GND Power ground. 20 LVDS_TDCN LVDS DSI differential clock pair 19 GND Power ground. 20 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1) 21 LVDS_TDN1 LVDS DSI differential data pair. (Data lane 1) 22 GND Power ground. 23 LVDS_TDP0 LVDS DSI differential data pair. (Data lane 0) 24 LVDS_TDN0 LVDS DSI differential data pair. (Data lane 0) 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                       |        |           | <b>U</b> , ,                                   |        |

| 5 UPDN Up/down selection 6 SHLR Left / right selection 7 LED- Power for LED backlight (Cathode) 8 LED- Power for LED backlight (Cathode) 9 AVDD Power for Analog Circuit 10 GND Power ground. 11 LVDS_TDP3 LVDS DSI differential data pair. (Data lane 3) 12 LVDS_TDN3 LVDS DSI differential data pair. (Data lane 3) 13 GND Power ground. 14 LVDS_TDP2 LVDS DSI differential data pair. (Data lane 2) 15 LVDS_TDN2 LVDS DSI differential data pair. (Data lane 2) 16 GND Power ground. 17 LVDS_TDP2 LVDS DSI differential data pair. (Data lane 2) 18 LVDS_TDCP LVDS DSI differential clock pair 19 GND Power ground. 20 LVDS_TDCN LVDS DSI differential clock pair 19 GND Power ground. 20 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1) 21 LVDS_TDN1 LVDS DSI differential data pair. (Data lane 1) 22 GND Power ground. 23 LVDS_TDP0 LVDS DSI differential data pair. (Data lane 0) 24 LVDS_TDN0 LVDS DSI differential data pair. (Data lane 0) 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                  |        | _         | •                                              |        |

| 6 SHLR Left / right selection 7 LED- Power for LED backlight (Cathode) 8 LED- Power for LED backlight (Cathode) 9 AVDD Power for Analog Circuit 10 GND Power ground. 11 LVDS_TDP3 LVDS DSI differential data pair. (Data lane 3) 12 LVDS_TDN3 LVDS DSI differential data pair. (Data lane 3) 13 GND Power ground. 14 LVDS_TDP2 LVDS DSI differential data pair. (Data lane 2) 15 LVDS_TDN2 LVDS DSI differential data pair. (Data lane 2) 16 GND Power ground. 17 LVDS_TDCP LVDS DSI differential clock pair 18 LVDS_TDCP LVDS DSI differential clock pair 19 GND Power ground. 20 LVDS_TDCN LVDS DSI differential data pair. (Data lane 1) 21 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1) 22 GND Power ground. 23 LVDS_TDN1 LVDS DSI differential data pair. (Data lane 1) 24 LVDS_TDP0 LVDS DSI differential data pair. (Data lane 0) 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                            |        | _         |                                                |        |

| 7 LED- Power for LED backlight (Cathode) 8 LED- Power for LED backlight (Cathode) 9 AVDD Power for Analog Circuit 10 GND Power ground. 11 LVDS_TDP3 LVDS DSI differential data pair. (Data lane 3) 12 LVDS_TDN3 LVDS DSI differential data pair. (Data lane 3) 13 GND Power ground. 14 LVDS_TDP2 LVDS DSI differential data pair. (Data lane 2) 15 LVDS_TDN2 LVDS DSI differential data pair. (Data lane 2) 16 GND Power ground. 17 LVDS_TDCP LVDS DSI differential clock pair 18 LVDS_TDCN LVDS DSI differential clock pair 19 GND Power ground. 20 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1) 21 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1) 22 GND Power ground. 23 LVDS_TDN1 LVDS DSI differential data pair. (Data lane 1) 24 LVDS_TDP0 LVDS DSI differential data pair. (Data lane 0) 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                          |        |           | •                                              |        |

| 8 LED- Power for LED backlight (Cathode) 9 AVDD Power for Analog Circuit 10 GND Power ground. 11 LVDS_TDP3 LVDS DSI differential data pair. (Data lane 3) 12 LVDS_TDN3 LVDS DSI differential data pair. (Data lane 3) 13 GND Power ground. 14 LVDS_TDP2 LVDS DSI differential data pair. (Data lane 2) 15 LVDS_TDN2 LVDS DSI differential data pair. (Data lane 2) 16 GND Power ground. 17 LVDS_TDCP LVDS DSI differential clock pair 18 LVDS_TDCP LVDS DSI differential clock pair 19 GND Power ground. 20 LVDS_TDCN LVDS DSI differential data pair. (Data lane 1) 21 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1) 22 GND Power ground. 23 LVDS_TDN1 LVDS DSI differential data pair. (Data lane 1) 24 LVDS_TDP0 LVDS DSI differential data pair. (Data lane 0) 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                   |        |           |                                                |        |

| 9 AVDD Power for Analog Circuit 10 GND Power ground. 11 LVDS_TDP3 LVDS DSI differential data pair. (Data lane 3) 12 LVDS_TDN3 LVDS DSI differential data pair. (Data lane 3) 13 GND Power ground. 14 LVDS_TDP2 LVDS DSI differential data pair. (Data lane 2) 15 LVDS_TDN2 LVDS DSI differential data pair. (Data lane 2) 16 GND Power ground. 17 LVDS_TDCP LVDS DSI differential clock pair 18 LVDS_TDCP LVDS DSI differential clock pair 19 GND Power ground. 20 LVDS_TDCN LVDS DSI differential data pair. (Data lane 1) 21 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1) 22 GND Power ground. 23 LVDS_TDN1 LVDS DSI differential data pair. (Data lane 0) 24 LVDS_TDN0 LVDS DSI differential data pair. (Data lane 0) 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                            |        |           | ,                                              |        |

| 10 GND Power ground.  11 LVDS_TDP3 LVDS DSI differential data pair. (Data lane 3)  12 LVDS_TDN3 LVDS DSI differential data pair. (Data lane 3)  13 GND Power ground.  14 LVDS_TDP2 LVDS DSI differential data pair. (Data lane 2)  15 LVDS_TDN2 LVDS DSI differential data pair. (Data lane 2)  16 GND Power ground.  17 LVDS_TDCP LVDS DSI differential clock pair  18 LVDS_TDCP LVDS DSI differential clock pair  19 GND Power ground.  20 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1)  21 LVDS_TDN1 LVDS DSI differential data pair. (Data lane 1)  22 GND Power ground.  23 LVDS_TDP0 LVDS DSI differential data pair. (Data lane 0)  24 LVDS_TDN0 LVDS DSI differential data pair. (Data lane 0)  25 GND Power ground.  26 STBYB Display on/off.  27 LRSTB Global reset pin.  28 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                                          |        |           | <u> </u>                                       |        |

| 11 LVDS_TDP3 LVDS DSI differential data pair. (Data lane 3) 12 LVDS_TDN3 LVDS DSI differential data pair. (Data lane 3) 13 GND Power ground. 14 LVDS_TDP2 LVDS DSI differential data pair. (Data lane 2) 15 LVDS_TDN2 LVDS DSI differential data pair. (Data lane 2) 16 GND Power ground. 17 LVDS_TDCP LVDS DSI differential clock pair 18 LVDS_TDCN LVDS DSI differential clock pair 19 GND Power ground. 20 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1) 21 LVDS_TDN1 LVDS DSI differential data pair. (Data lane 1) 22 GND Power ground. 23 LVDS_TDP0 LVDS DSI differential data pair. (Data lane 0) 24 LVDS_TDN0 LVDS DSI differential data pair. (Data lane 0) 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                                                                                 |        |           | •                                              |        |

| 12 LVDS_TDN3 LVDS DSI differential data pair. (Data lane 3) 13 GND Power ground. 14 LVDS_TDP2 LVDS DSI differential data pair. (Data lane 2) 15 LVDS_TDN2 LVDS DSI differential data pair. (Data lane 2) 16 GND Power ground. 17 LVDS_TDCP LVDS DSI differential clock pair 18 LVDS_TDCN LVDS DSI differential clock pair 19 GND Power ground. 20 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1) 21 LVDS_TDN1 LVDS DSI differential data pair. (Data lane 1) 22 GND Power ground. 23 LVDS_TDP0 LVDS DSI differential data pair. (Data lane 0) 24 LVDS_TDN0 LVDS DSI differential data pair. (Data lane 0) 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10     |           | Power ground.                                  |        |

| 13 GND Power ground.  14 LVDS_TDP2 LVDS DSI differential data pair. (Data lane 2)  15 LVDS_TDN2 LVDS DSI differential data pair. (Data lane 2)  16 GND Power ground.  17 LVDS_TDCP LVDS DSI differential clock pair  18 LVDS_TDCN LVDS DSI differential clock pair  19 GND Power ground.  20 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1)  21 LVDS_TDN1 LVDS DSI differential data pair. (Data lane 1)  22 GND Power ground.  23 LVDS_TDN0 LVDS DSI differential data pair. (Data lane 0)  24 LVDS_TDN0 LVDS DSI differential data pair. (Data lane 0)  25 GND Power ground.  26 STBYB Display on/off.  27 LRSTB Global reset pin.  28 VDD(1.8V) Power for Digital Circuit(1.8V)  29 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11     | LVDS_TDP3 | LVDS DSI differential data pair. (Data lane 3) |        |

| 14 LVDS_TDP2 LVDS DSI differential data pair. (Data lane 2) 15 LVDS_TDN2 LVDS DSI differential data pair. (Data lane 2) 16 GND Power ground. 17 LVDS_TDCP LVDS DSI differential clock pair 18 LVDS_TDCN LVDS DSI differential clock pair 19 GND Power ground. 20 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1) 21 LVDS_TDN1 LVDS DSI differential data pair. (Data lane 1) 22 GND Power ground. 23 LVDS_TDP0 LVDS DSI differential data pair. (Data lane 0) 24 LVDS_TDN0 LVDS DSI differential data pair. (Data lane 0) 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V) 29 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12     | LVDS_TDN3 | LVDS DSI differential data pair. (Data lane 3) |        |

| 15 LVDS_TDN2 LVDS DSI differential data pair. (Data lane 2) 16 GND Power ground. 17 LVDS_TDCP LVDS DSI differential clock pair 18 LVDS_TDCN LVDS DSI differential clock pair 19 GND Power ground. 20 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1) 21 LVDS_TDN1 LVDS DSI differential data pair. (Data lane 1) 22 GND Power ground. 23 LVDS_TDP0 LVDS DSI differential data pair. (Data lane 0) 24 LVDS_TDN0 LVDS DSI differential data pair. (Data lane 0) 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13     | GND       | Power ground.                                  |        |

| 16 GND Power ground. 17 LVDS_TDCP LVDS DSI differential clock pair 18 LVDS_TDCN LVDS DSI differential clock pair 19 GND Power ground. 20 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1) 21 LVDS_TDN1 LVDS DSI differential data pair. (Data lane 1) 22 GND Power ground. 23 LVDS_TDP0 LVDS DSI differential data pair. (Data lane 0) 24 LVDS_TDN0 LVDS DSI differential data pair. (Data lane 0) 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 14     | LVDS_TDP2 | LVDS DSI differential data pair. (Data lane 2) |        |

| 17 LVDS_TDCP LVDS DSI differential clock pair 18 LVDS_TDCN LVDS DSI differential clock pair 19 GND Power ground. 20 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1) 21 LVDS_TDN1 LVDS DSI differential data pair. (Data lane 1) 22 GND Power ground. 23 LVDS_TDP0 LVDS DSI differential data pair. (Data lane 0) 24 LVDS_TDN0 LVDS DSI differential data pair. (Data lane 0) 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V) 29 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15     | LVDS_TDN2 | LVDS DSI differential data pair. (Data lane 2) |        |

| 18 LVDS_TDCN LVDS DSI differential clock pair 19 GND Power ground. 20 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1) 21 LVDS_TDN1 LVDS DSI differential data pair. (Data lane 1) 22 GND Power ground. 23 LVDS_TDP0 LVDS DSI differential data pair. (Data lane 0) 24 LVDS_TDN0 LVDS DSI differential data pair. (Data lane 0) 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V) 29 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 16     | GND       | Power ground.                                  |        |

| 18 LVDS_TDCN LVDS DSI differential clock pair 19 GND Power ground. 20 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1) 21 LVDS_TDN1 LVDS DSI differential data pair. (Data lane 1) 22 GND Power ground. 23 LVDS_TDP0 LVDS DSI differential data pair. (Data lane 0) 24 LVDS_TDN0 LVDS DSI differential data pair. (Data lane 0) 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V) 29 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17     | LVDS_TDCP | LVDS DSI differential clock pair               |        |

| 20 LVDS_TDP1 LVDS DSI differential data pair. (Data lane 1) 21 LVDS_TDN1 LVDS DSI differential data pair. (Data lane 1) 22 GND Power ground. 23 LVDS_TDP0 LVDS DSI differential data pair. (Data lane 0) 24 LVDS_TDN0 LVDS DSI differential data pair. (Data lane 0) 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V) 29 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18     | LVDS_TDCN |                                                |        |

| LVDS_TDN1 LVDS DSI differential data pair. (Data lane 1)  22 GND Power ground.  23 LVDS_TDP0 LVDS DSI differential data pair. (Data lane 0)  24 LVDS_TDN0 LVDS DSI differential data pair. (Data lane 0)  25 GND Power ground.  26 STBYB Display on/off.  27 LRSTB Global reset pin.  28 VDD(1.8V) Power for Digital Circuit(1.8V)  29 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19     | GND       | Power ground.                                  |        |

| 22 GND Power ground. 23 LVDS_TDP0 LVDS DSI differential data pair. (Data lane 0) 24 LVDS_TDN0 LVDS DSI differential data pair. (Data lane 0) 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V) 29 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20     | LVDS_TDP1 | LVDS DSI differential data pair. (Data lane 1) |        |

| 23 LVDS_TDP0 LVDS DSI differential data pair. (Data lane 0) 24 LVDS_TDN0 LVDS DSI differential data pair. (Data lane 0) 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V) 29 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21     | LVDS_TDN1 | LVDS DSI differential data pair. (Data lane 1) |        |

| 24 LVDS_TDN0 LVDS DSI differential data pair. (Data lane 0) 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V) 29 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22     | GND       | Power ground.                                  |        |

| 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V) 29 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23     | LVDS_TDP0 | LVDS DSI differential data pair. (Data lane 0) |        |

| 25 GND Power ground. 26 STBYB Display on/off. 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V) 29 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24     | LVDS_TDN0 | LVDS DSI differential data pair. (Data lane 0) |        |

| 26 STBYB Display on/off.  27 LRSTB Global reset pin.  28 VDD(1.8V) Power for Digital Circuit(1.8V)  29 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25     | GND       |                                                |        |

| 27 LRSTB Global reset pin. 28 VDD(1.8V) Power for Digital Circuit(1.8V) 29 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26     | STBYB     | <u> </u>                                       |        |

| 28 VDD(1.8V) Power for Digital Circuit(1.8V) 29 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27     | LRSTB     |                                                |        |

| 29 VDD(1.8V) Power for Digital Circuit(1.8V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 28     | VDD(1.8V) | '                                              |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29     |           | ` '                                            |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30     |           | , ,                                            |        |

# 5. Absolute Maximum Ratings

| Parameter                | Symbol    | Min  | Max | Unit |

|--------------------------|-----------|------|-----|------|

| Supply voltage for logic | VDD       | -0.3 | 5.0 | V    |

| Operating temperature    | TOP       | -20  | +70 | °C \ |

| Storage temperature      | TST       | -30  | +80 | °C   |

| Power supply voltage (1) | VGH       | -0.3 | 42  | V    |

| Power supply voltage (2) | VGL       | -20  | 0.3 | V    |

| Power supply voltage (3) | VGH - VGL | -0.3 | 40  | V    |

| Power supply voltage (4) | AVDD      | 0.5  | 15  | V    |

Note 1: All of the voltages listed above are with respective to GND = 0V.

Note 2: Device is subject to be damaged permanently if stresses beyond those absolute maximum ratings listed above.

## 6. Electrical Characteristics

$(VCC = 3.3V, GND = 0V, Ta = 25^{\circ}C)$

| 00 - 0.0V, GIVD - 0V, Id - 20 C) |        |         |      |        |      |                     |  |  |

|----------------------------------|--------|---------|------|--------|------|---------------------|--|--|

| Item                             | Symbol | Min     | Тур  | Max    | Unit | Applicable terminal |  |  |

| Supply voltage for logic         | VDD    | 1.8     | 3.3  | 3.6    | V    | VDD                 |  |  |

| Input voltage                    | VIL    | 0       | -    | 0.3VDD | ٧    |                     |  |  |

| Input voltage                    | ViH    | 0.7 VDD | -    | VDD    | V    |                     |  |  |

| Input voltage                    | Vgн    | 17      | 18   | 19     | V    |                     |  |  |

| Input voltage                    | VgL    | -6.6    | -6.0 | -5.4   | V    |                     |  |  |

| Input voltage                    | Vavdd  | 9.4     | 9.6  | 9.8    | V    |                     |  |  |

| Input voltage                    | Vсом   | 2.85    | 3.15 | 3.45   | V    |                     |  |  |

# 7. Timing Characteristics.

DE mode

|                                 | 0 1 1    |      | 1 1 1 1 1 1 |      |      |

|---------------------------------|----------|------|-------------|------|------|

| Parameter                       | Symbol   | Min. | Тур.        | Max. | Unit |

| DCLK frequency @Frame rate=60hz | fclk     | 40.8 | 51.2        | 67.2 | Mhz  |

| Horizontal display area         | thd      |      | 1024        | 10 8 | DCLK |

| HSYNC period time               | th       | 1114 | 1344        | 1400 | DCLK |

| HSYNC blanking                  | thb+thfp | 90   | 320         | 376  | DCLK |

| Vertical display area           | Tvd      |      | 600         |      | Н    |

| VSYNC period time               | Tv       | 610  | 635         | 800  | Н    |

| VSYNC blanking                  | Tvb+Tvfp | 10   | 35          | 200  | Н    |

HV mode

Horizontal input timing

| Parameter                       |      | Symbol |      | Value |      | Unit |

|---------------------------------|------|--------|------|-------|------|------|

| Horizontal display area         |      | thd    | 1024 |       | DCLK |      |

| DCLK frequency@ Frame rate=60hz |      | falls  | Min. | Тур.  | Max. |      |

|                                 |      | fclk - | 44.9 | 51.2  | 63   | Mhz  |

| 1 Horizontal Line               |      | th     | 1200 | 1344  | 1400 |      |

|                                 | Min. |        | 1    |       |      | ]    |

| HSYNC pulse width               | Тур. | thpw   |      |       |      | DCLK |

| Ma                              |      |        |      | 140   | 200  | DCL  |

| HSYNC blanking                  |      | thb    | 160  | 160   | 160  |      |

| HSYNC front por                 | ch   | thfp   | 16   | 160   | 216  |      |

HV mode

Vertical input timing

|                       |        |      | (1.15. A) |      |      |  |

|-----------------------|--------|------|-----------|------|------|--|

| Parameter             | Symbol | Min. | Тур.      | Max. | Unit |  |

| Vertical display area | tvd    | _    | 600       |      | Н    |  |

| VSYNC period time     | tv     | 624  | 635       | 750  | Н    |  |

| VSYNC pulse width     | tvpw   | 1    | -         | 20   | Н    |  |

| VSYNC back porch      | tvb    | 23   | 23        | 23   | Н    |  |

| VSYNC front porch     | tvfp   | 1    | 12        | 127  | Н    |  |

# 8. Backlight Characteristics.

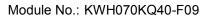

(CIRCUIT DIAGRAM)

| Item                       | Symbo | MIN   | TYP  | MAX        | UNIT              | Test<br>Condition | Note |

|----------------------------|-------|-------|------|------------|-------------------|-------------------|------|

| Supply Voltage             | Vf    | 8.4   | 9.9  | 10,2       | V                 | If=180 mA         | •    |

| Supply Current             | If    | -     | 180  |            | mA                | -                 | -    |

| Reverse Voltage            | Vr    | -     | -    | 5          | V                 | 10uA              |      |

| Power dissipation          | Pd    | -     | 1782 | 7          | mW                | -                 |      |

| Luminous Intensity for LCM |       | 350   | 400  | <b>)</b> . | cd/m <sup>2</sup> | If=180 mA         |      |

| Uniformity for LCM         | -     | 80    |      | -          | %                 | If=180 mA         |      |

| Life Time                  | -     | 50000 | 1,7  | -          | Hr                | If=180 mA         | -    |

| Backlight Color            | х     | 0.24  | 0.28 | 0.32       | -                 | If=180 mA         | -    |

|                            | у     | 0.28  | 0.32 | 0.36       | -                 | If=180 mA         | -    |

www.wandisplay.com 9/18 Ver.1.0

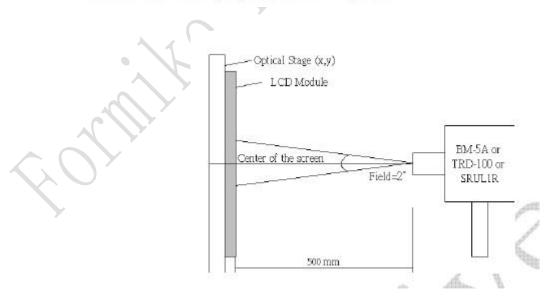

# 9. Optical Characteristics

| ITEM                                       |        | SYMBOL   | CONDITION          | MIN.  | TYP.    | MAX.  | UNIT  | NOTE                                                    |

|--------------------------------------------|--------|----------|--------------------|-------|---------|-------|-------|---------------------------------------------------------|

| Contrast Ratio                             |        | CR       | θ=ψ= 0°            | 600   | 800     |       | _     | *1) 2)                                                  |

| Transmittance<br>(with HC/Plain Polarizer) |        | Т% €     | θ=ψ= 0°            | 3.8   | 3.8 4.1 | 4.1   | %     | *1) 6)<br>Measuring with<br>Polarizer<br>Reference Only |

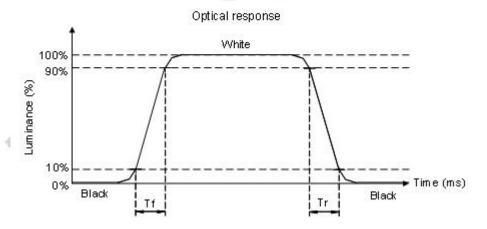

| Response Time                              | 8      | Tr+Tf    | θ=ψ= 0°            | 1     | 30      | 40    | ms    | *3)                                                     |

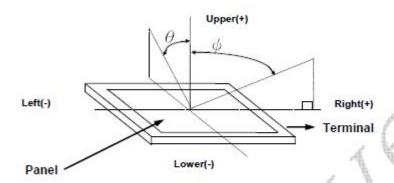

|                                            | Left   | ø        | CR≧10              | 80    | 85      | 1     | Ting! |                                                         |

|                                            | Right  | •        |                    | 80    | 85      | h     | 0     | *4)<br>Measuring with                                   |

| View angle                                 | Upper  | θ        |                    | 80    | 85      |       |       | Polarizer -                                             |

|                                            | Lower  | θ        |                    | 80    | 85      | .7    | 0     | Reference Onl                                           |

|                                            | 181    | Х        | θ=ψ= 0°            | 0.280 | 0.300   | 0.320 | 320   |                                                         |

|                                            | W      | Y        |                    | 0.320 | 0.340   | 0.360 |       |                                                         |

|                                            | R      | X        |                    | 0.612 | 0.632   | 0.652 |       |                                                         |

|                                            | I.     | Y        | 0-0-0              | 0.296 | 0.316   | 0.336 | 8782  | *5)                                                     |

| Color Filter                               | G      | X        | Base on            | 0.277 | 0.297   | 0.317 |       | CF glass<br>Base on C light                             |

| Chromaticity                               | G      | Y        | C light            | 0.516 | 0.536   | 0.556 | -     |                                                         |

|                                            |        | X        |                    | 0.120 | 0.140   | 0.160 | 170   |                                                         |

|                                            | В      | my '     | <b>L</b> '         | 0.134 | 0.154   | 0.174 |       |                                                         |

| -                                          | NTSC(C | IE 1931) | Base on<br>C light | 47    | 50      |       | %     |                                                         |

#### [Note]

#### \*1) Setup of Measurement Equipment :

The LCD module should be turn-on to a stable luminance level to be reached. The measurement should be executed after lighting Backlight for 20 minutes and in a dark room.

#### \*2) Definition of contrast ratio :

CR = White Luminance (ON) / Black Luminance (OFF)

#### \*3) Definition of response time :

The response time is defined as the time interval between the 10% and 90% amplitudes.

The output signals of photo detector are measured when the input signals are changed from "black" to "white" (rising time) and from "white" to "black" (falling time) respectively.

\*4) Definition of view angle(θ · •):

- \*5) Light source: Base on C light.

- \*6) Definition of transmittance (T%):

Transmittance=(Luminance of LCD module/Luminance of backlight)\* 100%

www.wandisplay.com 11/18 Ver.1.0

# **10. RELIABILITY**

| No. | Test Item                                        | Test Condition                                                                                                               | Remark                                                                                               |

|-----|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| 1   | High Temperature Storage                         | +80℃± 2℃,96 hrs                                                                                                              | Note                                                                                                 |

| 2   | Low Temperature Storage                          | -30℃± 2℃, 96 hrs                                                                                                             | Note                                                                                                 |

| 3   | High Temperature Operation                       | +70℃± 2℃,96 hrs                                                                                                              | Note                                                                                                 |

| 4   | Low Temperature Operation                        | +20℃± 2℃,96 hrs                                                                                                              | Note                                                                                                 |

| 5   | High Temperature & High<br>Humidity Storage Test | +50℃± 5℃, 90%R.H, 96 hours                                                                                                   | Note                                                                                                 |

| 6   | Temperature Cycle ( non operation)               | -30°C ← +25°C → +80°C<br>(30mins ← 5mins →30mins)<br>10 Cycles                                                               | Note                                                                                                 |

| 7   | Electronic Static Discharge                      | Air Discharge: 2KV to with 5 times  Ambiance: 15°c~35°c,30%~60%R.H Resistance(Rd): 330Ω ±10% Capacitance(Cs + Cd): 150pF±10% | Discharge for each polarity Mode of Operation: Single Discharge, successive discharge at least 1 sec |

| 8   | Vibration (Packaged)                             | Frequency range: 10Hz ~ 55 Hz<br>Amplitude: 1.5mm<br>Direction of X.Y. Z for 3 Hrs in total                                  |                                                                                                      |

| 9   | Drop Test ( Packaged)                            | Height: 80cm, Time: 1<br>1 corner, 3 edged, 6 surfaces                                                                       |                                                                                                      |

Note : Recovery Time should be 2~4 hours at room temperature (20±8 $^\circ$ c) and humidity ( below 60% R.H). No abnormalities in functions and appearance

www.wandisplay.com 12/18 Ver.1.0

## 11.INSPECTION CRITERION

### **11.1 Scope**

Display Quality Evaluation Mechanics Specification

## 11.2 Sampling Plan

MIL-STD-105E

Unless there is other agreement, the sampling plan for incoming inspection shall follow MIL-STD-105E Lot size: Quantity per shipment as one lot (different model as different lot ).

Sampling type: Normal inspection, single sampling

Sampling level: Level II.

11.3 Acceptable Quality Level

| Item       | Major | Minor |

|------------|-------|-------|

| Appearance | 1.0%  | 1.5%  |

| Electrical | 0.65  | 1.0%  |

#### 11.3.1 Classification of defects:

### 11.3.1.1Major defect

Any defect may result in functional failure, or reduce the usability of product for its purpose. For Example: Electrical failure, deformation and etc.

11.3.1.2 Minor defect

The criteria on major or minor judgment will be according with the classification of defects.

### **11.4 Panel Inspection Condition**

11.4.1 Environment:

11.4.2 Room Temperature:  $25\pm5^{\circ}$  C.

11.4.3 Humidity:  $50\pm20\%$  RH.

Illumination: 300 ~ 700 Lux.

11.4.4 Inspection Distance: 35 ± 5 cm

#### 11.5 TFT Inspection Criteria

11.5.1 Visual inspection criterion in cosmetic / appearance

|     | 11.5.1 Visual inspection chiefion in cosmetic / appearance |                        |        |  |  |  |  |

|-----|------------------------------------------------------------|------------------------|--------|--|--|--|--|

| Gla | Glass defect                                               |                        |        |  |  |  |  |

| N   | Item                                                       | Criteria               | Remark |  |  |  |  |

| 0   |                                                            |                        |        |  |  |  |  |

| 1   | Dimension<br>(Minor)                                       | By engineering diagram | Y Z (  |  |  |  |  |

| 2   | Crack (Major)                                              | Extensive crack        |        |  |  |  |  |

| 3 | Corner (Minor) | $X \le 4 \text{ mm}$ $Y \le 4 \text{ mm}$ $Z \le T$ Ignore | T: Glass thickness Z: Thickness X: Length Y: Width |

|---|----------------|------------------------------------------------------------|----------------------------------------------------|

| 4 | Side (Minor)   | $X \le 6mm$ $Y \le 4mm$ $Z \le T$ Ignore                   | T: Glass thickness Z: Thickness X: Length Y: Width |

| TFT | TFT defect in appearance                                                         |                                                                                                                                                                                                                         |                                                       |  |  |  |  |

|-----|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| No  | Item                                                                             | Criteria                                                                                                                                                                                                                | Remark                                                |  |  |  |  |

| 1   | Foreign Spot (Minor) Including: Black spot, White spot Pin hole Foreign particle | D≤0.3mm, Ignore<br>0.3mm <d≤0.5mm, n≤5<br="">0.5mm<d, n="0&lt;br">Distance≥5mm<br/>Ignore if out of Area AA</d,></d≤0.5mm,>                                                                                             | D =(X+Y)/2,<br>X: Length, Y: Width  □ = (X+Y)/2  X  → |  |  |  |  |

| 2   | Foreign Line(Minor) Including: Black line White line Bright line                 | $W \leqslant 0.08$ mm, Ignore $0.08$ mm< $W \leqslant 0.1$ mm, $L \leqslant 6$ mm, $N \leqslant 5$ $0.1$ mm< $W \leqslant 0.15$ mm, $L \leqslant 5$ mm, $N \leqslant 2$ $W > 0.15$ mm, $N = 0$ Ignore if out of Area AA | L: Length, W: Width                                   |  |  |  |  |

| 3   | Polarizer Dent/Air<br>Bubble<br>(Minor)                                          | D≤0.3mm, Ignore<br>0.3mm <d≤0.5mm, n≤5<br="">D&gt;0.50mm, N=0<br/>Distance≥5mm<br/>Ignore if out of Area AA</d≤0.5mm,>                                                                                                  | D =(X+Y)/2,<br>X: Length, Y: Width  □ = (X+Y)/2  X  → |  |  |  |  |

| 4   | Polarizer Scratches<br>(Minor)                                                   | $W \leqslant 0.08$ mm, Ignore $0.08$ mm< $W \leqslant 0.1$ mm, L $\leqslant 6$ mm, N $\leqslant 5$ $0.1$ mm< $W \leqslant 0.15$ mm, L $\leqslant 5$ mm, N $\leqslant 2$ $W > 0.15$ mm, N=0 Ignore if out of Area AA     | L: Length, W: Width                                   |  |  |  |  |

www.wandisplay.com 14/18 Ver.1.0

| Oth | Other defects     |                                         |          |  |  |  |  |  |

|-----|-------------------|-----------------------------------------|----------|--|--|--|--|--|

| No  | Item              | Criteria                                | Remark   |  |  |  |  |  |

| 1   | FPC (Minor)       | Any crack or breakage which effect the  |          |  |  |  |  |  |

|     |                   | function are not allowed                |          |  |  |  |  |  |

|     |                   | Disregard if the dirty removed          |          |  |  |  |  |  |

| 2   | Backlight (Minor) | Power up is allowed.                    |          |  |  |  |  |  |

|     |                   | Breaking off is not allowed.            | <b>A</b> |  |  |  |  |  |

|     |                   | The scratch which may causes a          |          |  |  |  |  |  |

|     |                   | problem in practical use is not allowed |          |  |  |  |  |  |

| 3   | Bezel (Minor)     | Erasable dirt is ignore                 |          |  |  |  |  |  |

11.5.2 Visual inspection criterion in electrical display

| <u> </u> | suai inspection critei                            | non in electrical display |          |

|----------|---------------------------------------------------|---------------------------|----------|

| Glas     | ss defect                                         |                           | <b>Y</b> |

| No       | Item                                              | Criteria                  | Remark   |

| 1        | No display (Major)<br>Abnormally<br>Short circuit | Not allowed               |          |

| 2        | Missing line (Major)                              | Not allowed               |          |

| 3        | Darker or lighter line<br>(Major)                 | Not allowed               |          |

| 4        | Weak line (Minor)                                 | By limit sample           |          |

www.wandisplay.com 15/18 Ver.1.0

| Display Inspection |                   |                                                                                                 |           |           |           |  |                                                                                                                                                    |

|--------------------|-------------------|-------------------------------------------------------------------------------------------------|-----------|-----------|-----------|--|----------------------------------------------------------------------------------------------------------------------------------------------------|

| No                 | Item              | Criteria                                                                                        |           |           |           |  | Remark                                                                                                                                             |

| 1                  | Bright / Dark dot | Items                                                                                           | Area<br>I | Area<br>O | Tota<br>I |  | H/4 H/2 H/2 O V/4                                                                                                                                  |

|                    |                   | Bright                                                                                          | 2         | 2         | 3         |  | V I V/2                                                                                                                                            |

|                    |                   | Dark                                                                                            | 3         | 4         | 5         |  | ↓                                                                                                                                                  |

|                    |                   | Bright &<br>Dark                                                                                | 4         | 5         | 7         |  | H                                                                                                                                                  |

|                    |                   | 2<br>adjacent                                                                                   | 1         | 2         | 3         |  | 1.1sub-pixel: 1R or 1G or 1B                                                                                                                       |

|                    |                   | dots                                                                                            |           |           |           |  | 2.Point defect area ≥                                                                                                                              |

|                    |                   | Minimum                                                                                         | Distanc   | e ≥ :     | 5mm       |  | 1/2 sub pixel                                                                                                                                      |

| 2                  | Tiny bright dot   | Visible thro                                                                                    | ugh 6%    | ND filt   | er        |  | D = (X+Y)/2,                                                                                                                                       |

|                    |                   | D≤0.3mm                                                                                         | , Ignore  | Э         |           |  | X: Length, Y: Width                                                                                                                                |

|                    |                   | 0.3mm <d≤< td=""><td>≤0.5mm</td><td>ı, N≤</td><td>5</td><td></td><td>D = ( X+Y ) / 2</td></d≤<> | ≤0.5mm    | ı, N≤     | 5         |  | D = ( X+Y ) / 2                                                                                                                                    |

|                    |                   | D>0.5mm,                                                                                        | N=0       |           |           |  | X                                                                                                                                                  |

|                    |                   | Distance≥                                                                                       | 5mm       |           |           |  | $\rightarrow \qquad \qquad$ |

|                    |                   | Ignore if ou                                                                                    | it of Are | a AA      |           |  | $\uparrow$                                                                                                                                         |

| 4                  | Mura/Waving/ Hot  | Not visible                                                                                     | through   | n 50%     |           |  |                                                                                                                                                    |

|                    | spot              | gray or judge by limit sample if necessary                                                      |           |           |           |  |                                                                                                                                                    |

### \* Note:

- Defect which is on the Black Matrix (outside of active area) are not considered as a defect.

If any specific defect is not included in the above defect table, this defect should be judged by Formike.

- 3. W: Width, L: Length D: Average Diameter N: Count.

16/18 Ver.1.0 www.wandisplay.com

Module No.: KWH070KQ40-F09

## 12. PRECAUTION RELATING & PRODUCT HANDLING

Display is assembled and adjusted with a high degree of precision. Do not attempt to make any alteration or modification.

#### **12.1 SAFETY**

- 12.1.1 If the LCD panel breaks, be careful not to get the liquid crystal to touch your skin.

- 12.1.2 If the liquid crystal touches your skin or clothes, please wash it off immediately by using soap and water.

#### **12.2 HANDLING**

- 12.2.1 Avoid any strong mechanical shock which can break the glass.

- 12.2.2 Avoid static electricity which can damage the CMOS LSI When working with the module, be sure to ground your body and any electrical equipment you may be using. The followings should be noted:

- 12.2.2.1 CMOS-LSI is used for the module circuit; therefore operators should be grounded whenever he/she comes into contact with the module.

- 12.2.2.2 Do not touch any of the conductive parts such as the LSI pads; the copper leads on the PCB and the interface terminals with any parts of the human body.

- 12.2.2.3 Do not touch the connection terminals of the display with bare hand; it will cause disconnection or defective insulation of terminals.

- 12.2.2.4 The modules should be kept in anti-static bags or other containers resistant to static for storage.

- 12.2.2.5 Only properly grounded soldering irons should be used.

- 12.2.2.6 If an electric screwdriver is used, it should be grounded and shielded to prevent sparks.

- 12.2.2.7 The normal static prevention measures should be observed for work clothes and working benches.

- 12.2.3.8 Since dry air is inductive to static, a relative humidity of 50-60% is recommended

- 12.2.3 Do not remove the panel or frame from the module.

- 12.2.4 The polarizing plate of the display is very fragile. Please handle it very carefully, do not touch, push or rub the exposed polarizing with anything harder than an HB pencil lead (glass, tweezers, etc.)

- 12.2.5 Do not wipe the polarizing plate with a dry cloth, as it may easily scratch the surface of plate.

- 12.2.6 Do not touch the display area with bare hands, this will stain the display area.

- 12.2.7 Do not use ketonics solvent & aromatic solvent. Use with a soft cloth soaked with a cleaning naphtha solvent.

- 12.2.8 To control temperature and time of soldering is  $300 \pm 10^{\circ}$  and 3-4 sec.

To avoid liquid (include organic solvent) stained on LCD Module.

#### 12.3 STORAGE

- 12.3.1 Store the panel or module in a dark place where the temperature is  $25^{\circ}$ C ±  $5^{\circ}$ C and the humidity is below 60% RH.

- 12.3.2 Avoid exposure to direct sunlight or to the light of fluorescent lamps.

- 12.3.3 Do not place the module near organic solvents or corrosive gases.

Do not crush, shake, or jolt the module.

#### 12.4 LIMITED WARRANTY

- 12.4.1 FORMIKE modules are not consumer products, but may be incorporated by FORMIKE's customers into consumer products or components thereof, FORMIKE does not warrant that its modules and components are fit for any such particular purpose.

- 12.4.2 The liability of FORMIKE is limited to repair or replacement on the terms set forth below. FORMIKE will not be responsible for any subsequent or consequential events or injury or damage to any personnel or user including third party personnel and/or user. Unless otherwise agreed in writing between FORMIKE and the customer, FORMIKE will only replace or repair any of its Modules which is found defective electrically or visually when inspected in accordance with FORMIKE INSPECTION CRITERIA

- 12.4.3 No warranty can be granted if any of the precautions state in handling liquid crystal display has been disregarded. Broken glass, scratches on polarizer mechanical damages as well as defects that are caused accelerated environment tests are excluded from warranty.

- 12.4.4 In returning the modules, they must be properly packaged; there should be detailed description of the failures or defect.

## 13. OTHERS

- 13.1 If there is any not specified quality standard in this specification as well as RMA, please refer to < INSPECTION CRITERIA>. Contact FORMIKE to get the complete <INSPECTION CRITERIA> by the contact window or feedback@wandisplay.com.

- 13.2 Special agreement of <INSPECTION CRITERIA> is recognized only in writhing between FORMIKE and the customer also indicated it before ordering.

www.wandisplay.com 18/18 Ver.1.0