| INITIALIZATION<br>SEQUENCE<br>NUMBER | INITIALIZATION SEQUENCE DESCRIPTION                                                                                                                            |  |  |  |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Init seq 1                           | Power on                                                                                                                                                       |  |  |  |

| Init seq 2                           | After power is applied and stable, the DSI CLK lanes MUST be in HS state and the DSI data lanes MUST be drived to LP11 state                                   |  |  |  |

| Init seq 3                           | Set EN pin to Low                                                                                                                                              |  |  |  |

| Wait 10 ms <sup>(1)</sup>            |                                                                                                                                                                |  |  |  |

| Init seq 4                           | Tie EN pin to High                                                                                                                                             |  |  |  |

| Wait 10 ms <sup>(1)</sup>            |                                                                                                                                                                |  |  |  |

| Init seq 5                           | Initialize all CSR registers to their appropriate values based on the implementation (The SN65DSI8x is not functional until the CSR registers are initialized) |  |  |  |

| Init seq 6                           | Set the PLL_EN bit (CSR 0x0D.0)                                                                                                                                |  |  |  |

| Wait 10 ms <sup>(1)</sup>            | •                                                                                                                                                              |  |  |  |

| Init seq 7                           | Set the SOFT_RESET bit (CSR 0x09.0)                                                                                                                            |  |  |  |

| Wait 10 ms <sup>(1)</sup>            | <u>'</u>                                                                                                                                                       |  |  |  |

| Init seq 8                           | Change DSI data lanes to HS state and start DSI video stream                                                                                                   |  |  |  |

| Wait 5 ms <sup>(1)</sup>             |                                                                                                                                                                |  |  |  |

| Init seq 9                           | Read back all resisters and confirm they were correctly written                                                                                                |  |  |  |

| Init seq 10                          | Write 0xFF to CSR 0xE5 to clear the error registers                                                                                                            |  |  |  |

| Wait 1 ms <sup>(1)</sup>             | •                                                                                                                                                              |  |  |  |

| Init seq 11                          | Read CSR 0xE5. If CSR 0xE5!= 0x00, then go back to step #2 and re-initialize                                                                                   |  |  |  |

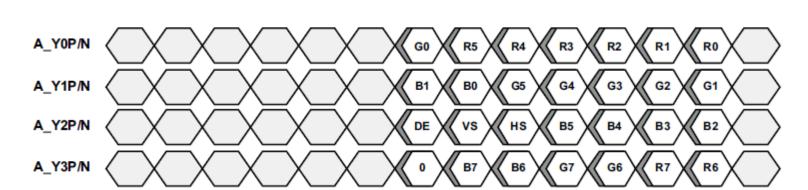

DE = Data Enable

Figure 7-5. FlatLink Output Data (Format 2); Single-Link 24 bpp

| 0xE5 | 7 | CHA_SYNCH_ERR When the DSI channel A packet processor detects an HS or VS synchronization error, that is, an unexpected sync packet; this bit is set; this bit is cleared by writing a 1 value.                                                                                                                                                                 | 0 | R/W1C |

|------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|

|      | 6 | CHA_CRC_ERR When the DSI channel A packet processor detects a data stream CRC error, this bit is set; this bit is cleared by writing a 1 value.                                                                                                                                                                                                                 | 0 | R/W1C |

|      | 5 | CHA_UNC_ECC_ERR When the DSI channel A packet processor detects an uncorrectable ECC error, this bit is set; this bit is cleared by writing a 1 value.                                                                                                                                                                                                          | 0 | R/W1C |

|      | 4 | CHA_COR_ECC_ERR When the DSI channel A packet processor detects a correctable ECC error, this bit is set; this bit is cleared by writing a 1 value.                                                                                                                                                                                                             | 0 | R/W1C |

|      | 3 | CHA_LLP_ERR When the DSI channel A packet processor detects a low level protocol error, this bit is set; this bit is cleared by writing a 1 value. Low-level protocol errors include SoT and EoT sync errors, Escape Mode entry command errors, LP transmission sync errors, and false control errors. Lane merge errors are reported by this status condition. | 0 | R/W1C |

|      | 2 | CHA_SOT_BIT_ERR When the DSI channel A packet processor detects an SoT leader sequence bit error, this bit is set; this bit is cleared by writing a 1 value.                                                                                                                                                                                                    | 0 | R/W1C |

|      | 0 | PLL_UNLOCK This bit is set whenever the PLL Lock status transitions from LOCK to UNLOCK.                                                                                                                                                                                                                                                                        | 1 | R/W1C |