# AN-1730 DP83640 Synchronous Ethernet Mode: Achieving Sub-Nanosecond Accuracy in PTP Applications

#### **ABSTRACT**

This application note first provides a summary of empirical results found when master to slave node synchronization is measured with Synchronous Ethernet mode enabled. Background information is then provided describing the operation of and topological constraints associated with Synchronous Ethernet mode. Typical applications are then described, followed by empirical data which clearly demonstrates the accuracy potential of using Synchronous Ethernet mode.

|                 | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1               | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| 2               | Measuring Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| 3               | Results Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 4               | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|                 | 4.1 Key Terms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|                 | 4.2 Key Configuration Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|                 | 4.3 Enabling Synchronous Ethernet Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|                 | 4.4 DP83640 Clocking Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| E               | 4.5 System Topology Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 5<br>6          | Typical Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| 7               | Measurement Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

| 8               | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| Ü               | CONTROL CONTRO | •  |

|                 | List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 1               | DP83640 Internal Clocks with Synchronous Ethernet Mode Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4  |

| 2               | DP83640 Internal Clocks with Synchronous Ethernet Mode Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4  |

| 3               | DP83640 with Synchronous Ethernet Mode Enabled in a Point to Point Network Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5  |

| 4               | Distributed Master Clock Switch Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6  |

| 5               | 2 Port Synchronous Repeater System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6  |

| 6               | Synchronization Measurement Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7  |

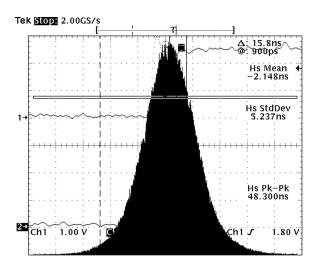

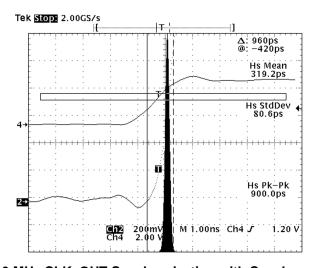

| 7               | Master to Slave 10 MHz CLK_OUT Synchronization with Synchronous Ethernet Mode Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9  |

| 8               | Master to Slave 1 MHz CLK_OUT Synchronization with Synchronous Ethernet Mode Disabled and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|                 | Crystal Slave Reference Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9  |

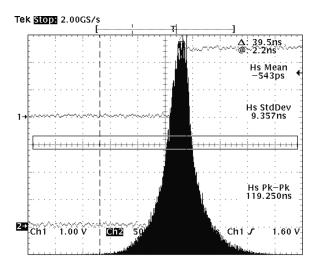

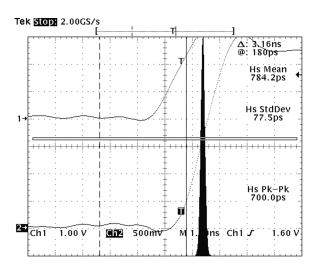

| 9               | Master to Slave 10 MHz CLK_OUT Synchronization with Synchronous Ethernet Mode Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9  |

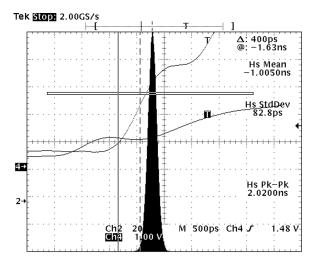

| 10              | Master to Slave 10 MHz CLK_OUT Synchronization with Synchronous Mode Enabled and Crystal Slave Reference Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10 |

| 11              | Master to Slave Synchronization Pulse Per Second Trigger Output with Synchronous Ethernet Mode Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10 |

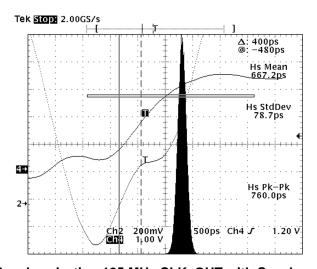

| 12              | Master to Slave Synchronization 125 MHz CLK_OUT with Synchronous Ethernet Mode Enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10 |

|                 | List of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| 1               | Synchronization Output Test Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8  |

| Texas Instrum   | nent is a trademark of Texas Instruments.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

| All other trade | emarks are the property of their respective owners.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

Introduction www.ti.com

### 1 Introduction

Synchronous Ethernet at 100 Mb/s, a feature unique to the Texas Instrument™ DP83640, enables very accurate synchronization between IEEE 1588 Precision Time Protocol (PTP) systems connected via Ethernet. Using this feature, it is possible to maintain sub-nanosecond master to slave synchronization precision in PTP applications operating within required network topological constraints. It is also possible to generate a slave node clock output which is locked and aligned to the Master PTP clock.

This application note is applicable to DP83640.

### 2 Measuring Synchronization

Synchronization accuracy can be defined as the instantaneous time difference between a master clock counter and a corresponding synchronized slave clock counter. Accuracy is determined by measuring the time difference between a master signal which is triggered at a specific time, and a corresponding slave signal which is triggered at the same time using the slave's local synchronized clock counter. Usually, in the context of PTP discussions, these triggered signals occur at 1 second intervals, and are referred to as Pulse Per Second, or PPS, signals.

Depending on the accuracy of the master to slave synchronization, it is also possible to directly measure the phase relationship between outputs from the Master and Slave PTP clocks which control the PTP counters.

In doing such a measurement repeatedly over extended periods, statistical data is gathered which provides a mean, a standard deviation, and a maximum time or "Peak-to-Peak" difference between master and slave clock or PPS signals.

When a slave device is connected to and synchronized with a master device, a fixed phase relationship is established between the master and the slave PTP clocks. This fixed phase relationship is measured as the mean of the statistical data accumulated over time. The extent that this phase relationship can vary is constrained by the resolution of the internal PTP counter. In the DP838640T device, the internal PTP counter (or digital clock) updates in 8 ns increments at a rate of 125 MHz. Thus, the fixed phase relationship, or mean, established between a master and slave device can vary from +8 to -8 ns. Additional variation may also result from any asymmetry in the physical bidirectional path between the master PTP clock and the slave PTP clock.

The mean remains fixed for as long as a synchronization connection is maintained. However, when this connection is broken and then re-established, a new fixed mean is established within the constraints of the sampling clock.

For the purpose of this document, the term "Precision" is used to describe the standard deviation measured between a master and a slave signal corresponding to a fixed mean while synchronization is established.

#### 3 Results Summary

In point-to-point connected PTP systems configured for Synchronous Ethernet operation, tests conducted over extended periods under nominal conditions show master clock to slave clock synchronization can achieve a precision of less than 100 ps with a peak-to-peak measurement of less than 1 ns. These results are roughly 100 times more accurate than similar tests performed with Synchronous Ethernet mode disabled.

Empirical data also demonstrates the ability to produce a slave clock of up to 125 MHz which is locked and aligned to a network connected PTP master clock. Even higher frequency locked clocks are attainable using an external precision clocking device, such as the NSC LMK3000 family of devices.

It is also noteworthy to mention that with Synchronous Ethernet mode enabled, the effects of any local slave reference clock instability are eliminated, since the slave PTP clock is locked to the master clock.

#### 4 Background

The IEEE 1588 Precision Time Protocol provides networked, packet-based synchronization between master and slave systems. When implemented as a purely software-oriented process, systems typically achieve synchronization precision on the order of milliseconds.

www.ti.com Background

By including the hardware-oriented advantages provided by the DP83640 in a PTP-enabled point-to-point connection, it is possible to achieve precision of under 10 ns.

Additionally, by enabling Synchronous Ethernet mode, it is possible to achieve sub-nanosecond precision in point-to-point connections.

In order to utilize Synchronous Ethernet mode, a network system must meet certain topological constraints. To help explain these constraints, some key terms, the internal clocking architecture of the device, and the network topology requirements are described below.

### 4.1 Key Terms

**Master Node:** A master node is a Precision Time Protocol (PTP) enabled network node which contains or propagates a Master PTP clock signal and Master PTP counter data.

**Slave Node:** A slave node is a PTP-enabled network node which contains a Slave PTP clock and counter. A slave node is usually connected to a master node via a network connection. PTP is used to synchronize the slave PTP clock and counter to a master PTP clock and counter.

**PTP Clock:** A PTP clock is the source of an output clock signal which is locked to a PTP counter. In the DP83640, the local PTP clock operates at 250 MHz, and can be configured to control the CLK\_OUT signal. This PTP CLK\_OUT signal is programmable to frequencies which are integral divisions of the 250 MHz PTP clock in the range of 2 and 255 (125 MHz to 0.98 MHz).

**PTP Counter:** A PTP counter contains time information, and is locked to the PTP clock. In a master node, the PTP counter is the source of data used in the Precision Time Protocol for the purpose of synchronizing counters in PTP slave nodes. The PTP counter is incremented every 8 ns.

**Local Reference Clock:** A local reference clock is used for generating network traffic. The local reference clock is embedded into the transmit network packet traffic and is recovered from the network packet traffic at the receiver node. All Ethernet Physical Layer devices use local reference clock sources. Internally, the local reference clock in the DP83640 operates at 125 MHz.

### 4.2 Key Configuration Requirements

For a network node to function as a PTP slave device, the node must be attached to a partner (node, switch, or repeater) which provides access to a Master PTP clock, and the PTP protocol must be enabled and active.

In addition, the partner must have its local reference clock frequency locked to the PTP master clock. If PTP clock phase alignment between the master and slave is also desired, the PTP master clock must be phase-aligned with the master PTP counter. For information on phase aligning the output clock in the DP83640, see *AN-1729 DP83640 IEEE 1588 PTP Synchronized Clock Output* (SNLA099).

It is also important to note that Synchronous Ethernet mode should only be enabled in a device which is utilized as a slave PTP clock node. Enabling Synchronous Ethernet mode in a master node will produce undesired results.

### 4.3 Enabling Synchronous Ethernet Mode

Synchronous Ethernet mode must be enabled in nodes which are designated as slave nodes only. Synchronous Ethernet mode is enabled by simply setting the SYNC\_ENET\_EN bit of the PHYCR2 Extended Page 0 register to 1 (Reg 0x1C:13 = 1).

#### 4.4 DP83640 Clocking Architecture

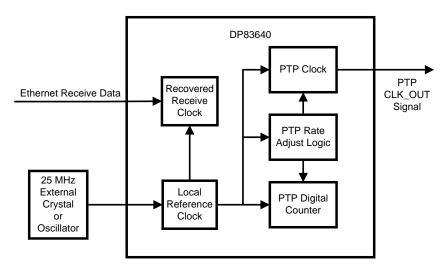

The DP83640 has several internal clocks, including the local reference clock, an Ethernet receive clock, and a PTP clock signal source. An internal PTP digital counter is also included, as well as logic which controls the rate (frequency) of both the digital counter and the PTP clock (see Figure 1).

Background www.ti.com

Figure 1. DP83640 Internal Clocks with Synchronous Ethernet Mode Disabled

An external crystal or oscillator provides the stimulus for the local reference clock. The local reference clock acts as the central source for all clocking in the device. The Receive Clock is recovered from the received Ethernet packet data stream and is locked to the Transmit Clock in the partner.

In normal operation, IEEE 1588 PTP packets are utilized to match the PTP clock and counter in the slave device to the PTP clock and counter in the master device. This matching is accomplished by controlling the rate adjust logic.

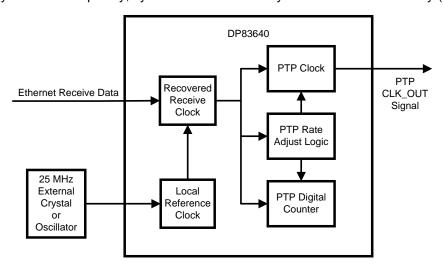

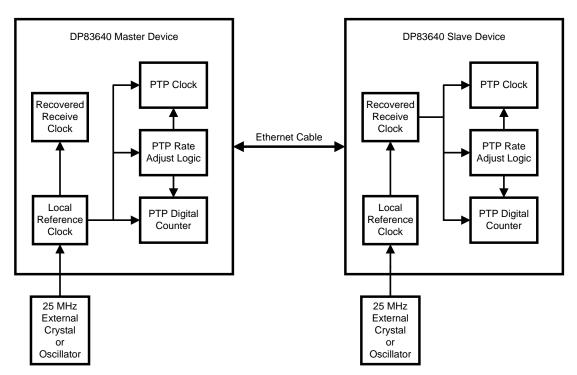

When Synchronous Ethernet mode is enabled, control of the PTP clock, digital counter, and PTP rate adjust logic is switched from the local reference clock to the recovered receive clock (see Figure 2). This has the effect of locking the PTP clock and counter of the slave system to the PTP clock and counter of the master system. Consequently, synchronization accuracy is increased dramatically (see Figure 3).

Figure 2. DP83640 Internal Clocks with Synchronous Ethernet Mode Enabled

www.ti.com Background

Figure 3. DP83640 with Synchronous Ethernet Mode Enabled in a Point to Point Network Topology

## 4.5 System Topology Considerations

As mentioned earlier, for Synchronous Ethernet mode to function, the master node reference clock must be locked to the master PTP clock. This is the default configuration when the DP83640 local reference clock is used by the PTP digital counter and PTP clock. If an external PTP clock source is used in a master system, an external PLL can be used to lock the reference clock source to the external PTP clock.

Note that it is not necessary for a master PTP clock node to utilize a DP83640 device for Synchronous Ethernet mode to function in attached DP83640 slave nodes. Phase locking an external PTP clock to the reference clock input of any Ethernet Physical Layer Interface (Phy) device will suffice.

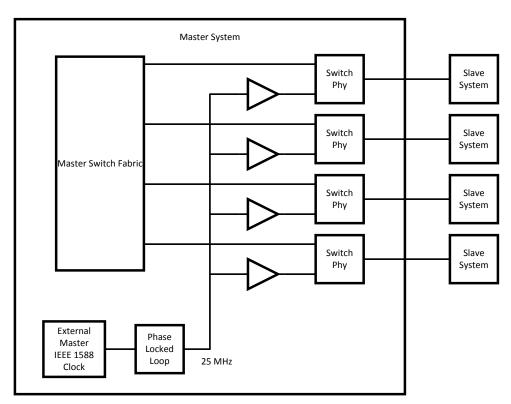

It is possible to synchronize multiple slave devices to a single master clock if a hub or switch architecture is utilized that synchronizes all Ethernet channels to the master PTP clock (see Figure 4).

Typical Applications www.ti.com

Figure 4. Distributed Master Clock Switch Topology

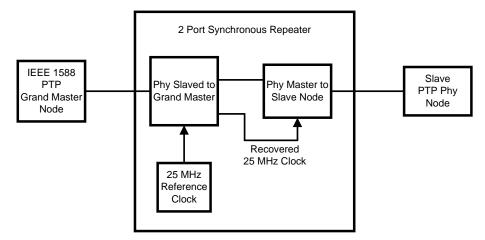

Similarly, it is possible to propagate Synchronous Ethernet mode operation through a switch tree in which each slave switch node synchronizes itself to a master network source connection (see Figure 5).

Figure 5. 2 Port Synchronous Repeater System

### 5 Typical Applications

A typical application for Synchronous Ethernet mode is instrumentation that requires very precise data logging. Using the distributed node example of Figure 4, a master system may trigger a stimulus, such as an energy burst, and each slave node may represent a precision instrument or sensor used to measure the effects of the stimulus at precise times.

Additionally, it may be desirable for an application to propagate a locked clock across several instruments within a local network. Given 1 ns peak-to-peak precision, with Synchronous Ethernet mode enabled, it is possible to trigger multiple instruments to sample data synchronously using 125 MHz output clocks. A greater variety of frequency options become available by using the output clock of the device to control an external PLL clock source, such as a Texas Instruments LMK3000 series device.

Finally, since the frequency of the master clock is delivered through the network, the stability of the local oscillator is not a significant source of error when Synchronous Ethernet mode is enabled. The stability of a slave node is directly dependent upon the stability of its corresponding PTP connected master node. Therefore, special environmental controls are not necessary to maintain synchronization precision. The slave node will achieve the same level of precision with a standard 25 MHz crystal as it would with a high-stability OCXO.

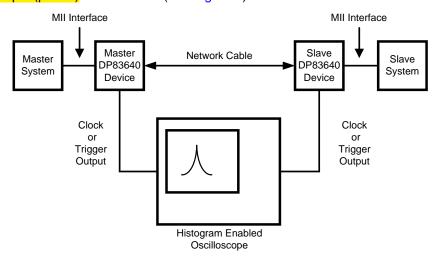

### 6 Synchronization Measurement Setup

As mentioned earlier, synchronization accuracy can be measured by using an oscilloscope to compare the delay between an output signal from a master clock source or node to the corresponding synchronized signal from a slave node. Typically, master and slave output signals are connected to inputs on a scope. The master signal is used to trigger the scope, and the slave signal time is measured against the master trigger signal.

With some oscilloscopes it is possible to enable a histogram function. By accumulating a large sample of slave node output signals, statistical information about the relative synchronization of a slave node to a master mode can be established.

In IEEE 1588 applications, synchronization is typically measured by connecting a pulse per second (PPS) trigger output from a master device and a corresponding PPS signal from a slave device.