## 7.4 Device Functional Modes

## 7.4.1 Reset Implementation

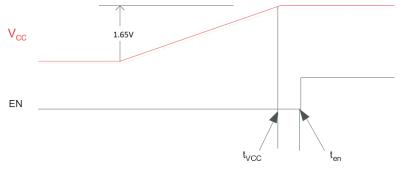

When EN is deasserted (low), the SN65DSI83 device is in shutdown or reset state. In this state, CMOS inputs are ignored, the MIPI D-PHY inputs are disabled and outputs are high impedance. It is critical to transition the EN input from a low level to a high level after the  $V_{CC}$  supply has reached the minimum operating voltage, as shown in Figure 7-1. This is achieved by a control signal to the EN input, or by an external capacitor connected between EN and GND.

Figure 7-1. Cold Start V<sub>CC</sub> Ramp up to EN

Fig 1 Start Vcc Ramp up to EN

| EN, ULPS, RESET    |                             |                             |     | _  |

|--------------------|-----------------------------|-----------------------------|-----|----|

| t <sub>en</sub>    | Enable time from EN or ULPS |                             | 1   |    |

| t <sub>dis</sub>   | Disable time to standby     | t <sub>C(0)</sub> = 12.9 ns | 0.1 | ms |

| t <sub>reset</sub> | Reset Time                  |                             | 10  | ms |

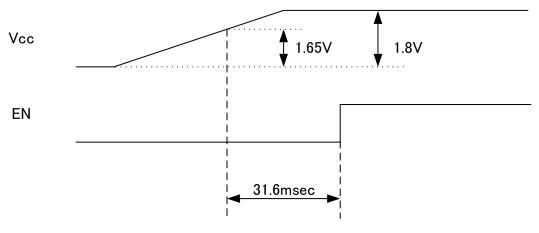

Fig 2 t<sub>en</sub> spec

Fig 3 our system