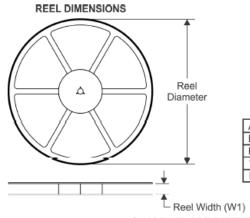

## TAPE AND REEL INFORMATION

## TAPE DIMENSIONS → K0 ←P1→

|    | Cavity — P Ao                                             |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component width     |

|    | Dimension designed to accommodate the component length    |

|    | Dimension designed to accommodate the component thickness |

| W  | Överall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

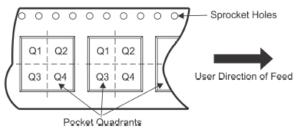

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

\*All dimensions are nominal

|   | Device          | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) |      | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---|-----------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------|------------|------------|------------|-----------|------------------|

| ١ | BQ27Z561YPHR-R1 | DSBGA           | YPH                | 12 | 3000 | 180.0                    | 8.4                      | 1.83 | 2.2        | 0.53       | 4.0        | 8.0       | Q1               |

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| BQ27Z561YPHR-R1 | DSBGA        | YPH             | 12   | 3000 | 182.0       | 182.0      | 20.0        |

| Marking picture | vendor Name | Part No.        | Marking Rule                                                                                                              |

|-----------------|-------------|-----------------|---------------------------------------------------------------------------------------------------------------------------|

| Q27Z561R1       | TI          | BQ27Z561YPHR-R1 | the marking " Q27Z561R1" represents the device name, by identifying units marking Q27Z561R1 correctly to determine device |

| TI Part             | Component            | Homogeneous<br>Material Name.               | Substance<br>Name | *CAS No.  | Substance<br>Mass. (mg) | Content<br>Rate(%) |

|---------------------|----------------------|---------------------------------------------|-------------------|-----------|-------------------------|--------------------|

|                     | Solder Bump          | Copper and Its<br>Alloys                    | Copper            | 7440-50-8 | 0.002245                | 0.599961           |

| BQ27Z561YPHR-<br>R1 |                      | Other<br>Nonferrous<br>Metals and<br>Alloys | Tin               | 7440-31-5 | 0.357353                | 95.500159          |

|                     |                      | Precious Metals                             | Silver            | 7440-22-4 | 0.014593                | 3.89988            |

|                     | Semiconductor Device | Ceramics / Glass                            | Doped<br>Silicon  | 7440-21-3 | 1.485935                | 100                |

| Basic Information                                                                             | Result          |

|-----------------------------------------------------------------------------------------------|-----------------|

| Device Part Number                                                                            | BQ27Z561YPHR-R1 |

| Wafer fab information, process type and node                                                  | foundry         |

| Wafer process was qualified and released to production or not.                                | Mature          |

| Products have been applied with this wafer process?                                           | Yes             |

| Is there any part from the same wafer process family have been used in customer?              | YES             |

| Wafer Process Capability(SPC)                                                                 | Meet SPC Spec   |

| Is there any wafer process CPK<1.33? If yes, please list it and provide the improvement plan. | NO              |

| Chip ID:Do you have chip ID or die ID for this device?                                        | NO              |

| Assembly Factory, Package type                                                                | TI Clark WCSP   |

| Package Size (Length*Width*Height)                                                            | 2.05x1.67x0.4mm |

| Ball/Lead pitch                                                                               | 0.5MM           |

| Is there any part from the same package family h please list the part number.                           | YES                                |                            |  |

|---------------------------------------------------------------------------------------------------------|------------------------------------|----------------------------|--|

| Wire Bonding                                                                                            | Wire composition                   | NA                         |  |

| (Only for Wire Bonding Package)                                                                         | Wire diameter                      | NA                         |  |

| Assembly Process Capability(SPC)                                                                        | Meet spc spec                      |                            |  |

| Is there any assembly process CPK<1.33? If yes, p improvement plan.                                     | lease list it and provide the      | NO                         |  |

| Range of Operation Temperature (Ta, Tj or Tc)                                                           |                                    | -40~85C                    |  |

| Storage Temperature range                                                                               |                                    | -65 ~ 150C                 |  |

| Storage limit                                                                                           |                                    | 1years at customer side    |  |

| Max.Junctioin Temperature                                                                               |                                    | 125C                       |  |

| IFR, Intrinsic Failure Rate, FIT                                                                        |                                    | 1.5FIT@60%CL               |  |

| MSL, Moisture Sensitive Level                                                                           |                                    | MSL 1                      |  |

|                                                                                                         | Оја                                | 64.1°C/W                   |  |

| Theta ja, jc and jb                                                                                     | Ojc                                | 59.8 °C/W                  |  |

|                                                                                                         | Θjb                                | 52.7°C/W                   |  |

|                                                                                                         | НВМ                                | 1500                       |  |

| ESD (HBM、CDM, for all pin)                                                                              | CDM                                | 500                        |  |

| Latch-Up (At max. Ambient Temperature)                                                                  | ,                                  | Meet qual test requirement |  |

| Test Factory                                                                                            |                                    | TI Clark                   |  |

| If the chip is new process or new design, And son beyond JEDEC standard) had been down. Please setails. | ·                                  | NO                         |  |

| Wafer reliability Qualification Report, including: 1                                                    | TDDB, HCI, NBTI, PBTI, EM, SM .etc | YES                        |  |

| Package Qualification Report, including: PC, THB, Bend, PDT, PVT .etc                                   | See TI.com qual report             |                            |  |

| Device Qualification Report, including: ELFR, HTO CDM, LU .etc                                          | See TI.com qual report             |                            |  |

| The device should be done reliability monitoring. Monitoring Report, including: PC, THB, HAST, UH,      | ORT test based on package          |                            |  |

| Characterization report, follow JESD86                                                                  | Refer to datasheet                 |                            |  |

| Component information                                   |                              | Investigation Result     |

|---------------------------------------------------------|------------------------------|--------------------------|

| Ball Compositions and ratio                             |                              | SAC396                   |

| Ball Diameter(µm) before b                              | all attachment               | 0.25MM                   |

| Back side laminate                                      |                              | Yes                      |

| Is there RDL layer in WLCSP                             | ?                            | Yes                      |

| Package standard                                        |                              | JEDEC                    |

| Weight of component (g)                                 |                              | 1.90mg                   |

| Weight/ available P&P areas                             | ≤0.06g/mm2                   | Yes                      |

| Is there polarity point on the                          |                              | Yes                      |

| Is the polarity point sole?                             |                              | Yes                      |

| Is there any specific location component specification? | n number of terminals in     | Yes                      |

| Component orientation can                               | be identified by AOI?        | Yes                      |

| Are matters RoHS complian                               | t and lead free?             | Yes                      |

| Are matters are Halogen-fre                             | ee                           | Yes                      |

|                                                         | Relative humidity (%)        | ≥20%&≤70%                |

|                                                         | Temperature (°C)             | ≥-10C&≤35C               |

| Storage Condition                                       | Maximum storage time (month) | 12Month at customer side |

| Packaging type                                          |                              | Tape and real            |

| Position of component pin 1                             | L in packing                 | Q1                       |

| Packaging height(K0)                                    |                              | 0.53mm                   |

| Packaging width(W)                                      |                              | 8mm                      |

| component pitch:P1                                      |                              | 4mm                      |

| ESD packaging                                           |                              | Yes                      |

| Rollover rate ≤0.05% in pacl                            | king                         | Yes                      |

| tray packing Baking condition                           | ons: 125°C@24h               | Yes                      |

|                                                                                                                                                                                                              | ,                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| reel tape packing Baking conditions: 40°C@192h                                                                                                                                                               | Yes                                      |

| Can reel tape packing meet EIA-481 standard?                                                                                                                                                                 | EIA                                      |

| MSL                                                                                                                                                                                                          | 1                                        |

| MSL>=2,moisture sensitive protection must include: moisture sensitive indicator card, desiccant, moisture sensitive grade logo                                                                               | Yes                                      |

| Baking requirement meet J-STD-033b if moisture                                                                                                                                                               | Yes                                      |

| Maximum soldering times ≥3                                                                                                                                                                                   | Yes                                      |

| Can heat resistance of SMT components meet JSTD020D. (should focus on the classification of temperature and reflow profiles, that is table 4-1, 4-2 and 5-2, please refer to sheet6 J-STD-020D in this file) | Yes                                      |

| Maximum pick-and-place pressure (N)                                                                                                                                                                          | Meet SMT pick-and-place pressure request |

| Whether the welding process and design requirements of component have all written to the component specifications                                                                                            | Yes                                      |

| Whether Pad & stencil design as Mandatory requirements in component spec?                                                                                                                                    | recommended                              |

| Whether the device has special requirements for the reflow temperature ramp-up rata and ramp-down rata? Customer follow J-STD-002 standard                                                                   | No                                       |

| Are there other mandatory requirements in component spec?                                                                                                                                                    | No                                       |

| Solder ability shall be tested per J-STD-002D and the report must be offered,                                                                                                                                | Yes                                      |