# Digital Electrophysiology Interface Chips

11 December 2012; updated 5 September 2013

#### **Features**

- Fully integrated electrophysiology amplifier array with on-chip 16-bit analog-to-digital converter (ADC) and industry-standard serial peripheral interface (SPI)

- ADC operation to 1.05 MSamples per second; supports sampling 32 amplifier channels at 30 kSamples/s each

- Low input-referred noise: 2.4 μV<sub>rms</sub> typical

- Standard four-wire 16-bit SPI interface with CMOS or low-voltage differential signaling (LVDS) I/O pins

- Upper cutoff frequency of all amplifiers set by on-chip registers; adjustable from 100 Hz to 20 kHz

- Lower cutoff frequency of all amplifiers set by on-chip registers; adjustable from 0.1 Hz to 500 Hz

- Integrated multi-frequency in situ electrode impedance measurement capability

- Optional on-chip DSP high-pass filters for amplifier offset removal

- Auxiliary ADC inputs for interfacing additional sensors.

- Individual amplifier power up/down for power minimization

# **Applications**

- Miniaturized multi-channel headstages for neural or ECoG recording

- Low-power wireless headstages or backpacks for electrophysiology experiments

- Recording spikes and/or local field potentials (LFPs) from microelectrodes

- "Smart Petri dish" in vitro recording systems

- Portable EKG or EMG monitoring systems

- Advanced prosthetic limb controller front-ends

## **Description**

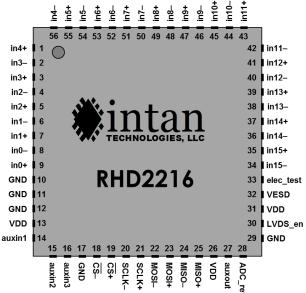

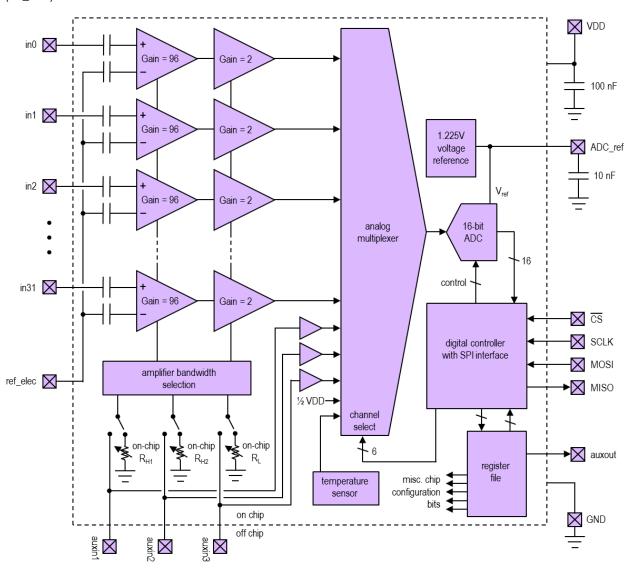

The Intan Technologies RHD2000-series microchips are complete low-power electrophysiology signal acquisition systems. These patent-pending devices contain arrays of low-noise amplifiers with programmable bandwidths and are suitable for a wide variety of biopotential monitoring applications. Innovative circuit architecture combines amplifiers, analog and digital filters, a multiplexed 16-bit analog-to-digital converter (ADC), and a flexible electrode impedance measurement module onto a single silicon chip. In practice, many recording electrodes are connected directly to one side of the chip, and serial digital data exits the other side on a standard SPI bus.

The upper and lower bandwidths of the amplifiers may be dynamically programmed by means of internal registers on each chip. This flexibility allows the chips to be optimized for different types of signals (e.g., 0.1 – 100 Hz for EKG signals, 250 Hz – 7.5 kHz for neural action potentials). Internal capacitors reject DC offset voltages at the input electrodes, eliminating problems with built-in potentials at the electrode-tissue interface.

A low-distortion, high-speed analog multiplexer (MUX) allows many amplifiers to share the on-chip ADC. The ADC can sample each channel up to 30 kSamples/s. Each chip includes three auxiliary input pins for connecting external sensors or other analog voltages which may be sampled using the ADC. Additional on-chip circuitry enables *in situ* electrode impedance measurements at user-programmable frequencies. By transforming weak electrode signals directly into a digital data stream, the RHD2000 replaces all analog instrumentation circuitry in electrophysiology monitoring and acquisition systems.

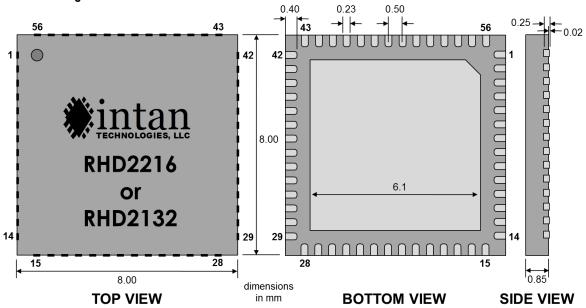

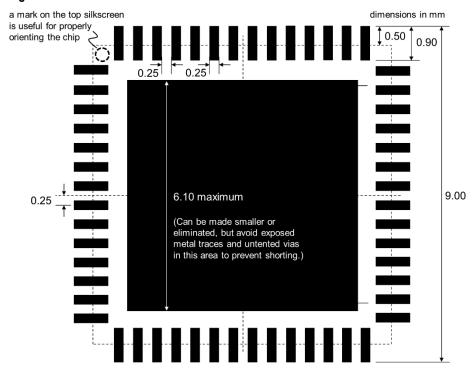

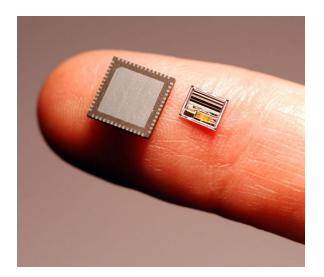

RHD2000-series chips are packaged in standard 8mm × 8mm QFN surface mount packages, or available in bare die form. The small footprint and low power consumption of the multi-channel chips enable the miniaturization of front end electronics for miniature headstages and other wearable or portable biopotential recording systems.

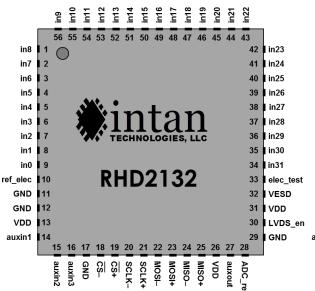

## **Simplified Chip Diagrams**

#### **RHD2000-SERIES FAMILY**

There are three devices in the RHD2000-series electrophysiology interface family: the RHD216 and RHD2132, which are described in this datasheet, and the RHD2164 which is described in its own datasheet available on the Intan Technologies website. The following table lists the features of these chips:

| DEVICE  | AMPLIFIERS<br>PER CHIP | AMPLIFIER INPUT PINS                                      | PACKAGE SIZE            | BARE DIE SIZE   |

|---------|------------------------|-----------------------------------------------------------|-------------------------|-----------------|

| RHD2216 | 16                     | 16 × 2 differential amplifier inputs                      | 8 mm × 8 mm 56-pin QFN  | 4.8 mm × 4.1 mm |

| RHD2132 | 32                     | 32 unipolar amplifier inputs;<br>1 common reference input | 8 mm × 8 mm 56-pin QFN  | 4.8 mm × 4.1 mm |

| RHD2164 | 64                     | 64 unipolar amplifier inputs; 1 common reference input    | 9 mm × 7 mm 104-pin BGA | 7.3 mm × 4.2 mm |

The positive and negative amplifier inputs on the RHD2216 have balanced input impedances; this will provide the best rejection of common-mode noise (most commonly, 50/60 Hz interference) if all electrodes, including reference electrodes, are roughly the same impedance. This is usually the case for surface EMG, EKG, and EEG recording.

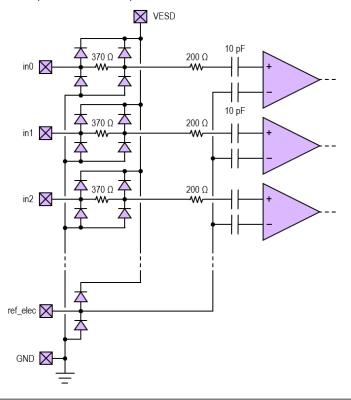

The RHD2132 and RHD2164 can be used in applications where the reference electrode has a much different impedance than the recording electrodes (e.g., microelectrodes for neural recording with a platinum or Ag/AgCl reference wire) or in cases where common-mode noise will not be severe (e.g., implanted devices). The common reference input on the RHD2132 (ref\_elec) is connected to the negative input of all 32 amplifiers, and therefore has an input impedance 32 times lower than the individual amplifier inputs. See the "Electrical Characteristics" section for details.

Simplified functional block diagrams of these chips are shown on the following pages.

# **Package Descriptions**

#### RHD2132: 56-Pin QFN Package

#### RHD2216: 56-Pin QFN Package

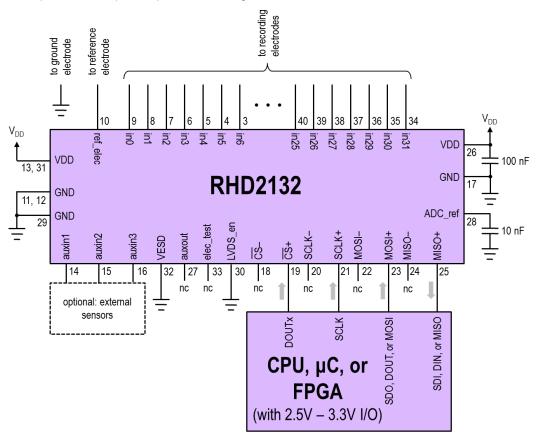

# **RHD2132 Simplified Diagram**

The RHD2132 contains an array of 32 amplifiers having unipolar inputs (in0, in1,...) and a common, shared reference line (ref\_elec).

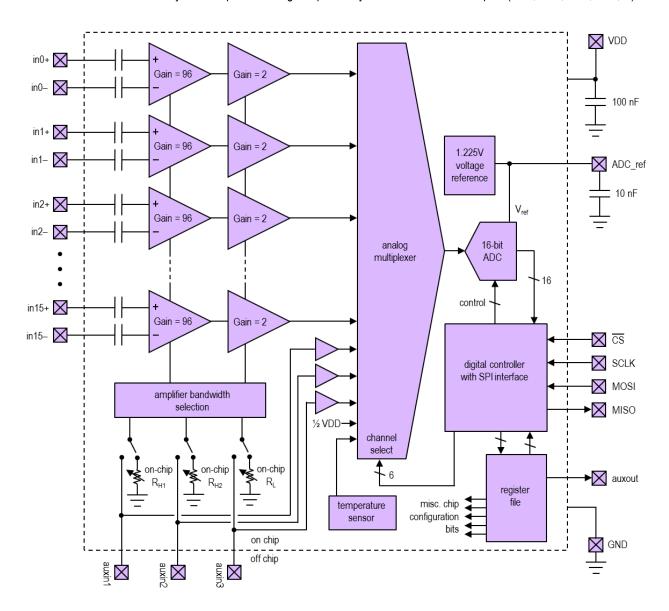

# **RHD2216 Simplified Diagram**

The RHD2216 contains an array of 16 amplifiers having independently accessible differential inputs (in0+, in0-, in1+, in1-,...).

# **Pin Descriptions**

| PIN                       | TYPE                        | FUNCTION                                                                                                                                                                                                                                                                                                                                           |

|---------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD, GND                  | power                       | 3.3V power supply (3.2V – 3.6V). All <b>VDD</b> pins must be connected to the same potential. All <b>GND</b> pins must be connected to the same potential. (See the "Supply Voltage Levels" section for derating under 3.0V operation.)                                                                                                            |

| in0, in1, in2,            | analog inputs               | Unipolar amplifier inputs (RHD2132 only).                                                                                                                                                                                                                                                                                                          |

| ref_elec                  | analog input                | Amplifier array common reference (negative) input (RHD2132 only).                                                                                                                                                                                                                                                                                  |

| in0+, in0–,               | analog inputs               | Differential (bipolar) amplifier inputs (RHD2216 only).                                                                                                                                                                                                                                                                                            |

| LVDS_en                   | digital input               | When <b>LVDS_en</b> is pulled high, communication with the SPI data bus is conducted using low-voltage differential signaling (LVDS). When <b>LVDS_en</b> is pulled low, SPI communication uses traditional CMOS-level signaling.                                                                                                                  |

| CS+, CS-                  | digital LVDS input pair     | Active-low chip select input for SPI data bus. The falling edge of this signal is also used to trigger an ADC sample. If LVDS_en is pulled low, only CS+ is used as a standard CMOS-level input. If LVDS_en is pulled high, both pins are used as an LVDS input pair.                                                                              |

| SCLK+, SCLK-              | digital LVDS input pair     | Serial clock input for SPI data bus. The base value of the clock is zero (CPOL = 0). If LVDS_en is pulled low, only SCLK+ is used as a standard CMOS-level input. If LVDS_en is pulled high, both pins are used as an LVDS input pair.                                                                                                             |

| MOSI+, MOSI-              | digital LVDS input pair     | Serial data input ("Master Out, Slave In") for SPI data bus. The RHD2000 chip always acts as slave in an SPI data link. This line is sampled on the rising edge of SCLK. If LVDS_en is pulled low, only MOSI+ is used as a standard CMOS-level input. If LVDS_en is pulled high, both pins are used as an LVDS input pair.                         |

| MISO+, MISO-              | digital LVDS<br>output pair | Serial data output ("Master In, Slave Out") for SPI data bus. The RHD2000 chip always acts as slave in an SPI data link. The value of this line changes in response to a falling edge on SCLK. If LVDS_en is pulled low, only MISO+ is used as a standard CMOS-level output. If LVDS_en is pulled high, both pins are used as an LVDS output pair. |

| auxin1, auxin2,<br>auxin3 | analog input                | Auxiliary analog inputs to the on-chip ADC (0.10V-2.45V range). Alternatively, off-chip resistors may be connected to these pins to set amplifier bandwidth if the on-chip bandwidth registers are not used. If not used, these pins should be tied to VDD to minimize power dissipation.                                                          |

| auxout                    | digital output              | This pin is an auxiliary CMOS digital output that is controlled or tristated by setting registers on the chip. If not used, this pin should be left unconnected. This pin should never be tied to ground or VDD, as the operation of this pin is undefined at power-up.                                                                            |

| elec_test                 | analog input                | Can be used to inject AC current for electrode impedance measurement or DC voltage for electrode activation. If the on-chip electrode impedance test circuits are used, this pin should be left unconnected. Tying this pin to ground will disable all on-chip and off-chip impedance test capabilities.                                           |

| VESD                      | power                       | Electrostatic discharge protection power line for amplifier inputs. This line should be tied to ground whenever the amplifiers are used. It may be tied to a higher voltage <i>only</i> during electrode activation. (See the "Amplifier Input Protection" section for more information.)                                                          |

| ADC_ref                   | analog output               | An external 10 nF ceramic capacitor to ground must be connected to this pin, and placed in close proximity to the chip to stabilize the on-chip voltage reference generator used by the ADC. A voltage of approximately 1.225V will appear on this pin during operation. See the "Analog-to-Digital Converter" section for more information.       |

# **Electrical Characteristics**

$T_A$  = 25°C,  $V_{DD}$  = 3.3V unless otherwise noted.

| SYMBOL                 | PARAMETER                                                              | CONDITIONS                                                                                | VALUE          | UNITS     | COMMENTS                                                                                                                                            |

|------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{DD}$               | Supply Voltage                                                         |                                                                                           | 3.2 – 3.6      | V         | Recommended nominal supply voltage is 3.3V. See text for derating under 3.0V operation.                                                             |

| $Z_{\text{diginCMOS}}$ | CMOS Digital Input<br>Impedance                                        | <b>LVDS_en</b> = 0                                                                        | 5              | pF        |                                                                                                                                                     |

| ZdiginLVDS             | LVDS Digital Input Impedance                                           | LVDS_en = 1                                                                               | 150            | kΩ        | LVDS inputs are weakly pulled to $V_{DD}$ if unconnected. User must add 100 $\Omega$ termination.                                                   |

| Zauxin                 | Auxiliary Analog Input Impedance                                       | On-chip bandwidth selection enabled                                                       | 4              | pF        |                                                                                                                                                     |

| $V_{inLO}$             | CMOS Digital "Low" Input<br>Voltage                                    | For all non-LVDS digital inputs to chip                                                   | -0.4 –<br>+0.7 | >         | Nominal "low" input voltage is GND (0 V).                                                                                                           |

| V <sub>inHI</sub>      | CMOS Digital "High" Input<br>Voltage                                   | For all non-LVDS digital inputs to chip                                                   | 2.4 – 3.6      | V         | 5V signals should never be applied directly to the chips.                                                                                           |

| $V_{\text{inLVDS-CM}}$ | LVDS Input Common-Mode Voltage                                         |                                                                                           | 1.0 – 1.5      | ٧         | Suggested common-mode level is 1.25 V.                                                                                                              |

| $V_{\text{inLVDS-D}}$  | LVDS Input Differential Voltage                                        |                                                                                           | ±250 –<br>±500 | mV        | Suggested differential voltage is ±350 mV.                                                                                                          |

| VoutLVDS-CM            | LVDS Output Common-Mode Voltage                                        |                                                                                           | 1.25           | V         | Typical                                                                                                                                             |

| $V_{\text{outLVDS-D}}$ | LVDS Output Differential Voltage                                       | With 100 Ω termination                                                                    | ±350           | mV        | Typical                                                                                                                                             |

| AD                     | Amplifier Differential Gain                                            | In midband region between f∟ and fн                                                       | 192<br>45.7    | V/V<br>dB | This gain yields an ADC step size (V <sub>LSB</sub> ) of 0.195 μV, referred to the electrode.                                                       |

| A <sub>0</sub>         | Amplifier DC Differential Gain                                         |                                                                                           | 0              | V/V       | Complete DC rejection, unlike amplifiers that have A <sub>0</sub> = 1 V/V.                                                                          |

| V <sub>LSB</sub>       | Voltage Step Size of ADC (Least Significant Bit)                       | referred to amplifier input                                                               | 0.195          | μV        |                                                                                                                                                     |

|                        |                                                                        | referred to auxiliary<br>ADC input                                                        | 37.4           | μV        |                                                                                                                                                     |

|                        |                                                                        | referred to supply voltage sensor                                                         | 74.8           | μV        |                                                                                                                                                     |

| fL                     | Amplifier Low-Frequency<br>3-dB Cutoff Frequency<br>(High-Pass Filter) | Set by off-chip resistor<br>or on-chip registers;<br>tunable from 0.02 Hz<br>to 1.0 kHz   | 0.02 –<br>1000 | Hz        | 1-pole roll-off below f <sub>L</sub> . On-chip bandwidth selection registers have range of 0.1 Hz-500 Hz.                                           |

| fн                     | Amplifier High-Frequency<br>3-dB Cutoff Frequency<br>(Low-Pass Filter) | Set by two off-chip<br>resistors or on-chip<br>registers; tunable from<br>10 Hz to 20 kHz | 10 –<br>20000  | Hz        | 3-pole 3 <sup>rd</sup> -order Butterworth filter roll-off above f <sub>H</sub> . On-chip bandwidth selection registers have range of 100 Hz-20 kHz. |

# **Electrical Characteristics**

$T_A$  = 25°C,  $V_{DD}$  = 3.3V unless otherwise noted.

| SYMBOL              | PARAMETER                                                                                   | CONDITIONS                                                                                                                | VALUE                 | UNITS           | COMMENTS                                                                                           |

|---------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|----------------------------------------------------------------------------------------------------|

| V <sub>amp-AC</sub> | Amplifier AC Input Voltage<br>Range                                                         |                                                                                                                           | ±5.0                  | mV              |                                                                                                    |

| V <sub>amp-DC</sub> | Amplifier Input Voltage<br>Allowable DC Offset                                              |                                                                                                                           | ±0.4                  | V               | ESD diodes conduct to ground as DC offset increases.                                               |

| Vos                 | Amplifier Input-Referred Offset Voltage                                                     | DSP offset removal filter disabled                                                                                        | < ±100                | μV              | Output offset varies by 192x this value (i.e., ±19.2 mV).                                          |

| CMRR                | Amplifier Common Mode<br>Rejection Ratio                                                    | f = 50 or 60 Hz<br>f = 1 kHz                                                                                              | 82<br>82              | dB<br>dB        | Typical                                                                                            |

| PSRR                | Amplifier Power Supply<br>Rejection Ratio                                                   | f = 50 or 60 Hz<br>f = 1 kHz                                                                                              | 75<br>75              | dB<br>dB        | Typical                                                                                            |

|                     | Amplifier Crosstalk                                                                         | f = 0.1 Hz to 10 kHz                                                                                                      | -68                   | dB              | Typical; measured between adjacent amplifiers on chip.                                             |

| l <sub>b</sub>      | Amplifier Input Bias Current                                                                | -0.2 V <v<sub>IN &lt; +0.2 V<br/>-0.3 V <v<sub>IN &lt; +0.3 V<br/>-0.4 V <v<sub>IN &lt; +0.4 V</v<sub></v<sub></v<sub>    | < 20<br>< 500<br>< 20 | pA<br>pA<br>nA  | Individual amplifier input (inX, inX+, or inX- pin) Voltage referenced to GND.                     |

| I <sub>bREF</sub>   | Amplifier Reference Input Bias<br>Current                                                   | -0.2 V <v<sub>REF &lt; +0.2 V<br/>-0.3 V <v<sub>REF &lt; +0.3 V<br/>-0.4 V <v<sub>REF &lt; +0.4 V</v<sub></v<sub></v<sub> | < 120<br>< 3<br>< 120 | pA<br>nA<br>nA  | Common amplifier reference (ref_elec pin) Voltage referenced to GND.                               |

| Cin                 | Amplifier Input Capacitance                                                                 |                                                                                                                           | 12                    | pF              | Individual amplifier input (inX, inX+, or inX- pin)                                                |

| CinREF              | Amplifier Reference Input Capacitance                                                       | RHD2132                                                                                                                   | 325                   | pF              | Common amplifier reference (ref_elec pin)                                                          |

| Z <sub>in</sub>     | Amplifier Input Impedance                                                                   | f = 10 Hz<br>f = 1 kHz                                                                                                    | 1300<br>13            | MΩ<br>MΩ        | Individual amplifier input (inX, inX+, or inX– pin)                                                |

| Z <sub>inREF</sub>  | Amplifier Reference Input Impedance                                                         | f = 10 Hz, RHD2132<br>f = 1 kHz, RHD2132                                                                                  | 50<br>0.5             | ΜΩ<br>ΜΩ        | Common amplifier reference (ref_elec pin)                                                          |

| Vni                 | Amplifier Input-Referred Noise                                                              |                                                                                                                           | 2.4                   | $\mu V_{rms}$   | Typical. Varies slightly (< 15%) with amplifier bandwidth.                                         |

| THD                 | Amplifier Total Harmonic Distortion (with f <sub>L</sub> = 0.1 Hz, f <sub>H</sub> = 10 kHz) | $f = 1 \text{ kHz}$ $V_{IN} = 4 \text{ mV}_{P-P}$ $V_{IN} = 10 \text{ mV}_{P-P}$                                          | 0.1<br>< 0.8          | %<br>%          | Includes any nonlinearity in MUX. Distortion may increase near f <sub>L</sub> and f <sub>H</sub> . |

| f <sub>MUX</sub>    | Maximum ADC MUX<br>Switching Frequency                                                      |                                                                                                                           | 1.05                  | MHz             | 32 amplifiers can be sampled up to 30 kSamples/s each.                                             |

|                     | Size of Packaged RHD2216 or RHD2132                                                         |                                                                                                                           | 8.0 × 8.0             | mm <sup>2</sup> | 56-pin plastic QFN package (0.85 mm thick)                                                         |

|                     | Mass of Packaged RHD2216<br>or RHD2132                                                      |                                                                                                                           | 168                   | mg              |                                                                                                    |

|                     | Size of RHD2216 or RHD2132<br>Bare Die                                                      |                                                                                                                           | 4.8 × 4.1             | mm²             | Bare silicon die (0.20 mm thick                                                                    |

|                     | Mass of RHD2216 or RHD2132<br>Bare Die                                                      |                                                                                                                           | 11                    | mg              |                                                                                                    |

### **Measured Performance Characteristics**

#### **SAMPLING AMPLIFIERS WITH ON-CHIP ADC**

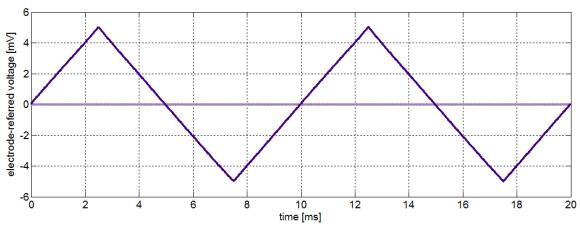

**Figure 1.** Measurement of ±5.0 mV, 100 Hz triangle wave on amplifier channel 1 with ADC running at 30 kS/s per channel, showing large-signal linearity. Amplifier channel 2, also shown, is grounded, showing low noise and lack of crosstalk.

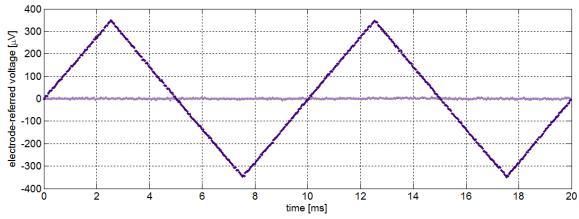

**Figure 2.** Measurement of  $\pm 350~\mu\text{V}$ , 100 Hz triangle wave on amplifier channel 1 with ADC running at 30 kS/s per channel, showing large-signal linearity. Amplifier channel 2, also shown, is grounded, showing low noise and lack of crosstalk.

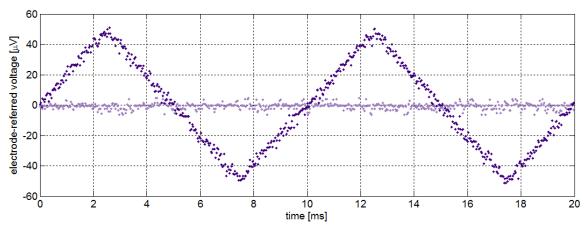

Figure 3. Measurement of  $\pm 50~\mu\text{V}$ , 100 Hz triangle wave on amplifier channel 1 with ADC running at 30 kS/s per channel, showing low noise levels. Amplifier channel 2, also shown, is grounded, showing low noise and lack of crosstalk.

### **Measured Performance Characteristics**

#### **BIOPOTENTIALS MEASURED WITH RHD2000-SERIES AMPLIFIERS**

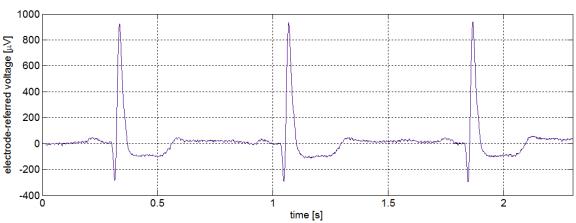

**Figure 4.** EKG signal recorded with RHD2216 using three Ag/AgCl electrodes (**in0+** and **in0-** on chest, 5 cm apart; ground on elbow). Amplifier was configured with  $f_L = 0.1$  Hz,  $f_H = 100$  Hz, and DSP high-pass filter set to 0.6 Hz. ADC sampling rate was 2 kS/s per channel.

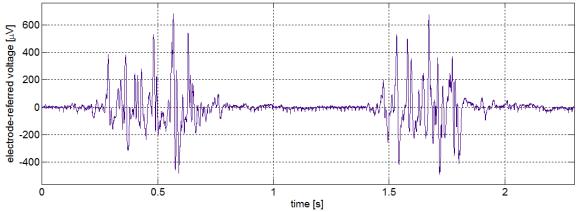

**Figure 5.** EMG signal recorded with RHD2216 using three Ag/AgCl electrodes during bicep contractions (**in0+** and **in0-** on bicep, 5 cm apart; ground on elbow). Amplifier was configured with  $f_L = 2.0$  Hz,  $f_H = 1.0$  kHz, and DSP high-pass filter set to 10 Hz. ADC sampling rate was 4 kS/s per channel.

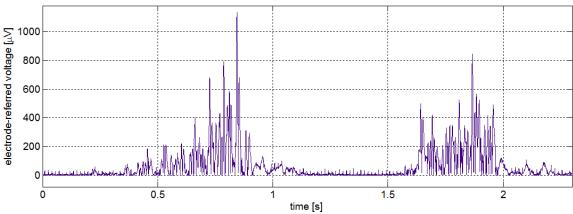

**Figure 6.** EMG signal recorded with RHD2216 with **absmode = 1** using three Ag/AgCl electrodes during bicep contractions (**in0+** and **in0-** on bicep, 5 cm apart; ground on elbow). Amplifier was configured with  $f_L = 2.0$  Hz,  $f_H = 1.0$  kHz, and DSP high-pass filter set to 10 Hz. ADC sampling rate was 4 kS/s per channel. Absolute value calculation is performed on the chip.

### **Measured Performance Characteristics**

#### **NEURAL SIGNALS MEASURED WITH RHD2000-SERIES AMPLIFIERS**

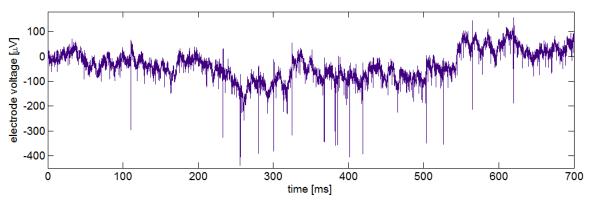

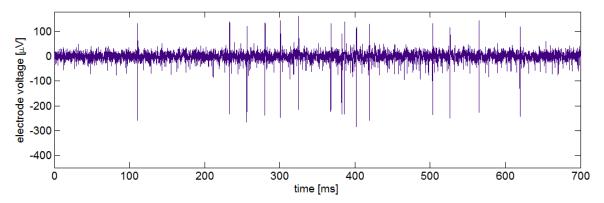

**Figure 7.** Neural action potentials (spikes) and local field potentials (LFPs) recorded in SI/barrel cortex of a freely behaving mouse using RHD2132 and tetrodes constructed from 12 μm nichrome wire, gold plated to an approximate impedance of 300 kΩ at 1 kHz. Amplifier was configured with  $f_L$  = 1 Hz and  $f_H$  = 9.0 kHz, and DSP high-pass filter set to 1 Hz. ADC sampling rate was 30 kS/s per channel. (Data courtesy of Jakob Voigts at MIT, Brown University, and open-ephys.org.)

**Figure 8.** The neural data from Fig. 7 above, high-pass filtered at 300 Hz in software to remove LFPs and isolate spikes. This filtering also could have been performed using the on-chip DSP high-pass filter.

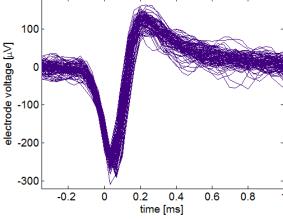

**Figure 9.** Time-aligned neural action potentials from the data shown above in Fig. 8. The time axis has been expanded to show the precise shape of each spike over a 1 ms window.

# **Digital Signaling Modes**

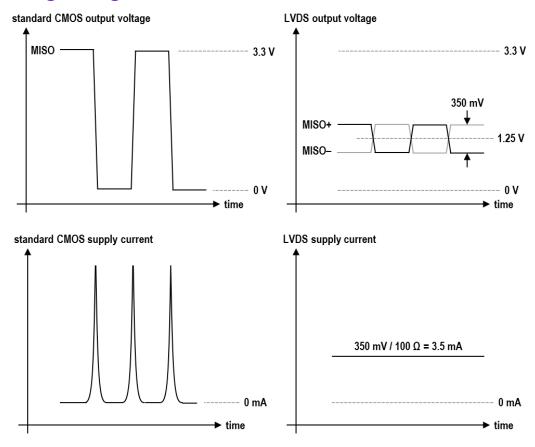

The RHD2000 chips communicate over a standard digital Serial Peripheral Interface (SPI) bus. The bus protocol and data structures used are described in later sections. The voltage levels used to send digital signals over this bus can assume one of two forms: standard CMOS signaling or low-voltage differential signaling (LVDS). The above figure illustrates the differences between a digital value (e.g., MISO) transmitted using these two signaling methods.

#### Standard CMOS Signaling

Standard CMOS signaling (upper left) transmits a digital one or zero by switching the voltage on a single output wire between ground and  $V_{\text{DD}}$ . The current drawn from the power supply (lower left) is nearly zero until the output switches state; at this point, a burst of current is pulled from the power supply to charge or discharge the capacitance of the output wire. These bursts of supply current introduce high frequency noise to the on-chip power supply; this noise can adversely affect noise levels. For typical data streams containing similar numbers of ones and zeros, the dynamic power dissipation of a standard CMOS output driving a wire with capacitance  $C_{\text{wire}}$  at R bits/s is

$$P = \frac{1}{2} C_{\text{wire}} V_{\text{DD}}^2 R.$$

(The actual power dissipation will be slightly higher than this due to secondary effects like the momentary short-circuit current that leaks through CMOS circuits every time they switch state.)

If we operate an RHD2000 at the maximum sampling rate of 1.05 MS/s, the data rate R is 1.05 MHz  $\times$  16 bits = 16.8 Mbit/s. Typical coaxial cables have a capacitance of 100 pF/m. The power required to transmit 16.8 Mbit/s over a 2.0 m cable is approximately 18 mW.

Transmitting high-frequency data reliably over long wires is challenging due to the presence of reflections that occur when a propagating signal reaches the high-impedance input of a digital receiver. These reflections interfere with the transmitted signal and corrupt the data stream. The characteristic impedance  $Z_0$  of a cable is given by

$$Z_0 = \sqrt{L/C}$$

where L is the cable inductance per unit length and C is the cable capacitance per unit length. For most common cable geometries (e.g., coaxial, twisted pair, ribbon),  $Z_0$  falls in the range of  $50-200~\Omega$ . To eliminate reflections, the cable must be terminated with a parallel resistance equal to  $Z_0$ .

Standard CMOS digital outputs lack the current sourcing capability to drive the high DC currents necessary to support  $V_{\text{DD}}\text{-level}$  signals (i.e., 3.3V) across such small resistances, so proper cable termination cannot be used in these cases. A series resistor with a value of  $Z_0$  placed near a CMOS digital output can prevent multiple reflections from the high-impedance input at the far end of a cable by absorbing the first reflection, but this is an imperfect solution that fails with high data rates or long cables.

#### **LVDS Signaling**

LVDS signaling (upper right, previous page) uses a pair of wires (e.g., **MISO+** and **MISO-**) to transmit each digital signal; the wires are terminated with a 100  $\Omega$  resistor tied between them near the LVDS receiver. The average voltage on the wire pair is held roughly at 1.25V, and a 3.5 mA current is forced through the wires in one direction or the other, creating a  $\pm 350$  mV differential voltage across the terminating resistor to signal a digital one or zero.

LVDS signaling offers several advantages over standard CMOS signaling. First, the use of terminated wires drastically reduces reflections, maintaining high signal integrity on long wires and at high data rates. Second, the use of small differential voltages greatly reduces crosstalk to other nearby wires in a cable bundle, especially if twisted pairs are used. Electromagnetic interference and emissions are also minimized using LVDS signaling. Finally, the current drawn from the power supply of the LVDS transmitter is nearly constant (lower right, previous page). This constant current draw does not introduce noise to the on-chip power supply. Thus, LVDS signaling is far better suited for low-noise operation on a chip containing both analog and digital components.

The minimum power dissipation of an LVDS transmitter is given by  $V_{DD}\cdot(3.5~\text{mA})=11.6~\text{mW}$  using a 3.3V power supply. At low frequencies and short wire lengths, standard CMOS signaling can operate at far lower power levels. However, as the calculations in the previous section demonstrate, LVDS can operate at lower power levels when data rates are high and wires are long.

Cables several meters in length can be used with LVDS signaling as long as the geometry of the cable is fairly consistent along its length. Twisted pairs are particularly good structures for LVDS signaling, and many standard cables contain multiple twisted pairs (e.g., USB, HDMI). The DC series resistance of the cable typically has no effect on the performance of the system as long as it is much less than the terminating resistance of 100  $\Omega$ . Signals propagate along standard cables at approximately two-thirds the speed of light, or 20 cm/ns, so a five-meter cable will introduce a round-trip delay of around 50 ns. As long as the SPI controller accounts for these delays, long cables may be used to communicate with the RHD2000 chips reliably.

The LVDS inputs and outputs on the RHD2000 use industry-standard LVDS signal levels. Many commercially available FPGAs and microcontrollers have built-in LVDS I/O pins, and can be interfaced directly with the RHD2000. If a controller lacks LVDS I/O, a wide variety of commercially available LVDS-to-standard-CMOS driver and receiver interface chips may be used to translate signal levels (e.g., TI SN65LVDS, SN65LVDT, DS90LV, and DS90C lines; Fairchild FIN10xx line).

#### **Selecting Signaling Modes on the RHD2000**

If the **LVDS\_en** pin on an RHD2000 is tied to GND, the SPI bus operates with standard CMOS signals, using a single wire for each digital signal. The digital input pins on the RHD2000 interpret any voltage below 0.7V as logic "low" and any voltage above 2.4V as logic "high", so the chip can be interfaced with standard 2.5V, 3.0V, or 3.3V signals. Digital inputs to the RHD2000 should not go below -0.4V, and should never exceed 3.6V. Digital outputs from the RHD2000 chip are driven to ground for logic "low" and to  $V_{DD}$  for logic "high".

If the **LVDS\_en** pin is tied to V<sub>DD</sub>, the SPI bus operates in LVDS mode, where every signal in the SPI bus is represented by a differential voltage across a pair of wires (e.g., **SCLK+** and **SCLK-**). The LVDS inputs on the RHD2000 expect a common-mode voltage near 1.25 V and differential signals near  $\pm 350$  mV, but are fairly tolerant of moderate variations in these values. The LVDS inputs do not include on-chip termination, so a 100  $\Omega$  resistor should be placed between each LVDS input signal pair near the chip. Connection diagrams on the following pages provide examples of termination schemes.

Enabling LVDS mode on the RHD2000 increases current consumption by approximately 5.7 mA. This includes the 3.5 mA of current driven through the MISO output as well as current to power the three on-chip LVDS receivers for CS, SCLK, and MOSI. (Commercial LVDS interface chips typically consume over 17 mA to perform the same functions as the RHD2000 LVDS I/O system.)

#### Increased Noise Levels with Standard CMOS Signaling

If standard CMOS signaling is used in combination with high ADC sampling rates, the amplifier noise levels on the RHD2000 will rise above its nominal value of 2.4  $\mu V_{rms}$ . Even if short wires are used, operating the ADC at 350 kS/s with standard CMOS signaling will increase amplifier noise by at least 10%. Operating the ADC at 1.05 MS/s with standard CMOS signaling will increase amplifier noise by at least 30%. Using long, high-capacitance wires will likely increase the amplifier noise level further. If low noise operation is essential, standard CMOS signaling is recommended only for ADC sampling rates of 175 kS/s or less (i.e., 10 kS/s/channel or less with 16 amplifiers; 5 kS/s/channel or less with 32 amplifiers).

# **Typical Connection Diagram**

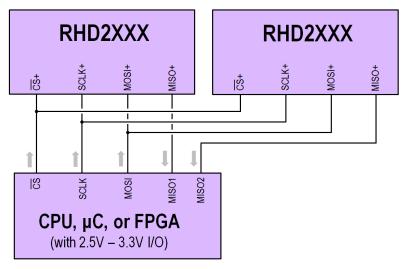

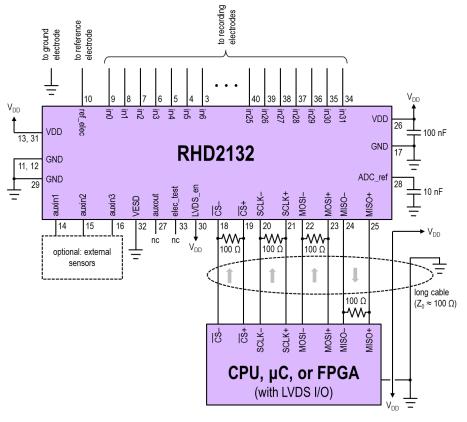

#### STANDARD CMOS SPI INTERFACE (LVDS\_en = 0)

The diagram below shows a typical circuit schematic for a single RHD2132 chip interfaced to a controller that is located in close proximity and uses a standard CMOS four-wire SPI interface. In addition to the chip, only two SMD (surface mount device) capacitors are required for a complete biopotential recording front end.

Additional RHD2000 chips can be added using only one additional MISO wire per chip, provided that all chips receive the same commands in parallel, as shown below.

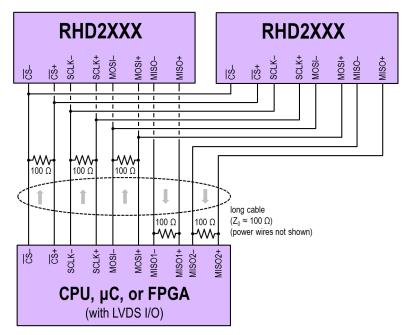

#### LVDS SPI INTERFACE (LVDS\_en = 1)

The diagram below shows a typical circuit schematic for a single RHD2132 chip interfaced to a controller over a long cable, using an SPI interface with low-voltage differential signaling and 100  $\Omega$  termination resistors.

Additional RHD2000 chips can be added as shown below. Only one termination resistor should be used for each LVDS pair (assuming all RHD2000 chip will receive the same commands); this resistor should be located within 20 cm of the RHD2000 chips.

## **SPI Bus Signals**

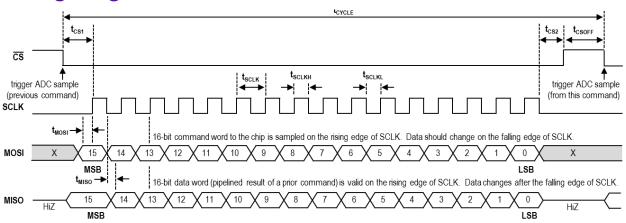

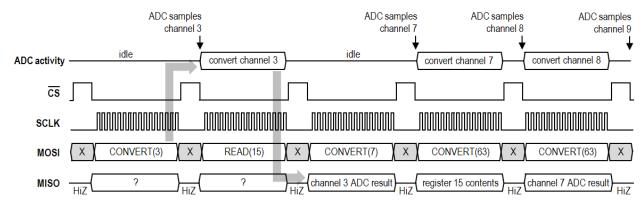

RHD2000 chips communicate using a standard SPI interface consisting of four signals: an active-low chip select (CS); a serial data clock (SCLK) with a base value of zero; a "Master Out, Slave In" data line (MOSI) to receive commands from the master device; and a "Master In, Slave Out" data line (MISO) to send pipelined results from prior commands to the master device. The RHD2000 chip always functions as the SPI slave device. During each chip select cycle, 16-bit data words are transferred in each direction, MSB first. As shown below, the RHD2000 samples MOSI on the rising edge of SCLK. The master should sample MISO on the rising edge of SCLK. (The master device SPI interface should be configured with SPI options CPOL=0 and CPHA=0.) The RHD2000 ADC samples the selected analog signal on the falling edge of CS. The CS line must be pulsed high between every 16-bit data transfer, even when the command word does not request an analog-to-digital conversion.

### **Timing Diagram**

#### SPI BUS TIMING SPECIFICATIONS

$T_A = 25$ °C,  $V_{DD} = 3.3$ V unless otherwise noted.

| SYMBOL            | PARAMETER                                  | MIN  | MAX | UNIT | COMMENTS                                                                              |

|-------------------|--------------------------------------------|------|-----|------|---------------------------------------------------------------------------------------|

| tsclk             | SCLK Period                                | 41.6 |     | ns   | Maximum SCLK frequency is 24 MHz                                                      |

| tsclkh            | SCLK Pulse Width High                      | 20.8 |     | ns   |                                                                                       |

| tsclkl            | SCLK Pulse Width Low                       | 20.8 |     | ns   |                                                                                       |

| tcs1              | CS Low to SCLK High Setup                  | 20.8 |     | ns   |                                                                                       |

| tcs2              | SCLK Low to CS High Setup                  | 20.8 |     | ns   |                                                                                       |

| tcsoff            | CS High Duration                           | 154  |     | ns   |                                                                                       |

| tmosi             | MOSI Data Valid to SCLK High<br>Setup      | 10.4 |     | ns   |                                                                                       |

| t <sub>MISO</sub> | SCLK or CS Falling Edge to MISO Data Valid |      | 12  | ns   |                                                                                       |

| tcycle            | Total Cycle Time Between ADC Samples       | 950  |     | ns   | Maximum sample rate is 1.05 MS/s, or 30 kS/s per channel for 35 multiplexed channels. |

#### **SPI Command Words**

Each RHD2000 chip responds to five basic commands: perform an analog-to-digital conversion on a particular signal; run an ADC self-calibration routine; clear ADC calibration; write to a RAM register; or read from a RAM or ROM register. Each chip contains 18 eight-bit RAM registers that configure various aspects of chip behavior and several eight-bit ROM registers that store basic properties of the chip.

The RHD2000 uses a pipelined communication protocol; each command sent over the MOSI line generates a 16-bit result that is transmitted over the MISO line two commands later. Communication with the chip is illustrated in the following example diagram:

After receiving a CONVERT(C) command, the on-chip ADC samples channel C on the falling edge of the next CS pulse. The analog-to-digital conversion is performed during the next 16 SCLK cycles, and the result is relayed to the master over the MISO line during the following 16 SCLK cycles.

The RHD2000 commands are described by the following bit patterns:

#### Command: CONVERT(C) – Run analog-to-digital conversion on channel C

| MSB |    |      |      |      |      |      |      |   |   |   |   |   |   |   | LSB |

|-----|----|------|------|------|------|------|------|---|---|---|---|---|---|---|-----|

| 15  | 14 | 13   | 12   | 11   | 10   | 9    | 8    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

| 0   | 0  | C[5] | C[4] | C[3] | C[2] | C[1] | C[0] | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Н   |

#### Result:

| MSB   |       |       |       |       |       |      |      |      |      |      |      |      |      |      | LSB  |

|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| 15    | 14    | 13    | 12    | 11    | 10    | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| A[15] | A[14] | A[13] | A[12] | A[11] | A[10] | A[9] | A[8] | A[7] | A[6] | A[5] | A[4] | A[3] | A[2] | A[1] | A[0] |

#### Comments:

The CONVERT(C) command executes an analog-to-digital conversion of analog channel C. Channels 0-31 correspond to the 32 biopotential amplifiers sharing the chip with the ADC. (Only channels 0-15 are active in the RHD2216.) A subset of channels 32-62 are used for auxiliary sensors on and off the chip (see later sections). The conversion result A is sent back to the master (MSB first) two commands later, as shown in the figure above.

A special case of the CONVERT command with C = 63 can be used to cycle through successive amplifier channels. The CONVERT(63) command automatically increments the multiplexer to the next amplifier channel. After reaching the end of the amplifier array, the multiplexer rolls back to channel 0. (Note: The state of the chip is undefined at power-up, so at least one CONVERT(0) command should be sent before executing this variant of the command.)

If the LSB (bit H) of a CONVERT(C) command is set to 1 when DSP offset removal is enabled (see "DSP High-Pass Filter for Offset Removal" section), then the output of the digital high-pass filter associated with amplifier channel C is reset to zero. This can be used to rapidly recover from a large transient and settle to baseline.

#### Command: CALIBRATE - Initiate ADC self-calibration routine

| MS | 3  |    |    |    |    |   |   |   |   |   |   |   |   |   | LSB |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|-----|

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

| 0  | 1  | 0  | 1  | 0  | 1  | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

#### Result:

| Ī | MSB |    |    |    |    |    |   |   |   |   |   |   |   |   |   | LSB |

|---|-----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|-----|

|   | 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

| Ī | *   | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

#### Comments:

The CALIBRATE command initiates an ADC self-calibration routine that should be performed after chip power-up and register configuration. Self-calibration takes many clock cycles to execute; since the ADC clock is derived solely from SCLK, nine "dummy" commands must be sent after a CALIBRATE command (along with the usual SCLK and  $\overline{\text{CS}}$  pulses) to generate the necessary clock cycles. The nine commands following a CALIBRATE command are not executed by the RHD2000; the chip ignores other operations until calibration is complete. The CALIBRATE should only be sent **once** to initiate a calibration sequence; resending this command before calibration is complete will restart calibration from the beginning.

During the entire calibration cycle, the results returned by the RHD2000 consist of all zeros except for the MSB. The MSB will be zero if two's complement mode is enabled (see Register 4 description below); otherwise it will be one.

#### Command: CLEAR - Clear ADC calibration

| <b>ISB</b><br>15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | <b>LSB</b> 0 |

|------------------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|--------------|

| 0                | 1  | 1  | 0  | 1  | 0  | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0            |

#### Result:

| MSB |    |    |    |    |    |   |   |   |   |   |   |   |   |   | LSB |

|-----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|-----|

| 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

| *   | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

#### Comments:

The CLEAR command clears the on-chip calibration parameters acquired by running the CALIBRATE command described above. In the normal operation of the RHD2000, it is not necessary to execute this command.

The result returned by the RHD2000 consists of all zeros except for the MSB. The MSB will be zero if two's complement mode is enabled (see Register 4 description below); otherwise it will be one.

#### Command: WRITE(R,D) - Write data D to register R

| MSB |    |      |      |      |      |      |      |      |      |      |      |      |      |      | LSB  |

|-----|----|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| 15  | 14 | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| 1   | 0  | R[5] | R[4] | R[3] | R[2] | R[1] | R[0] | D[7] | D[6] | D[5] | D[4] | D[3] | D[2] | D[1] | D[0] |

#### Result:

| MSB |    |    |    |    |    |   |   |      |      |      |      |      |      |      | LSB  |

|-----|----|----|----|----|----|---|---|------|------|------|------|------|------|------|------|

| 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| 1   | 1  | 1  | 1  | 1  | 1  | 1 | 1 | D[7] | D[6] | D[5] | D[4] | D[3] | D[2] | D[1] | D[0] |

#### Comments:

The WRITE(R,D) command writes an eight-bit data byte D to chip register R. The data byte D is echoed back to the master in the lower byte of the result so that correct reception of the data byte can be confirmed. The upper byte consists of all ones.

Any attempt to write to a read-only register (or non-existent register) will produce the same result, but in this case D will not be written to the register.

#### Command: READ(R) - Read contents of register R

| MSB |    |      |      |      |      |      |      |   |   |   |   |   |   |   | LSB |

|-----|----|------|------|------|------|------|------|---|---|---|---|---|---|---|-----|

| 15  | 14 | 13   | 12   | 11   | 10   | 9    | 8    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

| 1   | 1  | R[5] | R[4] | R[3] | R[2] | R[1] | R[0] | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

#### Result:

| MSB |    |    |    |    |    |   |   |      |      |      |      |      |      |      | LSB  |

|-----|----|----|----|----|----|---|---|------|------|------|------|------|------|------|------|

| 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| 0   | 0  | 0  | 0  | 0  | 0  | 0 | 0 | D[7] | D[6] | D[5] | D[4] | D[3] | D[2] | D[1] | D[0] |

#### Comments:

The READ(R) command reads the contents of chip register R. The data byte D is sent to the master in the lower byte of the result. The upper byte consists of all zeros.

#### **Unknown Commands:**

If an invalid command is sent (i.e., any command beginning with '01' that does not correspond to ADC calibration commands), the results returned by the chip will consist of all zeros except for the MSB. The MSB will be zero if two's complement mode is enabled (see Register 4 description below); otherwise it will be one.

## **On-Chip Registers**

Each RHD2000 chip is capable of addressing up to 64 eight-bit registers, in any combination of writable (RAM) registers and read-only (ROM) registers. **Upon power-up, all RAM registers contain indeterminate data and should be promptly configured by the SPI master device.** Initialization of registers should be completed at least 100 µs **before** ADC calibration as some registers set parameters that optimize ADC operation.

Individual bits in a register can be changed only by rewriting the entire eight-bit contents. Therefore, it is recommended that the SPI master device maintain a copy of RHD2000 register contents in its memory so bitwise operations can be performed there before writing the updated byte to the chip using a WRITE command on the SPI bus.

The RAM registers present in each RHD2132 and RHD2216 are described below. The detailed functions of some programmable variables are described later in the datasheet. Note: All multi-bit variables have their most significant bits (MSBs) on the left in the diagrams below, towards the direction of the register MSB D[7]. Bits marked X have no function but should be set to zero for compatibility with any future chip versions.

#### Register 0: ADC Configuration and Amplifier Fast Settle

| bit        | D[7]        | D[6]         | D[5]     | D[4]     | D[3]     | D[2]        | D[1]      | D[0]          |

|------------|-------------|--------------|----------|----------|----------|-------------|-----------|---------------|

| Register 0 | ADC referer | nce BW [1:0] | amp fast | amp Vref | ADC comp | arator bias | ADC compa | arator select |

|            |             |              | settle   | enable   | [1       | :0]         | [1:       | :0]           |

**ADC reference BW [1:0]:** This variable configures the bandwidth of an internal ADC reference generator feedback circuit. This variable should always be set to 3.

amp fast settle: Setting this bit to one closes a switch in each amplifier that drives its analog output to the baseline "zero" level. This can be used to quickly recover from large transient events that may drive the amplifiers to their rails. The switch should be closed for a certain amount of time to settle the amplifiers (see "Fast Settle Function" section for details) and then this register should be reset to zero to resume normal amplifier operation.

amp Vref enable: In normal operation, this bit should be set to one to power up voltage references used by the biopotential amplifiers. This bit can be set to zero to reduce power supply current consumption by 180 µA when the amplifiers will not be used for an extended period of time. After setting this bit to one, at least 100 µs must elapse before ADC samples are valid, or before ADC calibration is executed.

**ADC comparator bias [1:0]:** This variable configures the bias current of the ADC comparator. This variable should always be set to 3 for normal operation and ADC calibration. This variable can be set to zero to reduce power supply current consumption by 80 µA when the ADC will not be used for an extended period of time.

**ADC comparator select [1:0]:** This variable selects between four different comparators that can be used by the ADC. This variable should always be set to 2.

#### Register 1: Supply Sensor and ADC Buffer Bias Current

| bit        | D[7] | D[6]      | D[5] | D[4] | D[3]      | D[2]         | D[1] | D[0] |

|------------|------|-----------|------|------|-----------|--------------|------|------|

| Register 1 | Х    | VDD sense |      |      | ADC buffe | r bias [5:0] |      |      |

|            |      | enable    |      |      |           |              |      |      |

**VDD** sense enable: Setting this bit to one enables the on-chip supply voltage sensor, whose output may be sampled by the ADC on channel 48 (see "Supply Voltage Sensor" section for details). If the supply voltage is not sampled, this bit can be set to zero to reduce current consumption by 10  $\mu$ A.

**ADC buffer bias [5:0]:** This variable configures the bias current of an internal reference buffer in the ADC. The optimum value for this variable is a function of ADC sampling rate and is listed in a table in the "Analog-to-Digital Converter" section later in the datasheet.

#### Register 2: MUX Bias Current

| bit        | D[7] | D[6] | D[5] | D[4] | D[3]   | D[2]     | D[1] | D[0] |

|------------|------|------|------|------|--------|----------|------|------|

| Register 2 | Χ    | Χ    |      |      | MUX bi | as [5:0] |      |      |

**MUX bias [5:0]:** This variable configures the bias current of the MUX that routes the selected analog signal to the ADC input. The optimum value for this variable is a function of ADC sampling rate and is listed in a table in the "Analog-to-Digital Converter" section later in the datasheet.

#### Register 3: MUX Load, Temperature Sensor, and Auxiliary Digital Output

| bit        | D[7] | D[6]           | D[5] | D[4]   | D[3]   | D[2]   | D[1]       | D[0]   |

|------------|------|----------------|------|--------|--------|--------|------------|--------|

| Register 3 |      | MUX load [2:0] |      | tempS2 | tempS1 | tempen | digout HiZ | digout |

MUX load [2:0]: This variable configures the total capacitance at the input of the ADC. This variable should always be set to 0.

**tempS1** and **tempS2**: These bits control switches in the on-chip temperature sensor, whose output may be sampled by the ADC on channel 49. The detailed operation of the temperature sensor is described in the "Temperature Sensor" section later in the datasheet. When the temperature sensor is not in use, these bits should each be set to zero to save power.

tempen: Setting this bit to one enables the on-chip temperature sensor. Current consumption may be reduced by approximately 70 µA by setting this bit to zero to disable the sensor.

**digout HiZ:** The RHD2000 chips have an auxiliary digital output pin **auxout** that may be used to activate off-chip circuitry (e.g., MOSFET switches, LEDs, stimulation circuits). Setting this bit to one puts the digital output into high impedance (HiZ) mode.

**digout:** This bit is driven out of the auxiliary CMOS digital output pin **auxout**, provided that the **digout HiZ** bit is set to zero. See the "Auxiliary Digital Output" section for details.

#### Register 4: ADC Output Format and DSP Offset Removal

| bit        | D[7]      | D[6]     | D[5]    | D[4]  | D[3] | D[2] | D[1]         | D[0] |

|------------|-----------|----------|---------|-------|------|------|--------------|------|

| Register 4 | weak MISO | twoscomp | absmode | DSPen |      |      | f freq [3:0] |      |

weak MISO: If this bit is set to zero, the MISO line goes to high impedance mode (HiZ) when  $\overline{CS}$  is pulled high, allowing multiple chips to share the same MISO line so long as only one of their chip select lines is activated at any time. If only one RHD2000 chip will be using a MISO line, this bit may be set to one, and when  $\overline{CS}$  is pulled high the MISO line will be driven weakly by the chip. This can prevent the line from drifting to indeterminate values between logic high and logic low.

**twoscomp:** If this bit is set to one, amplifier conversions from the ADC are reported using a "signed" two's complement representation where the amplifier baseline is reported as zero and values below baseline are reported as negative numbers. If this bit is set to zero, amplifier conversions from the ADC are reported using "unsigned" offset binary notation where the baseline level is represented as 100000000000000. ADC conversions from non-amplifier channels (i.e., C > 31) are always reported as unsigned binary numbers.

**absmode:** Setting this bit to one passes all amplifier ADC conversions through an absolute value function. This is equivalent to performing full-wave rectification on the signals, and may be useful for implementing symmetric positive/negative thresholds or envelope estimation algorithms. This bit has no effect on ADC conversions from non-amplifier channels (i.e., C > 31). See the "Absolute Value Mode" section for more information.

**DSPen:** When this bit is set to one, the RHD2000 performs digital signal processing (DSP) offset removal from all 32 amplifier channels using a first-order high-pass IIR filter. See the "DSP High-Pass Filter for Offset Removal" section for details.

**DSP cutoff freq [3:0]:** This variable sets the cutoff frequency of the DSP filter used to for offset removal. See the "DSP High-Pass Filter for Offset Removal" section for details.

#### **Register 5: Impedance Check Control**

| bit        | D[7] | D[6]      | D[5]   | D[4]     | D[3]       | D[2]     | D[1]    | D[0]      |

|------------|------|-----------|--------|----------|------------|----------|---------|-----------|

| Register 5 | Χ    | Zcheck    | Zcheck | Zcheck s | cale [1:0] | Zcheck   | Zcheck  | Zcheck en |

|            |      | DAC power | load   |          |            | conn all | sel pol |           |

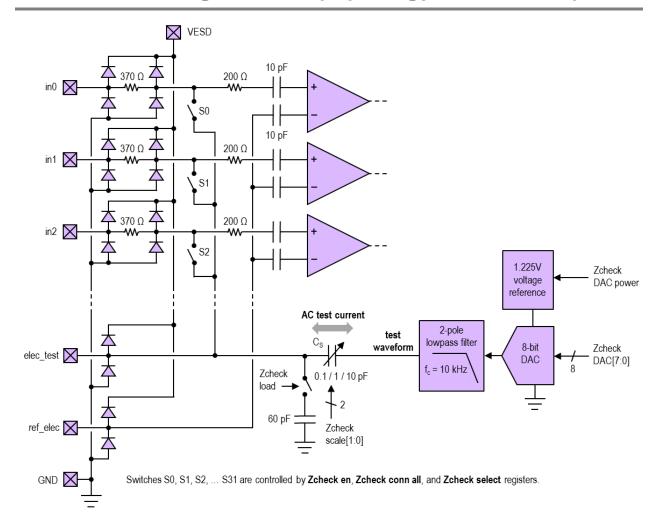

**Zcheck DAC power:** Setting this bit to one activates the on-chip digital-to-analog converter (DAC) used to generate waveforms for electrode impedance measurement. If impedance testing is not being performed, this bit can be set to zero to reduce current consumption by 120 μA. See the "On-Chip AC Current Waveform Generator" section for more information.

**Zcheck load:** Setting this bit to one adds a capacitor load to the impedance checking network. This mode is only used for chip testing at Intan Technologies. This bit should always be set to zero for normal operation.

**Zcheck scale [1:0]:** This variable selects the series capacitor used to convert the voltage waveform generated by the on-chip DAC into an AC current waveform that stimulates a selected electrode for impedance testing: 00 = 0.1 pF; 01 = 1.0 pF; 11 = 10 pF. See the "On-Chip AC Current Waveform Generator" section for more information.

**Zcheck conn all:** Setting this bit to one connects all electrodes together to the **elec\_test** input pin. This is only used for applying DC voltages to electroplate electrodes. In normal operation this bit should be set to zero. See the "Electrode Activation" section for details.

**Zcheck sel pol:** This bit is only used on the RHD2216 where the biopotential amplifiers have separate positive and negative inputs (instead of a reference input common to all amplifiers). Setting this bit to zero selects impedance testing of the positive input of the selected amplifier. Setting the bit to one tests the negative input. See the "Electrode Impedance Test" section for details.

**Zcheck en:** Setting this bit to one activates impedance testing mode, and connects the on-chip waveform generator (and pin **elec\_test**) to the amplifier selected by the **Zcheck select** variable in Register 7. See the "Electrode Impedance Test" section for details.

#### Register 6: Impedance Check DAC

| bit        | D[7] | D[6] | D[5] | D[4]     | D[3]     | D[2] | D[1] | D[0] |

|------------|------|------|------|----------|----------|------|------|------|

| Register 6 |      |      |      | Zcheck D | AC [7:0] |      |      |      |

**Zcheck DAC** [7:0]: This variable sets the output voltage of an 8-bit DAC used to generate waveforms for impedance checking. This variable must be updated at regular intervals to create the desired waveform. Note that this DAC must be enabled by setting **Zcheck DAC power** in Register 5. If impedance testing is not in progress, the value of this register should remain unchanged to minimize noise (although writing the same value to the register is acceptable). See the "On-Chip AC Current Waveform Generator" section for more information.

#### Register 7: Impedance Check Amplifier Select

| bit        | D[7] | D[6] | D[5] | D[4] | D[3]      | D[2]        | D[1] | D[0] |

|------------|------|------|------|------|-----------|-------------|------|------|

| Register 7 | X    | X    |      |      | Zcheck se | elect [5:0] |      |      |

**Zcheck select [5:0]:** This variable selects the amplifier whose electrode will be connected to the on-chip impedance testing circuitry if **Zcheck en** is set to one. In 16- and 32-amplifier chips, the MSB of this six-bit register is ignored. See the "Electrode Impedance Test" section for details.

Registers 8-13: On-Chip Amplifier Bandwidth Select

| bit         | D[7]     | D[6]    | D[5] | D[4] | D[3]          | D[2]          | D[1] | D[0] |

|-------------|----------|---------|------|------|---------------|---------------|------|------|

| Register 8  | offchip  | Х       |      |      | RH1 DA        | AC1 [5:0]     |      |      |

|             | RH1      |         |      |      |               |               |      |      |

| Register 9  | ADC aux1 | X       | Χ    |      |               | RH1 DAC2 [4:0 | )]   |      |

|             | en       |         |      |      |               |               |      |      |

| Register 10 | offchip  | Χ       |      |      | RH2 DA        | AC1 [5:0]     |      |      |

|             | RH2      |         |      |      |               |               |      |      |

| Register 11 | ADC aux2 | Χ       | Χ    |      |               | RH2 DAC2 [4:0 | )]   |      |

|             | en       |         |      |      |               |               |      |      |

| Register 12 | offchip  |         |      |      | RL DAC1 [6:0] | ]             |      |      |

|             | RL       |         |      |      |               |               |      |      |

| Register 13 | ADC aux3 | RL DAC3 |      |      | RL DA         | C2 [5:0]      |      |      |

|             | en       |         |      |      |               |               |      |      |

offchip RH1, offchipRH2, and offchip RL: Setting these bits to one switches from using on-chip programmable resistors for setting amplifier upper and lower bandwidths to using external resistors R<sub>H1</sub>, R<sub>H2</sub>, and R<sub>L</sub> (connected to pins auxin1, auxin2, and/or auxin3) to set amplifier bandwidth. Tables later in the datasheet provide appropriate values for bandwidth-setting resistors.

RH1 DAC1 [5:0], RH1 DAC2 [4:0], RH2 DAC1 [5:0], and RH2 DAC2 [4:0]: These variables set the upper cutoff frequency of the biopotential amplifiers. A table later in the datasheet provides appropriate register values for setting the upper cutoff frequency in the range of 100 Hz to 20 kHz.

**RL DAC1** [6:0], **RL DAC2** [5:0], and **RL DAC3**: These variables set the lower cutoff frequency of the biopotential amplifiers. A table later in the datasheet provides appropriate register values for setting the lower cutoff frequency in the range of 0.1 Hz to 500 Hz.

**ADC aux1 en, ADC aux2 en,** and **ADC aux3 en:** Setting these bits to one when on-chip bandwidth resistors are selected activates buffers that allow the pins **auxin1**, **auxin2**, and **auxin3** to be used as auxiliary ADC inputs. These auxiliary ADC inputs have a range of 0.10V to 2.45V, and correspond to channels 32, 33, and 34. See the "Auxiliary ADC Inputs" section for more information.

Registers 14-17: Individual Amplifier Power

| bit         | D[7]     | D[6]     | D[5]     | D[4]     | D[3]     | D[2]     | D[1]     | D[0]     |

|-------------|----------|----------|----------|----------|----------|----------|----------|----------|

| Register 14 | apwr[7]  | apwr[6]  | apwr[5]  | apwr[4]  | apwr[3]  | apwr[2]  | apwr[1]  | apwr[0]  |

| Register 15 | apwr[15] | apwr[14] | apwr[13] | apwr[12] | apwr[11] | apwr[10] | apwr[9]  | apwr[8]  |

| Register 16 | apwr[23] | apwr[22] | apwr[21] | apwr[20] | apwr[19] | apwr[18] | apwr[17] | apwr[16] |

| Register 17 | apwr[31] | apwr[30] | apwr[29] | apwr[28] | apwr[27] | apwr[26] | apwr[25] | apwr[24] |

apwr [31:0]: Setting these bits to zero powers down individual biopotential amplifiers, saving power if there are channels that don't need to be observed. Each amplifier consumes power in proportion to its upper cutoff frequency. Current consumption is approximately 7.6 µA/kHz per amplifier. Under normal operation, these bits should be set to one.

## **On-Chip Read-Only Registers**

Each RHD2000 chip contains the following ROM registers that provide information on the identity and capabilities of the particular chip.

#### Registers 40-44: Company Designation

The read-only registers 40-44 contain the characters INTAN in ASCII. The contents of these registers can be read to verify the fidelity of the SPI interface.

#### Register 60: Die Revision

| bit         | D[7] | D[6] | D[5] | D[4]      | D[3]       | D[2] | D[1] | D[0] |

|-------------|------|------|------|-----------|------------|------|------|------|

| Register 60 |      |      |      | die revis | sion [7:0] |      |      |      |

die revision [7:0]: This read-only variable encodes a die revision number which is set by Intan Technologies to encode various versions of a chip.

#### Register 61: Unipolar/Bipolar Amplifiers

| bit         | D[7] | D[6]           | D[5] | D[4] | D[3] | D[2] | D[1] | D[0] |

|-------------|------|----------------|------|------|------|------|------|------|

| Register 61 |      | unipolar [7:0] |      |      |      |      |      |      |

unipolar [7:0]: This read-only variable is set to zero if the on-chip biopotential amplifiers have independent differential (bipolar) inputs like the RHD2216 chip. It is set to one if the amplifiers have unipolar inputs and a common reference, like the RHD2132 chip.

#### Register 62: Number of Amplifiers

| bit         | D[7] | D[6] | D[5] | D[4]      | D[3]       | D[2] | D[1] | D[0] |

|-------------|------|------|------|-----------|------------|------|------|------|

| Register 62 |      |      |      | number of | amps [7:0] |      |      |      |

number of amps [7:0]: This read-only variable encodes the total number of biopotential amplifiers on the chip (e.g., 16, 32).

#### Register 63: Intan Technologies Chip ID

| bit         | D[7] | D[6]          | D[5] | D[4] | D[3] | D[2] | D[1] | D[0] |

|-------------|------|---------------|------|------|------|------|------|------|

| Register 63 |      | chip ID [7:0] |      |      |      |      |      |      |

**chip ID [7:0]:** This read-only variable encodes a unique Intan Technologies ID number indicating the type of chip. The chip ID for the RHD2132 is 1. The chip ID for the RHD2216 is 2.

# **Amplifier Bandwidth**

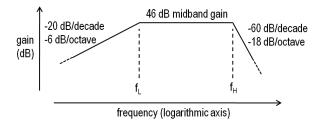

At the core of each RHD2000 chip is an array of low-noise amplifiers with integrated analog filters that can be configured to isolate frequencies of interest and minimize aliasing by attenuating signals above the Nyquist rate (i.e., half the ADC per-channel sampling rate). Each amplifier has a pass band extending from a low-frequency cutoff  $f_{\rm L}$  to a high-frequency cutoff  $f_{\rm H}$ . The upper end of the pass band has a  $3^{\rm rd}$ -order Butterworth low-pass filter at the 3-dB frequency  $f_{\rm H}$ . The lower end of the pass band has a  $1^{\rm st}$ -order high-pass filter characteristic at the 3-dB frequency  $f_{\rm L}$ .

The 3<sup>rd</sup>-order Butterworth low-pass filter characteristic at f<sub>H</sub> has a maximally flat pass band region with -60 dB/decade (-18 dB/octave) of attenuation beyond f<sub>H</sub>. The table below lists filter gains for several frequencies above and below f<sub>H</sub>.

| SIGNAL              | NORMALIZED GAIN |          |  |  |  |

|---------------------|-----------------|----------|--|--|--|

| FREQUENCY           | V/V             | dB       |  |  |  |

| 0.5∙ f <sub>H</sub> | 0.99            | -0.07 dB |  |  |  |

| 0.8· f <sub>H</sub> | 0.89            | -1.0 dB  |  |  |  |

| fн                  | 0.707           | -3.0 dB  |  |  |  |

| 1.2· f <sub>H</sub> | 0.50            | -6.0 dB  |  |  |  |

| 2· f <sub>H</sub>   | 0.12            | -18 dB   |  |  |  |

| 10∙ f <sub>H</sub>  | 0.001           | -60 dB   |  |  |  |

The diagram below illustrates the analog frequency response of the RHD2000 amplifiers:

An additional pole of high-pass filtering can be applied using the optional DSP filter module (see below).

# **Setting Upper Bandwidth**

Registers 8-11 are used to configure on-chip resistors that set the upper bandwidth of the amplifiers ( $f_H$ ) in the range of 100 Hz to 20 kHz. Register values for common bandwidths are listed in a table on the following pages. For bandwidths not listed on this table, contact Intan Technologies for recommended values.

Alternatively, two off-chip resistors,  $R_{H1}$  and  $R_{H2}$ , may be tied to the pins **auxin1** and **auxin2**, respectively, to set the

upper bandwidth of the amplifiers. Using off-chip resistors permits a wider range of  $f_{\rm H}$  to be achieved: 10 Hz to 20 kHz. Standard 1% resistor values are given in the table on the following pages. Any resistor with a power rating of 0.01 W or greater may be used. For bandwidths not listed on this table, interpolate or contact Intan Technologies for recommended resistor values.

If off-chip resistors are used,  $R_{H1}$  and  $R_{H2}$  should be tied from the **auxin1** and **auxin2** pins to chip ground. Care should be taken to minimize parasitic capacitance (such as stray capacitance resulting from long circuit board traces) at the **auxin1** and **auxin2** pins. Resistors should be kept close to the RHD2000 chip on the printed circuit board, particularly when resistor values exceed 1  $M\Omega$ .

## **Setting Lower Bandwidth**

Registers 12-13 are used to configure an on-chip resistor that sets the lower bandwidth of the amplifiers (fL) in the range of 0.1 Hz to 500 Hz. Register values for common bandwidths are listed in a table on the following pages. For bandwidths not listed on this table, contact Intan Technologies for recommended values.

Alternatively, an off-chip resistor  $R_L$  may be tied to the pin **auxin3** to set the lower bandwidth of the amplifiers. Using an off-chip resistor permits a wider range of  $f_L$  to be achieved: 0.02 Hz to 1.0 kHz. Standard 1% resistor values are given in the table on the following pages. For bandwidths not listed on this table, interpolate or contact Intan Technologies for recommended resistor values.

If an off-chip resistor is used,  $R_L$  should be tied between **auxin3** and chip ground. As with  $R_{H1}$  and  $R_{H2}$ , care should be taken in minimize parasitic capacitance on the **auxin3** pin. This resistor should be kept close to the RHD2000 chip on the printed circuit board, particularly when the resistor value exceeds 1  $M\Omega$ .

### **Fast Settle Function**

Due to the potentially long time constant associated with the low cutoff frequency  $f_{\rm L}$ , it may be useful to reset the amplifiers if a large input signal causes the output signals to saturate. To settle the amplifiers, the **amp fast settle** bit in Register 0 should be set high momentarily and then returned to zero. It is recommended (though not required) to hold **amp fast settle** high momentarily after powering up the chip if low values of  $f_{\rm L}$  (< 1 Hz) are used. The recommended duration of a fast settle pulse is  $2.5/f_{\rm H}$ ; as the upper bandwidth of the amplifiers is lowered, settling takes more time. Using this guideline, if  $f_{\rm H}$  is set to 10 kHz then setting **amp fast settle** high for 250  $\mu s$ , and then low, is sufficient to settle the amplifiers to baseline.

# Setting Upper Bandwidth: On-Chip Register Values

The following settings for variables in Registers 8-11 are used to configure the upper bandwidth (fH) of the amplifiers.

| UPPER BANDWIDTH f <sub>H</sub> | RH1<br>DAC1 | RH1<br>DAC2 | RH2<br>DAC1 | RH2<br>DAC2 |

|--------------------------------|-------------|-------------|-------------|-------------|

| 20 kHz                         | 8           | 0           | 4           | 0           |

| 15 kHz                         | 11          | 0           | 8           | 0           |

| 10 kHz                         | 17          | 0           | 16          | 0           |

| 7.5 kHz                        | 22          | 0           | 23          | 0           |

| 5.0 kHz                        | 33          | 0           | 37          | 0           |

| 3.0 kHz                        | 3           | 1           | 13          | 1           |

| 2.5 kHz                        | 13          | 1           | 25          | 1           |

| 2.0 kHz                        | 27          | 1           | 44          | 1           |

| 1.5 kHz                        | 1           | 2           | 23          | 2           |

| 1.0 kHz                        | 46          | 2           | 30          | 3           |

| 750 Hz                         | 41          | 3           | 36          | 4           |

| 500 Hz                         | 30          | 5           | 43          | 6           |

| 300 Hz                         | 6           | 9           | 2           | 11          |

| 250 Hz                         | 42          | 10          | 5           | 13          |

| 200 Hz                         | 24          | 13          | 7           | 16          |

| 150 Hz                         | 44          | 17          | 8           | 21          |

| 100 Hz                         | 38          | 26          | 5           | 31          |

# Setting Upper Bandwidth: Off-Chip Resistor Values

The following resistor values can be used to set amplifier upper bandwidth ( $f_H$ ) if off-chip resistors are used.

| <b>UPPER BANDWIDTH</b> |                 |                 |  |  |  |  |

|------------------------|-----------------|-----------------|--|--|--|--|

| <b>f</b> H             | R <sub>H1</sub> | R <sub>H2</sub> |  |  |  |  |

| 20 kHz                 | 6.80 kΩ         | 11.5 kΩ         |  |  |  |  |

| 15 kHz                 | 9.10 kΩ         | 15.0 kΩ         |  |  |  |  |

| 10 kHz                 | 12.4 kΩ         | 21.0 kΩ         |  |  |  |  |

| 7.5 kHz                | 15.8 kΩ         | 26.7 kΩ         |  |  |  |  |

| 5.0 kHz                | 22.0 kΩ         | 37.4 kΩ         |  |  |  |  |