#### MSP430FR5989-EP

SLASEC9-APRIL 2017

# MSP430FR5989-EP Mixed-Signal Microcontroller

# 1 Device Overview

# 1.1 Features

- Embedded Microcontroller

- 16-Bit RISC Architecture up to 16-MHz Clock

- Wide Supply Voltage Range (1.8 V to 3.6 V)

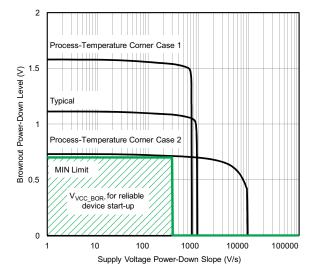

- 1.99-V Minimum Supply Voltage Required for Power Up per SVS<sub>H</sub> Power-Up Level

- Optimized Ultra-Low-Power Modes

- Active Mode: Approximately 100 µA/MHz

- Standby (LPM3 With VLO): 0.4 µA (Typical)

- Real-Time Clock (RTC) (LPM3.5): 0.35 µA (Typical) <sup>(1)</sup>

- Shutdown (LPM4.5): 0.02 µA (Typical)

- Ultra-Low-Power Ferroelectric RAM (FRAM)

- Up to 128KB of Nonvolatile Memory

- Ultra-Low-Power Writes

- Fast Write at 125 ns per Word (64KB in 4 ms)

- Unified Memory = Program + Data + Storage in One Single Space

- 10<sup>15</sup> Write Cycle Endurance

- Radiation Resistant and Nonmagnetic

- Intelligent Digital Peripherals

- 32-Bit Hardware Multiplier (MPY)

- Three-Channel Internal Direct Memory Access (DMA)

- RTC With Calendar and Alarm Functions

- Five 16-Bit Timers With up to 7 Capture/Compare Registers Each

- 16-Bit and 32-Bit Cyclic Redundancy Checker (CRC16, CRC32)

- High-Performance Analog

- 16-Channel Analog Comparator

- 12-Bit Analog-to-Digital Converter (ADC) With Internal Reference and Sample-and-Hold and up to 16 External Input Channels

- Integrated LCD Driver With Contrast Control for up to 320 Segments

- (1) RTC is clocked by a 3.7-pF crystal.

# 1.2 Applications

- Water Meters

- Heat Meters

- Heat Cost Allocators

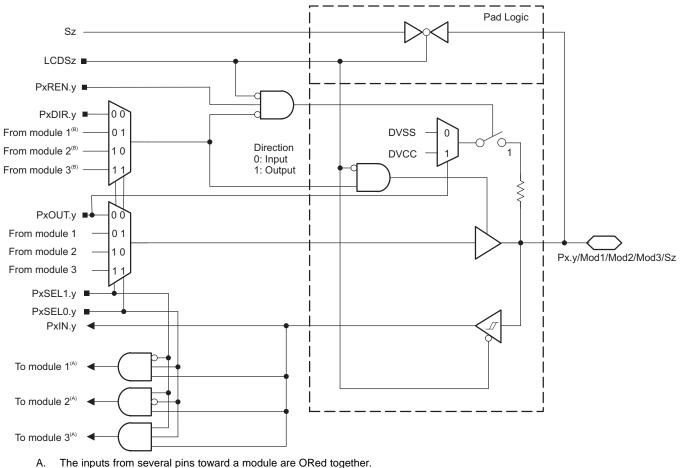

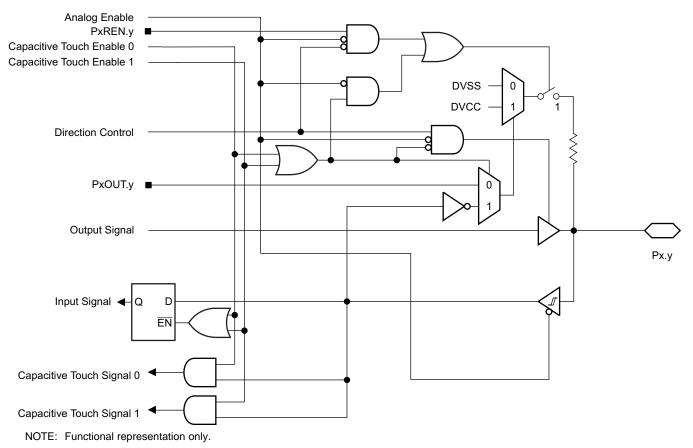

- Multifunction Input/Output Ports

- All P1 to P10 and PJ Pins Support Capacitive Touch Capability Without Need for External Components

- Accessible Bit-, Byte- and Word-Wise (in Pairs)

- Edge-Selectable Wakeup From LPM on Ports P1, P2, P3, and P4

- Programmable Pullup and Pulldown on All Ports

- Code Security

- True Random Number Seed for Random Number Generation Algorithm

- Enhanced Serial Communication

- eUSCI\_A0 and eUSCI\_A1 Support:

- UART With Automatic Baud-Rate Detection

- IrDA Encode and Decode

- SPI

- eUSCI\_B0 and eUSCI\_B1 Support:

- I<sup>2</sup>C With Multiple-Slave Addressing

- SPI

- Hardware UART and I<sup>2</sup>C Bootloader (BSL)

- Flexible Clock System

- Fixed-Frequency DCO With 10 Selectable Factory-Trimmed Frequencies

- Low-Power Low-Frequency Internal Clock Source (VLO)

- 32-kHz Crystals (LFXT)

- High-Frequency Crystals (HFXT)

- Development Tools and Software

- Free Professional Development Environments With EnergyTrace++<sup>™</sup> Technology

- Experimenter and Development Kits

- Controlled Baseline

- One Assembly/Test Site, One Fabrication Site

- Enhanced Diminishing Manufacturing Sources

(DMS) Support

- Enhanced Product-Change Notification

- Qualification Pedigree

- Portable Medical Meters

- Data Logging

# 1.3 Description

The MSP430<sup>™</sup> ultra-low-power (ULP) FRAM platform combines uniquely embedded FRAM and a holistic ultra-low-power system architecture, allowing innovators to increase performance at lowered energy budgets. FRAM technology combines the speed, flexibility, and endurance of SRAM with the stability and reliability of flash at much lower power.

The MSP430 ULP FRAM portfolio consists of a diverse set of devices that feature FRAM, the ULP 16-bit MSP430 CPU, and intelligent peripherals targeted for various applications. The ULP architecture showcases seven low-power modes, which are optimized to achieve extended battery life in energy-challenged applications.

As a high reliability enhanced product, with controlled baseline, extended temperature range (-55°C to 95°C) and gold bond wires in the package, this device is uniquely suited to mission critical applications.

(4)

|                 | Device Information <sup>(1)</sup> |                          |

|-----------------|-----------------------------------|--------------------------|

| PART NUMBER     | PACKAGE                           | BODY SIZE <sup>(2)</sup> |

| MSP430FR5989-EP | VQFN (64)                         | 9.00 mm × 9.00 mm        |

(1) For more information, see Section 8, Mechanical, Packaging, and Orderable Information.

(2) The sizes shown here are approximations. For the package dimensions with tolerances, see the Mechanical Data in Section 8.

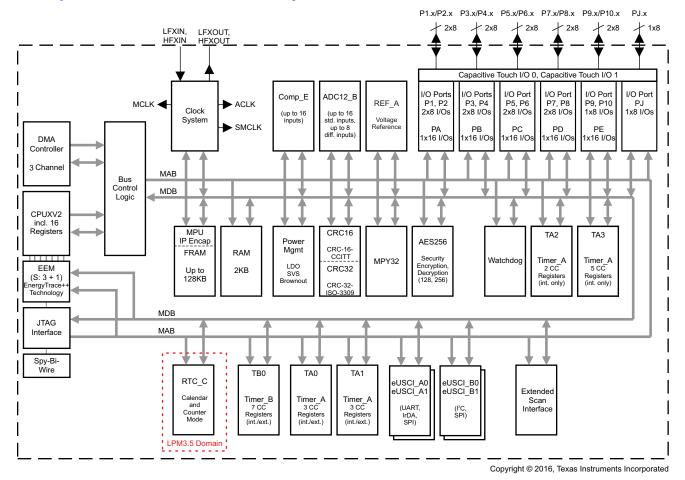

# 1.4 Functional Block Diagram

Figure 1-1 shows the functional block diagram.

TEXAS INSTRUMENTS www.ti.com

# **Table of Contents**

| 1 | Devi | ce Overview                                                                                             | 1      |

|---|------|---------------------------------------------------------------------------------------------------------|--------|

|   | 1.1  | Features                                                                                                | 1      |

|   | 1.2  | Applications                                                                                            |        |

|   | 1.3  | Description                                                                                             | _      |

|   | 1.4  | Functional Block Diagram                                                                                |        |

| 2 | Revi | sion History                                                                                            | 2<br>4 |

| 3 | Term | ninal Configuration and Functions                                                                       | 5      |

|   | 3.1  | Pin Diagram                                                                                             | 5      |

|   | 3.2  | Signal Descriptions                                                                                     |        |

|   | 3.3  | Pin Multiplexing                                                                                        | 12     |

|   | 3.4  | Connection of Unused Pins                                                                               | 12     |

| 4 | Spec | ifications                                                                                              | 13     |

|   | 4.1  | Absolute Maximum Ratings                                                                                | 13     |

|   | 4.2  | ESD Ratings                                                                                             | 13     |

|   | 4.3  | Recommended Operating Conditions                                                                        | 13     |

|   | 4.4  | Active Mode Supply Current Into V <sub>CC</sub> Excluding External Current                              | 14     |

|   | 4.5  | Typical Characteristics, Active Mode Supply Currents                                                    | 15     |

|   | 4.6  | Low-Power Mode (LPM0, LPM1) Supply Currents<br>Into V <sub>CC</sub> Excluding External Current          | 15     |

|   | 4.7  | Low-Power Mode (LPM2, LPM3, LPM4) Supply<br>Currents (Into V <sub>CC</sub> ) Excluding External Current | 16     |

|   | 4.8  | Low-Power Mode With LCD Supply Currents (Into V <sub>CC</sub> ) Excluding External Current              | 18     |

|   | 4.9  | Low-Power Mode LPMx.5 Supply Currents (Into V <sub>CC</sub> ) Excluding External Current                | 19     |

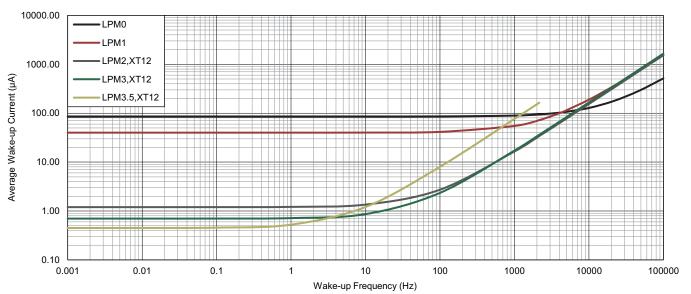

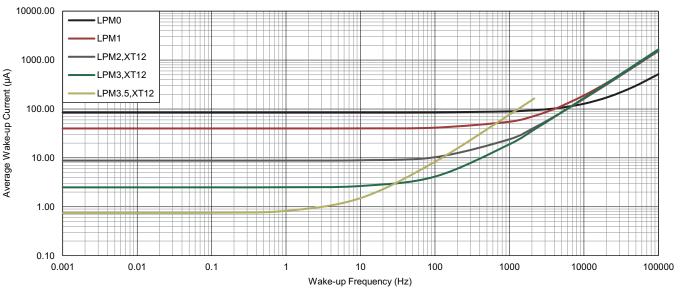

|   | 4.10 | Typical Characteristics, Low-Power Mode Supply Currents                                                 | 20     |

|   | 4.11 | Typical Characteristics, Current Consumption per<br>Module                                              | 21     |

|   | 4.12 | Thermal Resistance Characteristics                                                                      | 22     |

|   |      |                                                                                                         |        |

|   | 4.13  | Timing and Switching Characteristics              | 22         |

|---|-------|---------------------------------------------------|------------|

| 5 | Detai | iled Description                                  | 57         |

|   | 5.1   | Overview                                          | 57         |

|   | 5.2   | CPU                                               | 57         |

|   | 5.3   | Operating Modes                                   | 58         |

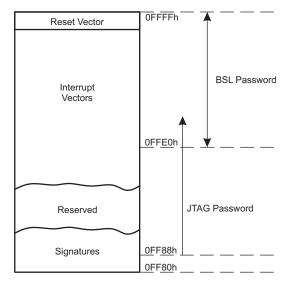

|   | 5.4   | Interrupt Vector Table and Signatures             | <u>61</u>  |

|   | 5.5   | Bootloader (BSL)                                  | <u>64</u>  |

|   | 5.6   | JTAG Operation                                    | 64         |

|   | 5.7   | FRAM                                              | 65         |

|   | 5.8   | RAM                                               | 65         |

|   | 5.9   | Tiny RAM                                          | 65         |

|   | 5.10  | Memory Protection Unit Including IP Encapsulation | 65         |

|   | 5.11  | Peripherals                                       | 66         |

|   | 5.12  | Device Descriptors (TLV)                          | 113        |

|   | 5.13  | Memory                                            | 116        |

|   | 5.14  | Identification                                    | 134        |

| 6 | Appl  | ications, Implementation, and Layout              | 135        |

|   | 6.1   | Device Connection and Layout Fundamentals         | 135        |

|   | 6.2   | Peripheral- and Interface-Specific Design         |            |

|   |       | Information                                       | <u>139</u> |

| 7 | Devi  | ce and Documentation Support                      | <u>143</u> |

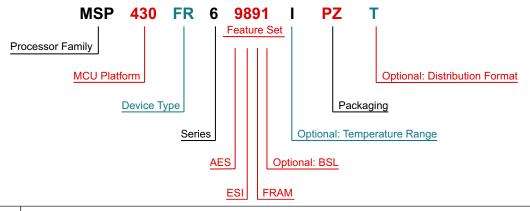

|   | 7.1   | Device and Development Tool Nomenclature          | <u>143</u> |

|   | 7.2   | Tools and Software                                | <u>145</u> |

|   | 7.3   | Documentation Support                             | <u>147</u> |

|   | 7.4   | Community Resources                               | <u>148</u> |

|   | 7.5   | Trademarks                                        | <u>148</u> |

|   | 7.6   | Electrostatic Discharge Caution                   | <u>148</u> |

|   | 7.7   | Export Control Notice                             | <u>148</u> |

|   | 7.8   | Glossary                                          | <u>149</u> |

| 8 |       | nanical, Packaging, and Orderable                 |            |

|   | Infor | mation                                            | <u>149</u> |

SLASEC9-APRIL 2017

# 2 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE       | REVISION | NOTES            |

|------------|----------|------------------|

| April 2017 | *        | Initial release. |

# **3** Terminal Configuration and Functions

# 3.1 Pin Diagram

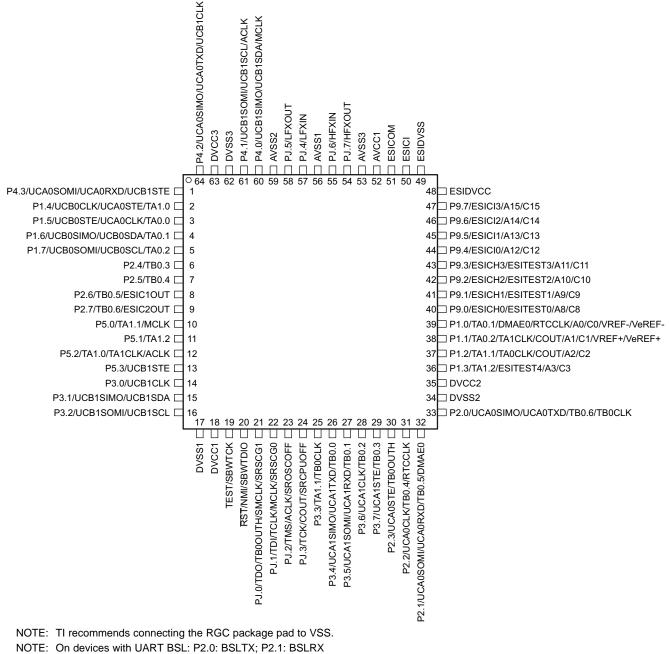

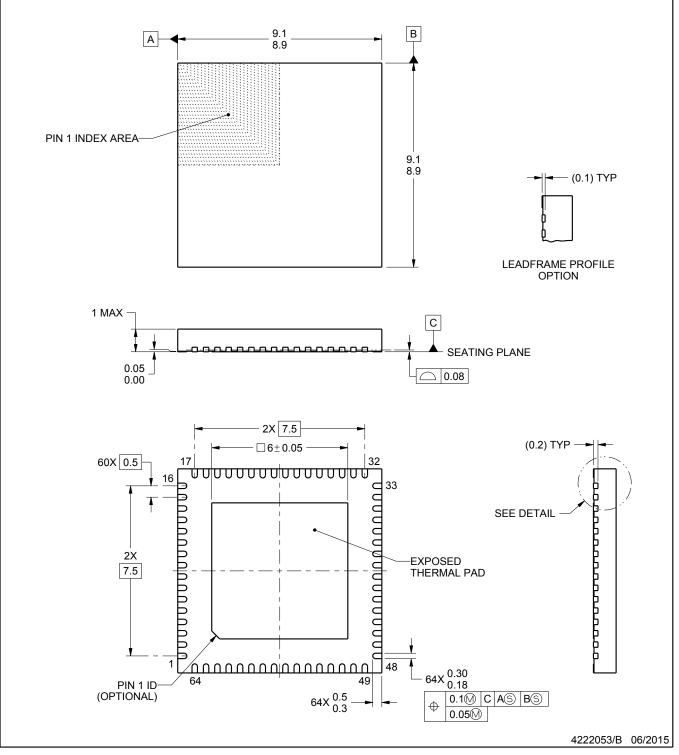

Figure 3-1 shows the pinout of the 64-pin RGC package.

NOTE: On devices with I<sup>2</sup>C BSL: P1.6: BSLSDA; P1.7: BSLSCL

Figure 3-1. 64-Pin RGC Package (Top View) – MSP430FR5989-EP

#### 3.2 **Signal Descriptions**

| Table 3-1. Signal | Descriptions - | - MSP430FR5989-EP |

|-------------------|----------------|-------------------|

|-------------------|----------------|-------------------|

| TERMINAL                          |                             |                                                                                            |  |

|-----------------------------------|-----------------------------|--------------------------------------------------------------------------------------------|--|

|                                   | RGC                         | DESCRIPTION                                                                                |  |

| NAME                              | NO.                         |                                                                                            |  |

|                                   |                             | General-purpose digital I/O                                                                |  |

| P4.3/UCA0SOMI/<br>UCA0RXD/UCB1STE | 1                           | USCI_A0: Slave out, master in (SPI mode), Receive data (UART mode)                         |  |

| CEACKAD/OCB131E                   |                             | USCI_B1: Slave transmit enable (SPI mode)                                                  |  |

|                                   |                             | General-purpose digital I/O                                                                |  |

|                                   |                             | USCI_B0: Clock signal input (SPI slave mode), Clock signal output (SPI master mode)        |  |

| P1.4/UCB0CLK/ UCA0STE/TA1.0       | 2                           | USCI_A0: Slave transmit enable (SPI mode)                                                  |  |

|                                   |                             | Timer_A TA1 CCR0 capture: CCI0A input, compare: Out0 output                                |  |

|                                   |                             | General-purpose digital I/O                                                                |  |

|                                   |                             | USCI_B0: Slave transmit enable (SPI mode)                                                  |  |

| P1.5/UCB0STE/ UCA0CLK/TA0.0       | 3                           | USCI_A0: Clock signal input (SPI slave mode), Clock signal output (SPI master mode)        |  |

|                                   |                             | Timer_A TA0 CCR0 capture: CCI0A input, compare: Out0 output                                |  |

|                                   |                             | General-purpose digital I/O                                                                |  |

|                                   |                             | USCI_B0: Slave in, master out (SPI mode), I <sup>2</sup> C data (I <sup>2</sup> C mode)    |  |

| P1.6/UCB0SIMO/ UCB0SDA/TA0.1      | 4                           | BSL Data (I <sup>2</sup> C BSL)                                                            |  |

|                                   |                             | Timer_A TA0 CCR1 capture: CCI1A input, compare: Out1 output                                |  |

|                                   |                             | General-purpose digital I/O                                                                |  |

| P1.7/UCB0SOMI/ UCB0SCL/TA0.2      | 5                           | USCI_B0: Slave out, master in (SPI mode), I <sup>2</sup> C clock (I <sup>2</sup> C mode)   |  |

| F1.7/0CB0SOMI/ 0CB0SCL/TA0.2      | 5                           | BSL Clock (I <sup>2</sup> C BSL)                                                           |  |

|                                   |                             | Timer_A TA0 CCR2 capture: CCI2A input, compare: Out2 output                                |  |

| P2.4/TB0.3                        | 6                           | General-purpose digital I/O                                                                |  |

|                                   | 0                           | Timer_B TB0 CCR3 capture: CCI3A input, compare: Out3 output                                |  |

| P2.5/TB0.4                        | 7                           | General-purpose digital I/O                                                                |  |

|                                   |                             | Timer_B TB0 CCR4 capture: CCI4A input, compare: Out4 output                                |  |

|                                   |                             | General-purpose digital I/O                                                                |  |

| P2.6/TB0.5/ESIC1OUT               | 8                           | Timer_B TB0 CCR5 capture: CCI5A input, compare: Out5 output                                |  |

|                                   |                             | ESI Comparator 1 output                                                                    |  |

|                                   | 9                           | General-purpose digital I/O                                                                |  |

| P2.7/TB0.6/ESIC2OUT               |                             | Timer_B TB0 CCR6 capture: CCI6A input, compare: Out6 output                                |  |

|                                   |                             | ESI Comparator 2 output                                                                    |  |

|                                   |                             | General-purpose digital I/O                                                                |  |

| P5.0/TA1.1/MCLK                   | 10                          | Timer_A TA1 CCR1 capture: CCI1A input, compare: Out1 output                                |  |

|                                   |                             | MCLK output                                                                                |  |

| P5.1/TA1.2 11                     | General-purpose digital I/O |                                                                                            |  |

|                                   |                             | Timer_A TA1 CCR2 capture: CCI2A input, compare: Out2 output<br>General-purpose digital I/O |  |

|                                   |                             |                                                                                            |  |

| P5.2/TA1.0/TA1CLK/ACLK            | 12                          | Timer_A TA1 CCR0 capture: CCI0B input, compare: Out0 output                                |  |

|                                   |                             | Timer_A TA1 clock signal TA0CLK input                                                      |  |

|                                   |                             | ACLK output                                                                                |  |

| TERMINAL                          |     |                                                                                     |

|-----------------------------------|-----|-------------------------------------------------------------------------------------|

| NAME                              | RGC | DESCRIPTION                                                                         |

| NAME                              | NO. |                                                                                     |

| P5.3/UCB1STE                      | 13  | General-purpose digital I/O                                                         |

|                                   | 10  | USCI_B1: Slave transmit enable (SPI mode)                                           |

| P3.0/UCB1CLK                      | 14  | General-purpose digital I/O                                                         |

|                                   | 1-  | USCI_B1: Clock signal input (SPI slave mode), Clock signal output (SPI master mode) |

|                                   |     | General-purpose digital I/O                                                         |

| P3.1/UCB1SIMO/UCB1SDA             | 15  | USCI_B1: Slave in, master out (SPI mode)                                            |

|                                   |     | USCI_B1: I <sup>2</sup> C data (I <sup>2</sup> C mode)                              |

|                                   |     | General-purpose digital I/O                                                         |

| P3.2/UCB1SOMI/UCB1SCL             | 16  | USCI_B1: Slave out, master in (SPI mode)                                            |

|                                   |     | USCI_B1: I <sup>2</sup> C clock (I <sup>2</sup> C mode)                             |

| DVSS1                             | 17  | Digital ground supply                                                               |

| DVCC1                             | 18  | Digital power supply                                                                |

| TEST/SBWTCK                       | 19  | Test mode pin - select digital I/O on JTAG pins                                     |

|                                   | 10  | Spy-Bi-Wire input clock                                                             |

|                                   |     | Reset input, active low                                                             |

| RST/NMI/SBWTDIO                   | 20  | Nonmaskable interrupt input                                                         |

|                                   |     | Spy-Bi-Wire data input/output                                                       |

|                                   |     | General-purpose digital I/O                                                         |

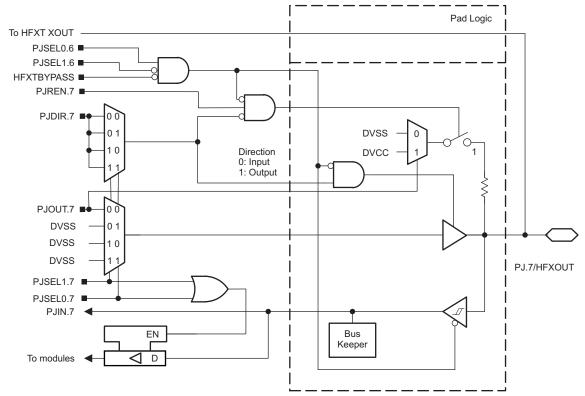

|                                   | 21  | Test data output port                                                               |

| PJ.0/TDO/TB0OUTH/<br>SMCLK/SRSCG1 |     | Switch all PWM outputs high impedance input - Timer_B TB0                           |

|                                   |     | SMCLK output                                                                        |

|                                   |     | Low-power debug: CPU Status register SCG1                                           |

|                                   |     | General-purpose digital I/O                                                         |

|                                   |     | Test data input or test clock input                                                 |

| PJ.1/TDI/TCLK/MCLK/SRSCG0         | 22  | MCLK output                                                                         |

|                                   |     | Low-power debug: CPU Status register SCG0                                           |

|                                   |     | General-purpose digital I/O                                                         |

|                                   |     | Test mode select                                                                    |

| PJ.2/TMS/ACLK/SROSCOFF            | 23  | ACLK output                                                                         |

|                                   |     | Low-power debug: CPU Status register OSCOFF                                         |

|                                   |     | General-purpose digital I/O                                                         |

|                                   |     | Test clock                                                                          |

| PJ.3/TCK/COUT/SRCPUOFF            | 24  | Comparator output                                                                   |

|                                   |     | Low-power debug: CPU Status register CPUOFF                                         |

|                                   |     | General-purpose digital I/O                                                         |

| P3.3/TA1.1/TB0CLK                 | 25  | Timer_A TA1 CCR1 capture: CCI1A input, compare: Out1 output                         |

|                                   | _0  | Timer_B TB0 clock signal TB0CLK input                                               |

|                                   |     | General-purpose digital I/O                                                         |

|                                   | 26  | USCI_A1: Slave in, master out (SPI mode)                                            |

| P3.4/UCA1SIMO/UCA1TXD/TB0.0       |     | USCI_A1: Transmit data (UART mode)                                                  |

|                                   |     |                                                                                     |

|                                   |     | Timer_B TB0 CCR0 capture: CCI0A input, compare: Out0 output                         |

| TERMINAL                     |     |                                                                                     |

|------------------------------|-----|-------------------------------------------------------------------------------------|

| NAME                         | RGC | DESCRIPTION                                                                         |

| NAME                         | NO. |                                                                                     |

|                              |     | General-purpose digital I/O                                                         |

|                              | 77  | USCI_A1: Slave out, master in (SPI mode)                                            |

| P3.5/UCA1SOMI/UCA1RXD/TB0.1  | 27  | USCI_A1: Receive data (UART mode)                                                   |

|                              |     | Timer_B TB0 CCR1 capture: CCI1A input, compare: Out1 output                         |

|                              |     | General-purpose digital I/O                                                         |

| P3.6/UCA1CLK/TB0.2           | 28  | USCI_A1: Clock signal input (SPI slave mode), Clock signal output (SPI master mode) |

|                              |     | Timer_B TB0 CCR2 capture: CCI2A input, compare: Out2 output                         |

|                              |     | General-purpose digital I/O                                                         |

| P3.7/UCA1STE/TB0.3           | 29  | USCI_A1: Slave transmit enable (SPI mode)                                           |

|                              |     | Timer_B TB0 CCR3 capture: CCI3B input, compare: Out3 output                         |

|                              |     | General-purpose digital I/O                                                         |

| P2.3/UCA0STE/TB0OUTH         | 30  | USCI_A0: Slave transmit enable (SPI mode)                                           |

|                              |     | Switch all PWM outputs high impedance input - Timer_B TB0                           |

|                              |     | General-purpose digital I/O                                                         |

| P2.2/UCA0CLK/TB0.4/RTCCLK    | 21  | USCI_A0: Clock signal input (SPI slave mode), Clock signal output (SPI master mode) |

| F2.2/UCAUCEN/TB0.4/RTCCER    | 31  | Timer_B TB0 CCR4 capture: CCI4B input, compare: Out4 output                         |

|                              |     | RTC clock output for calibration                                                    |

|                              |     | General-purpose digital I/O                                                         |

|                              |     | USCI_A0: Slave out, master in (SPI mode)                                            |

| P2.1/UCA0SOMI/UCA0RXD/TB0.5/ |     | USCI_A0: Receive data (UART mode)                                                   |

| DMAE0                        | 32  | BSL receive (UART BSL)                                                              |

|                              |     | Timer_B TB0 CCR5 capture: CCI5B input, compare: Out5 output                         |

|                              |     | DMA external trigger input                                                          |

|                              |     | General-purpose digital I/O                                                         |

|                              |     | USCI_A0: Slave in, master out (SPI mode)                                            |

| P2.0/UCA0SIMO/UCA0TXD/TB0.6/ | 22  | USCI_A0: Transmit data (UART mode)                                                  |

| TBOCLK                       | 33  | BSL transmit (UART BSL)                                                             |

|                              |     | Timer_B TB0 CCR6 capture: CCI6B input, compare: Out6 output                         |

|                              |     | Timer_B TB0 clock signal TB0CLK input                                               |

| DVSS2                        | 34  | Digital ground supply                                                               |

| DVCC2                        | 35  | Digital power supply                                                                |

|                              |     | General-purpose digital I/O                                                         |

|                              |     | ESI test signal 4                                                                   |

| P1.3/ESITEST4/TA1.2/A3/C3    | 36  | Timer_A TA1 CCR2 capture: CCI2A input, compare: Out2 output                         |

|                              |     | Analog input A3                                                                     |

|                              |     | Comparator input C3                                                                 |

| TERMINAL                                       |     |                                                             |

|------------------------------------------------|-----|-------------------------------------------------------------|

| NAME                                           | RGC | DESCRIPTION                                                 |

|                                                | NO. |                                                             |

|                                                |     | General-purpose digital I/O                                 |

|                                                |     | Timer_A TA1 CCR1 capture: CCI1A input, compare: Out1 output |

| P1.2/TA1.1/TA0CLK/COUT/A2/C2                   | 37  | Timer_A TA0 clock signal TA0CLK input                       |

|                                                |     | Comparator output                                           |

|                                                |     | Analog input A2                                             |

|                                                |     | Comparator input C2                                         |

|                                                |     | General-purpose digital I/O                                 |

|                                                |     | Timer_A TA0 CCR2 capture: CCI2A input, compare: Out2 output |

|                                                |     | Timer_A TA1 clock signal TA1CLK input                       |

| P1.1/TA0.2/TA1CLK/<br>COUT/A1/C1/VREF+/ VeREF+ | 38  | Comparator output                                           |

| COUTATICI/VREF#/ VeREF#                        |     | Analog input A1                                             |

|                                                |     | Comparator input C1                                         |

|                                                |     | Output of positive reference voltage                        |

|                                                |     | Input for an external positive reference voltage to the ADC |

|                                                |     | General-purpose digital I/O                                 |

|                                                |     | Timer_A TA0 CCR1 capture: CCI1A input, compare: Out1 output |

|                                                |     | DMA external trigger input                                  |

| P1.0/TA0.1/DMAE0/ RTCCLK/A0/C0/                | 39  | RTC clock output for calibration                            |

| VREF-/VeREF-                                   |     | Analog input A0                                             |

|                                                |     | Comparator input C0                                         |

|                                                |     | Output of negative reference voltage                        |

|                                                |     | Input for an external negative reference voltage to the ADC |

|                                                |     | General-purpose digital I/O                                 |

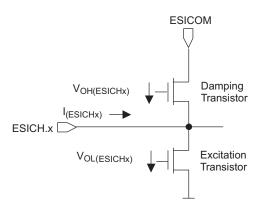

| P9.0/ESICH0/ESITEST0/A8/C8                     | 40  | ESI channel 0 sensor excitation output and signal input     |

|                                                |     | ESI test signal 0<br>Analog input A8; comparator input C8   |

|                                                |     | General-purpose digital I/O                                 |

|                                                |     | ESI channel 1 sensor excitation output and signal input     |

| P9.1/ESICH1/ESITEST1/ A9/C9                    | 41  | ESI test signal 1                                           |

|                                                |     | Analog input A9                                             |

|                                                |     | Comparator input C9                                         |

|                                                |     | General-purpose digital I/O                                 |

|                                                |     | ESI channel 2 sensor excitation output and signal input     |

| P9.2/ESICH2/ESITEST2/A10/C10                   | 42  | ESI test signal 2                                           |

|                                                |     | Analog input A10                                            |

|                                                |     | Comparator input C10                                        |

|                                                |     | General-purpose digital I/O                                 |

|                                                |     | ESI channel 3 sensor excitation output and signal input     |

| P9.3/ESICH3/ESITEST3/A11/C11                   | 43  | ESI test signal 3                                           |

|                                                |     | Analog input A11                                            |

|                                                |     | Comparator input C11                                        |

Copyright © 2017, Texas Instruments Incorporated

| TERMINAL                   |     |                                                         |

|----------------------------|-----|---------------------------------------------------------|

| NAME                       | RGC | DESCRIPTION                                             |

|                            | NO. |                                                         |

|                            |     | General-purpose digital I/O                             |

| P9.4/ESICI0/A12/C12        | 44  | ESI channel 0 signal input to comparator                |

| 1 0.4/2010/0//12/012       |     | Analog input A12                                        |

|                            |     | Comparator input C12                                    |

|                            |     | General-purpose digital I/O                             |

| P9.5/ESICI1/A13/C13        | 45  | ESI channel 1 signal input to comparator                |

| P9.5/ESICH/A15/C13         | 45  | Analog input A13                                        |

|                            |     | Comparator input C13                                    |

|                            |     | General-purpose digital I/O                             |

|                            |     | ESI channel 2 signal input to comparator                |

| P9.6/ESICI2/A14/C14        | 46  | Analog input A14                                        |

|                            |     | Comparator input C14                                    |

|                            |     | General-purpose digital I/O                             |

|                            |     | ESI channel 3 signal input to comparator                |

| P9.7/ESICI3/A15/C15        | 47  | Analog input A15                                        |

|                            |     | Comparator input C15                                    |

| ESIDVCC                    | 48  | ESI Power supply                                        |

| ESIDVSS                    | 49  | ESI Ground supply                                       |

| ESICI                      | 50  | ESI Scan IF input to Comparator                         |

| ESICOM                     | 51  | ESI Common termination for Scan IF sensors              |

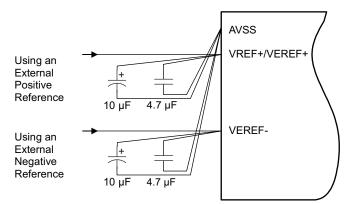

| AVCC1                      | 52  | Analog power supply                                     |

| AVSS3                      | 53  | Analog ground supply                                    |

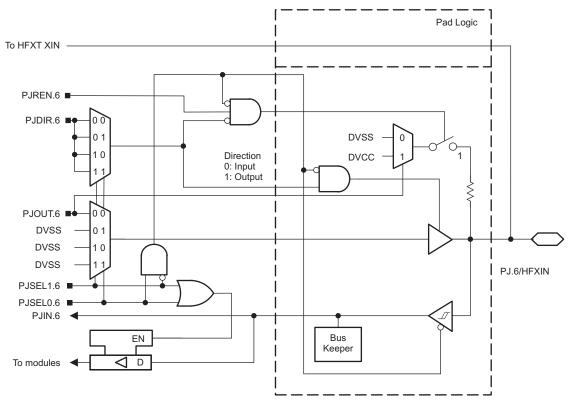

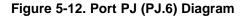

| PJ.7/HFXOUT                | 54  | General-purpose digital I/O                             |

|                            |     | Output terminal of crystal oscillator XT2               |

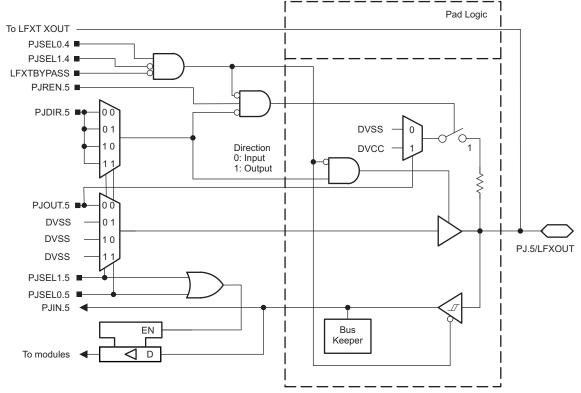

| PJ.6/HFXIN                 | 55  | General-purpose digital I/O                             |

|                            |     | Input terminal for crystal oscillator XT2               |

| AVSS1                      | 56  | Analog ground supply                                    |

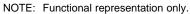

| PJ.4/LFXIN                 | 57  | General-purpose digital I/O                             |

|                            |     | Input terminal for crystal oscillator XT1               |

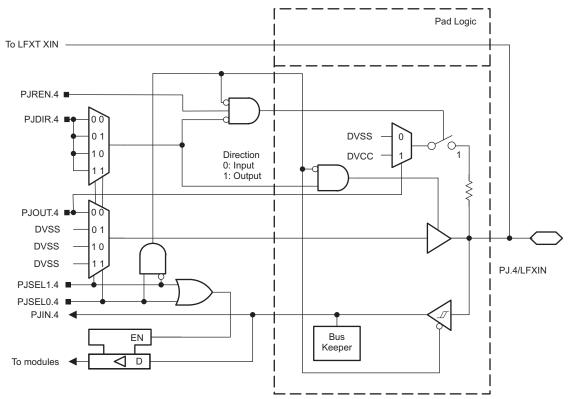

| PJ.5/LFXOUT                | 58  | General-purpose digital I/O                             |

|                            |     | Output terminal of crystal oscillator XT1               |

| AVSS2                      | 59  | Analog ground supply                                    |

|                            |     | General-purpose digital I/O                             |

| P4.0/UCB1SIMO/UCB1SDA/MCLK | 60  | USCI_B1: Slave in, master out (SPI mode)                |

|                            |     | USCI_B1: I <sup>2</sup> C data (I <sup>2</sup> C mode)  |

|                            |     | MCLK output                                             |

| P4.1/UCB1SOMI/UCB1SCL/ACLK |     | General-purpose digital I/O                             |

|                            | 61  | USCI_B1: Slave out, master in (SPI mode)                |

|                            |     | USCI_B1: I <sup>2</sup> C clock (I <sup>2</sup> C mode) |

|                            |     | ACLK output                                             |

| DVSS3                      | 62  | Digital ground supply                                   |

| DVCC3                      | 63  | Digital power supply                                    |

| TERMINAL                          |     |                                                                                          |

|-----------------------------------|-----|------------------------------------------------------------------------------------------|

| NAME                              |     | DESCRIPTION                                                                              |

| NAME                              | NO. |                                                                                          |

| P4.2/UCA0SIMO/UCA0TXD/<br>UCB1CLK |     | General-purpose digital I/O                                                              |

|                                   | 64  | USCI_A0: Slave in, master out (SPI mode)                                                 |

|                                   |     | USCI_A0: Transmit data (UART mode)                                                       |

|                                   |     | USCI_B1: Clock signal input (SPI slave mode), Clock signal output (SPI master mode)      |

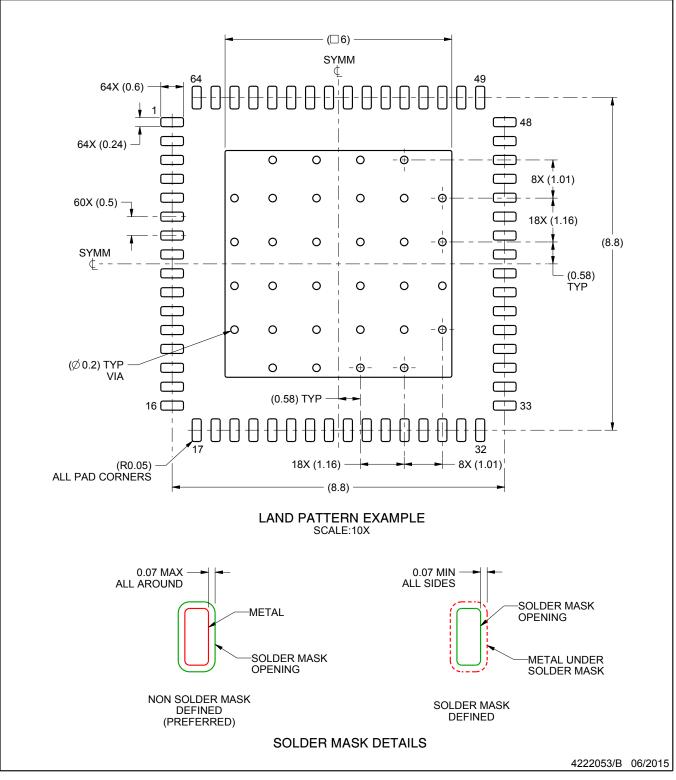

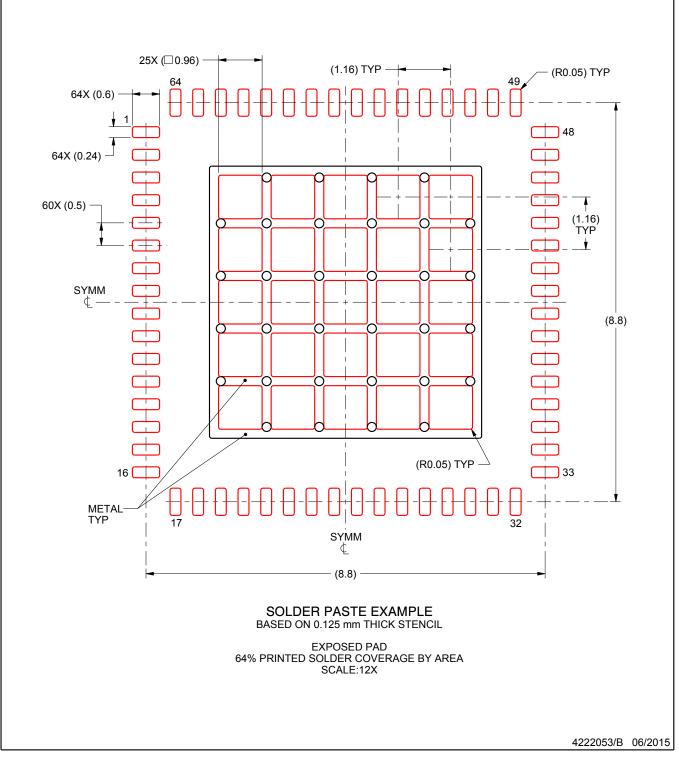

| Thermal pad                       | Pad | RGC package only. QFN package exposed thermal pad. TI recommends connection to $V_{SS}.$ |

#### **Pin Multiplexing** 3.3

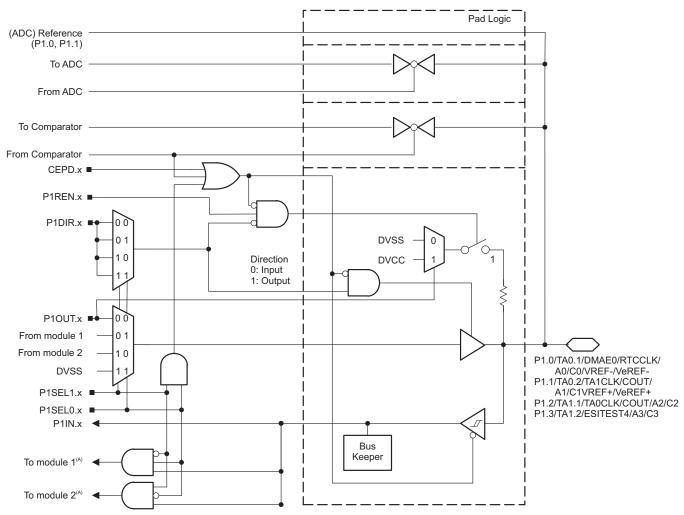

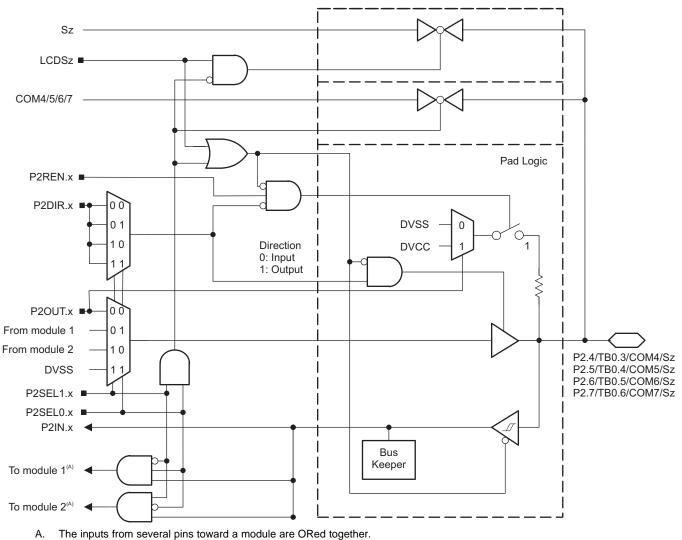

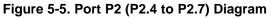

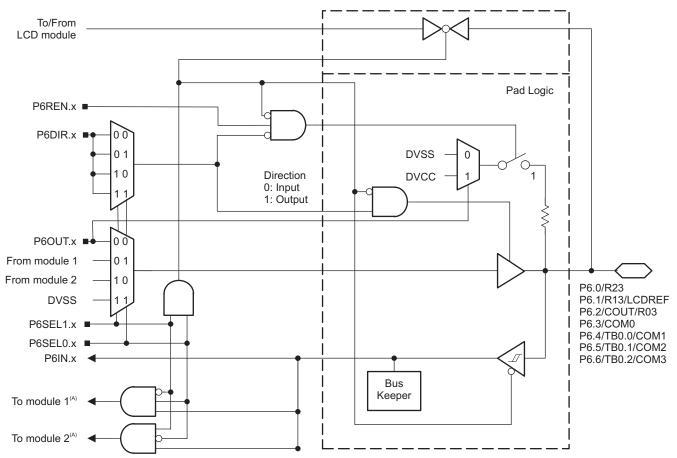

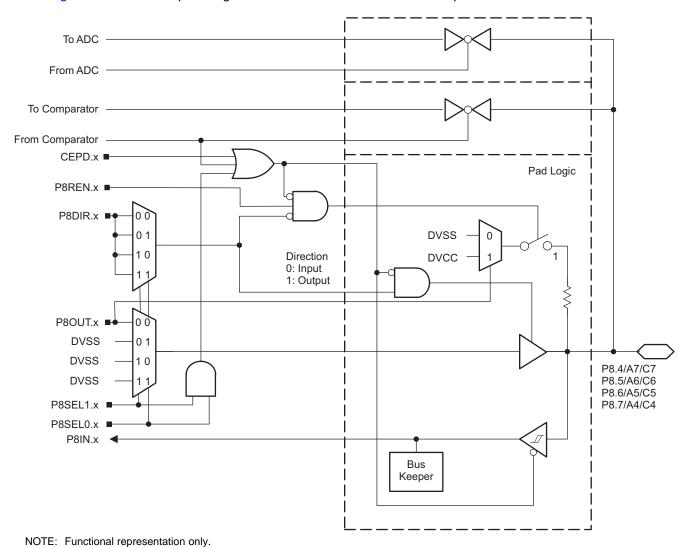

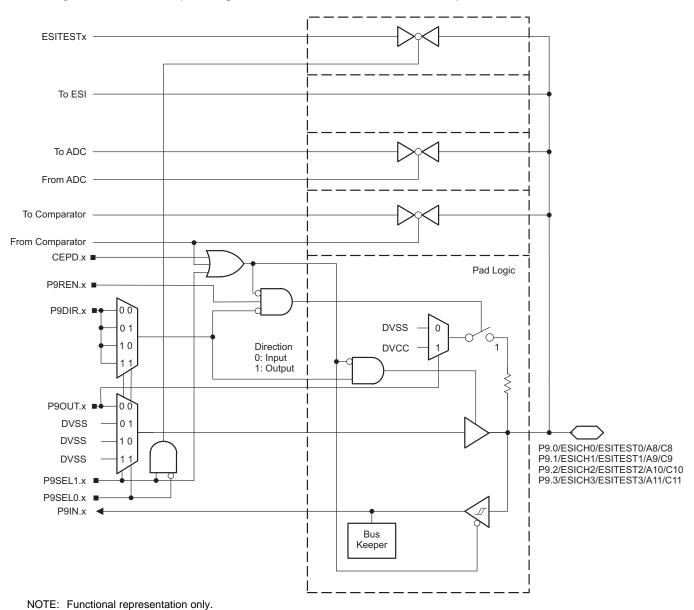

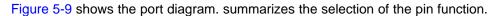

Pin multiplexing for these devices is controlled by both register settings and operating modes (for example, if the device is in test mode). For details of the settings for each pin and schematics of the multiplexed ports, see Section 5.11.24.

#### **Connection of Unused Pins** 3.4

Table 3-2 lists the correct termination of all unused pins.

| COMMENT |

|---------|

|         |

Table 3-2. Connection of Unused Pins<sup>(1)</sup>

| PIN                                          | POTENTIAL              | COMMENT                                                                                                                                                                                                   |

|----------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AVCC                                         | DV <sub>CC</sub>       |                                                                                                                                                                                                           |

| AVSS                                         | DV <sub>SS</sub>       |                                                                                                                                                                                                           |

| Px.0 to Px.7                                 | Open                   | Switched to port function, output direction (PxDIR.n = 1)                                                                                                                                                 |

| R33/LCDCAP                                   | $DV_{SS}$ or $DV_{CC}$ | If not used the pin can be tied to either supplies.                                                                                                                                                       |

| ESIDVCC                                      | DV <sub>CC</sub>       |                                                                                                                                                                                                           |

| ESIDVSS                                      | DV <sub>SS</sub>       |                                                                                                                                                                                                           |

| ESICOM                                       | Open                   |                                                                                                                                                                                                           |

| ESICI                                        | Open                   |                                                                                                                                                                                                           |

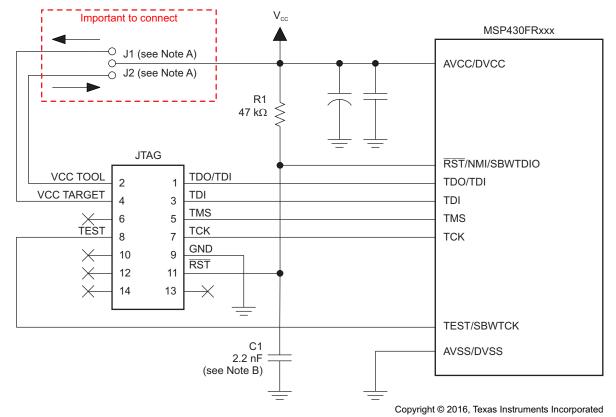

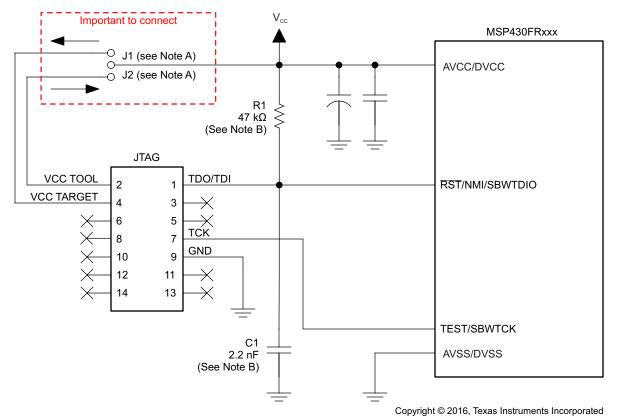

| RST/NMI                                      | $DV_{CC}$ or $V_{CC}$  | 47-kΩ pullup or internal pullup selected with 2.2-nF (10-nF <sup>(2)</sup> ) pulldown.                                                                                                                    |

| PJ.0/TDO<br>PJ.1/TDI<br>PJ.2/TMS<br>PJ.3/TCK | Open                   | The JTAG pins are shared with general-purpose I/O function (PJ.x). If not being used, these should be switched to port function, output direction. When used as JTAG pins, these pins should remain open. |

| TEST                                         | Open                   | This pin always has an internal pulldown enabled.                                                                                                                                                         |

(1) Any unused pin with a secondary function that is shared with general-purpose I/O should follow the Px.0 to Px.7 unused pin connection guidelines.

(2) The pulldown capacitor should not exceed 2.2 nF when using devices with Spy-Bi-Wire interface in Spy-Bi-Wire mode or in 4-wire JTAG mode with TI tools like FET interfaces or GANG programmers. If JTAG or Spy-Bi-Wire access is not needed, up to a 10-nF pulldown capacitor may be used.

# 4 Specifications

## 4.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating junction temperature range (unless otherwise noted)

|                                                              | MIN  | MAX                                  | UNIT |

|--------------------------------------------------------------|------|--------------------------------------|------|

| Voltage applied at DVCC and AVCC pins to V <sub>SS</sub>     | -0.3 | 4.1                                  | V    |

| Voltage difference between DVCC and AVCC pins <sup>(2)</sup> |      | ±0.3                                 | V    |

| Voltage applied to any pin <sup>(3)</sup>                    | -0.3 | V <sub>CC</sub> + 0.3 V<br>(4.1 max) | V    |

| Diode current at any device pin                              |      | ±2                                   | mA   |

| Storage temperature, T <sub>stg</sub> <sup>(4)</sup>         | -55  | 125                                  | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Voltage differences between DVCC and AVCC exceeding the specified limits may cause malfunction of the device including erroneous writes to RAM and FRAM.

(3) All voltage values are with respect to V<sub>SS</sub>, unless otherwise noted.

(4) Higher temperature may be applied during board soldering according to the current JEDEC J-STD-020 specification with peak reflow temperatures not higher than classified on the device label on the shipping boxes or reels.

## 4.2 ESD Ratings

|        |                         |                                                                                | VALUE | UNIT |

|--------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| V      |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±1000 | V    |

| V(ESD) | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±250  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as ±1000 V may actually have higher performance.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Pins listed as ±250 V may actually have higher performance.

## 4.3 Recommended Operating Conditions

Typical data are based on  $V_{CC} = 3 \text{ V}$ ,  $T_J = 25^{\circ}\text{C}$  unless otherwise noted.

|                     |                                                    |                                                                    | MIN                | NOM | MAX               | UNIT |

|---------------------|----------------------------------------------------|--------------------------------------------------------------------|--------------------|-----|-------------------|------|

| V <sub>CC</sub>     | Supply voltage range applied at all DVCC, A        | VCC, and ESIDVCC pins <sup>(1)</sup> <sup>(2)</sup> <sup>(3)</sup> | 1.8 <sup>(4)</sup> |     | 3.6               | V    |

| V <sub>SS</sub>     | Supply voltage applied at all DVSS, AVSS, a        | nd ESIDVSS pins                                                    |                    | 0   |                   | V    |

| TJ                  | Operating junction temperature                     |                                                                    | -55                |     | 95                | °C   |

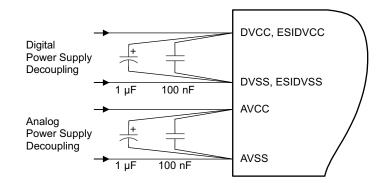

| C <sub>DVCC</sub>   | Capacitor value at DVCC and ESIDVCC <sup>(5)</sup> |                                                                    | 1_20%              |     |                   | μF   |

| 4                   | Processor frequency (maximum MCLK                  | No FRAM wait states (NWAITSx = 0)                                  | 0                  |     | 8 <sup>(7)</sup>  |      |

| <sup>†</sup> SYSTEM | frequency) <sup>(6)</sup>                          | With FRAM wait states (NWAITSx = 1) <sup>(8)</sup>                 | 0                  |     | 16 <sup>(9)</sup> | MHz  |

| f <sub>ACLK</sub>   | Maximum ACLK frequency                             |                                                                    |                    |     | 50                | kHz  |

| f <sub>SMCLK</sub>  | Maximum SMCLK frequency                            |                                                                    |                    |     | 16 <sup>(9)</sup> | MHz  |

(1) TI recommends powering the DVCC, AVCC, and ESIDVCC pins from the same source. At a minimum, during power up, power down, and device operation, the voltage difference between DVCC, AVCC, and ESIDVCC must not exceed the limits specified in *Absolute Maximum Ratings*. Exceeding the specified limits may cause malfunction of the device including erroneous writes to RAM and FRAM.

(2) See Table 4-1 for additional important information.

(3) Modules may have a different supply voltage range specification. See the specification of each module in this data sheet.

(4) The minimum supply voltage is defined by the supervisor SVS levels. See Table 4-2 for the exact values.

(5) Connect a low-ESR capacitor with at least the value specified and a maximum tolerance of 20% as close as possible to the DVCC and ESIDVCC pins.

(6) Modules may have a different maximum input clock specification. See the specification of each module in this data sheet.

(7) DCO settings and HF crystals with a typical value less than or equal to the specified MAX value are permitted.

(8) Wait states only occur on actual FRAM accesses; that is, on FRAM cache misses. RAM and peripheral accesses are always executed without wait states.

(9) DCO settings and HF crystals with a typical value less than or equal to the specified MAX value are permitted. If a clock sources with a larger typical value is used, the clock must be divided in the clock system.

SLASEC9-APRIL 2017

#### Active Mode Supply Current Into V<sub>cc</sub> Excluding External Current 4.4

over recommended operating junction temperature (unless otherwise noted)<sup>(1)</sup> <sup>(2)</sup>

|                                                              |                                 |                 |                                 | FREQUENCY (f <sub>MCLK</sub> = f <sub>SMCLK</sub> ) |                                 |            |                               |            |                             |       |                             |       |      |

|--------------------------------------------------------------|---------------------------------|-----------------|---------------------------------|-----------------------------------------------------|---------------------------------|------------|-------------------------------|------------|-----------------------------|-------|-----------------------------|-------|------|

| PARAMETER                                                    | EXECUTION<br>MEMORY             | V <sub>cc</sub> | 1 MH<br>0 WA<br>STAT<br>(NWAITS | AIT<br>ES                                           | 4 MI<br>0 WA<br>Stat<br>(NWAITS | AIT<br>TES | 8 M<br>0 W<br>Stat<br>(NWAITS | AIT<br>TES | 12 M<br>1 WAIT S<br>(NWAITS | STATE | 16 M<br>1 WAIT S<br>(NWAITS | STATE | UNIT |

|                                                              |                                 |                 | TYP                             | MAX                                                 | ТҮР                             | MAX        | TYP                           | MAX        | ТҮР                         | MAX   | TYP                         | MAX   |      |

| I <sub>AM, FRAM_UNI</sub><br>(Unified memory) <sup>(3)</sup> | FRAM                            | 3.0 V           | 210                             |                                                     | 640                             |            | 1220                          |            | 1475                        |       | 1845                        |       | μΑ   |

| I <sub>AM, FRAM</sub> (0%) <sup>(4) (5)</sup>                | FRAM<br>0% cache hit<br>ratio   | 3.0 V           | 375                             |                                                     | 1290                            |            | 2525                          |            | 2100                        |       | 2675                        |       | μA   |

| I <sub>AM, FRAM</sub> (50%) <sup>(4) (5)</sup>               | FRAM<br>50% cache hit<br>ratio  | 3.0 V           | 240                             |                                                     | 745                             |            | 1440                          |            | 1575                        |       | 1990                        |       | μΑ   |

| I <sub>AM, FRAM</sub> (66%) <sup>(4) (5)</sup>               | FRAM<br>66% cache hit<br>ratio  | 3.0 V           | 200                             |                                                     | 560                             |            | 1070                          |            | 1300                        |       | 1620                        |       | μΑ   |

| I <sub>AM, FRAM</sub> (75%) <sup>(4) (5)</sup>               | FRAM<br>75% cache hit<br>ratio  | 3.0 V           | 170                             | 255                                                 | 480                             |            | 890                           | 1085       | 1155                        | 1310  | 1420                        | 1620  | μA   |

| I <sub>AM, FRAM</sub> (100% <sup>(4) (5)</sup>               | FRAM<br>100% cache hit<br>ratio | 3.0 V           | 110                             |                                                     | 235                             |            | 420                           |            | 640                         |       | 730                         |       | μA   |

| I <sub>AM, RAM</sub> <sup>(6)</sup> <sup>(5)</sup>           | RAM                             | 3.0 V           | 130                             |                                                     | 320                             |            | 585                           |            | 890                         |       | 1070                        |       | μA   |

| I <sub>AM, RAM only</sub> (7) (5)                            | RAM                             | 3.0 V           | 100                             | 180                                                 | 290                             |            | 555                           |            | 860                         |       | 1040                        | 1300  | μA   |

(1) All inputs are tied to 0 V or to V<sub>CC</sub>. Outputs do not source or sink any current.

Characterized with program executing typical data processing. (2)

$f_{ACLK}$  = 32768 Hz,  $f_{MCLK}$  =  $f_{SMCLK}$  =  $f_{DCO}$  at specified frequency, except for 12 MHz. For 12 MHz,  $f_{DCO}$  = 24 MHz and  $f_{MCLK} = f_{SMCLK} = f_{DCO} / 2.$

At MCLK frequencies above 8 MHz, the FRAM requires wait states. When wait states are required, the effective MCLK frequency (f<sub>MCLK.eff</sub>) decreases. The effective MCLK frequency also depends on the cache hit ratio. SMCLK is not affected by the number of wait states or the cache hit ratio.

The following equation can be used to compute f<sub>MCLK.eff</sub>:

$f_{MCLK,eff} = f_{MCLK} / [wait states x (1 - cache hit ratio) + 1]$ For example, with 1 wait state and 75% cache hit ratio  $f_{MCKL,eff} = f_{MCLK} / [1 x (1 - 0.75) + 1] = f_{MCLK} / 1.25.$

Represents typical program execution. Program and data reside entirely in FRAM. All execution is from FRAM.

(4)Program resides in FRAM. Data resides in SRAM. Average current dissipation varies with cache hit-to-miss ratio as specified. Cache hit ratio represents number cache accesses divided by the total number of FRAM accesses. For example, a 75% ratio implies three of every four accesses is from cache, and the remaining are FRAM accesses.

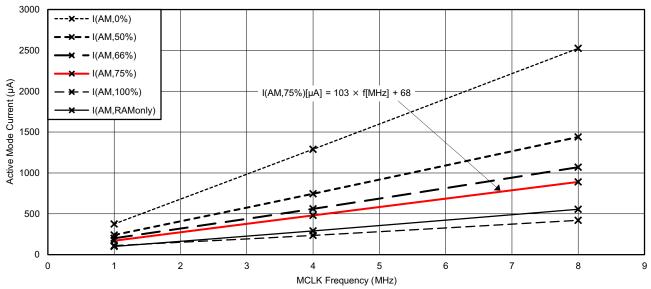

See Figure 4-1 for typical curves. Each characteristic equation shown in the graph is computed using the least squares method for best (5) linear fit using the typical data shown in Section 4.4.

(6) Program and data reside entirely in RAM. All execution is from RAM.

(7) Program and data reside entirely in RAM. All execution is from RAM. FRAM is off.

# 4.5 Typical Characteristics, Active Mode Supply Currents

I(AM, cache hit ratio): Program resides in FRAM. Data resides in SRAM. Average current dissipation varies with cache hit-to-miss ratio as specified. Cache hit ratio represents number cache accesses divided by the total number of FRAM accesses. For example, a 75% ratio implies three of every four accesses is from cache, and the remaining are FRAM accesses.

I(AM, RAMonly): Program and data reside entirely in RAM. All execution is from RAM. FRAM is off.

Figure 4-1. Typical Active Mode Supply Currents, No Wait States

# 4.6 Low-Power Mode (LPM0, LPM1) Supply Currents Into V<sub>cc</sub> Excluding External Current

over recommended operating junction temperature (unless otherwise noted)<sup>(1) (2)</sup>

|           |                 | FREQUENCY (f <sub>SMCLK</sub> ) |     |      |     |      |     |      |     |      |     |      |

|-----------|-----------------|---------------------------------|-----|------|-----|------|-----|------|-----|------|-----|------|

| PARAMETER | V <sub>cc</sub> | 1 MF                            | łz  | 4 MF | łz  | 8 MF | łz  | 12 M | Hz  | 16 M | Hz  | UNIT |

|           |                 | TYP                             | MAX | TYP  | MAX | TYP  | MAX | TYP  | MAX | TYP  | MAX |      |

|           | 2.2 V           | 75                              |     | 105  |     | 165  |     | 250  |     | 230  |     |      |

| ILPM0     | 3.0 V           | 85                              | 120 | 115  |     | 175  |     | 260  |     | 240  | 275 | μA   |

|           | 2.2 V           | 40                              |     | 65   |     | 130  |     | 215  |     | 195  |     |      |

| ILPM1     | 3.0 V           | 40                              | 65  | 65   |     | 130  |     | 215  |     | 195  | 220 | μA   |

(1) All inputs are tied to 0 V or to V<sub>CC</sub>. Outputs do not source or sink any current.

(2) Current for watchdog timer clocked by SMCLK included.

f<sub>ACLK</sub> = 32768 Hz, f<sub>MCLK</sub> = 0 MHz, f<sub>SMCLK</sub> = f<sub>DCO</sub> at specified frequency, except for 12 MHz: here f<sub>DCO</sub> = 24 MHz and f<sub>SMCLK</sub> = f<sub>DCO</sub> / 2.

#### 4.7 Low-Power Mode (LPM2, LPM3, LPM4) Supply Currents (Into V<sub>cc</sub>) Excluding External Current

over recommended ranges of supply voltage and operating junction temperature (unless otherwise noted)<sup>(1)</sup>

|                         |                                                                       |       | TEMPERATURE (T <sub>J</sub> ) |     |      |     |      |     |      |      |      |

|-------------------------|-----------------------------------------------------------------------|-------|-------------------------------|-----|------|-----|------|-----|------|------|------|

|                         | PARAMETER                                                             | Vcc   | V <sub>CC</sub> –55°C         |     | 25°C | ;   | 60°C |     | 95°C |      | UNIT |

|                         |                                                                       |       | TYP                           | MAX | TYP  | MAX | TYP  | MAX | TYP  | MAX  |      |

|                         | Low-power mode 2, 12-pF crystal <sup>(2)</sup> (3) (4)                | 2.2 V | 0.6                           |     | 1.2  |     | 3.1  |     | 8.8  |      |      |

| ILPM2,XT12              | crystal <sup>(2) (3) (4)</sup>                                        | 3.0 V | 0.6                           |     | 1.2  | 2.2 | 3.1  |     | 8.8  | 20.8 | μA   |

|                         | Low-power mode 2, 3.7-pF                                              | 2.2 V | 0.5                           |     | 1.1  |     | 3.0  |     | 8.7  |      |      |

| I <sub>LPM2,XT3.7</sub> | crystal <sup>(2) (5) (4)</sup>                                        | 3.0 V | 0.5                           |     | 1.1  |     | 3.0  |     | 8.7  |      | μA   |

|                         | Low-power mode 2, VLO,                                                | 2.2 V | 0.3                           |     | 0.9  |     | 2.8  |     | 8.5  |      |      |

| I <sub>LPM2,VLO</sub>   | includes SVS <sup>(6)</sup>                                           | 3.0 V | 0.3                           |     | 0.9  | 2.0 | 2.8  |     | 8.5  | 20.5 | μA   |

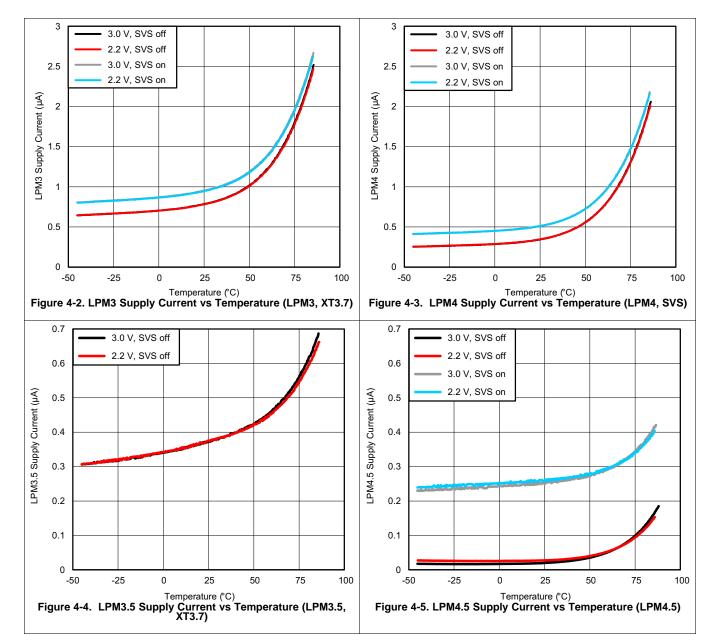

|                         | Low-power mode 3, 12-pF                                               | 2.2 V | 0.5                           |     | 0.7  |     | 1.2  |     | 2.5  |      |      |

| I <sub>LPM3,XT12</sub>  | crystal, excludes SVS <sup>(2) (3) (7)</sup>                          | 3.0 V | 0.5                           |     | 0.7  | 1.0 | 1.2  |     | 2.5  | 6.4  | μA   |

|                         | Low-power mode 3, 3.7-pF                                              | 2.2 V | 0.4                           |     | 0.6  |     | 1.1  |     | 2.4  |      |      |

| I <sub>LPM3,XT3.7</sub> | crystal, excludes SVS <sup>(2) (5) (8)</sup><br>(also see Figure 4-2) | 3.0 V | 0.4                           |     | 0.6  |     | 1.1  |     | 2.4  |      | μA   |

|                         | Low-power mode 3,                                                     | 2.2 V | 0.3                           |     | 0.4  |     | 0.9  |     | 2.2  |      | ٨    |

| I <sub>LPM3,VLO</sub>   | VLO, excludes SVS <sup>(9)</sup>                                      | 3.0 V | 0.3                           |     | 0.4  | 0.8 | 0.9  |     | 2.2  | 6.1  | μA   |

| h puesto e              | Low-power mode 3,                                                     | 2.2 V | 0.3                           |     | 0.4  |     | 0.8  |     | 2.1  |      |      |

| ILPM3,VLO,<br>RAMoff    | VLO, excludes SVS, RAM powered-down completely <sup>(10)</sup>        | 3.0 V | 0.3                           |     | 0.4  | 0.7 | 0.8  |     | 2.1  | 5.2  | μA   |

All inputs are tied to 0 V or to  $V_{CC}.$  Outputs do not source or sink any current. Not applicable for devices with HF crystal oscillator only. (1)

(3) Characterized with a Micro Crystal MS1V-T1K crystal with a load capacitance of 12.5 pF. The internal and external load capacitance are chosen to closely match the required 12.5 pF load.

- Low-power mode 2, crystal oscillator test conditions: (4)Current for watchdog timer clocked by ACLK and RTC clocked by XT1 included. Current for brownout and SVS included. CPUOFF = 1, SCG0 = 0 SCG1 = 1, OSCOFF = 0 (LPM2),

- $f_{XT1} = 32768$  Hz,  $f_{ACLK} = f_{XT1}$ ,  $f_{MCLK} = f_{SMCLK} = 0$  MHz (5) Characterized with a Seiko SSP-T7-FL (SMD) crystal with a load capacitance of 3.7 pF. The internal and external load capacitance are chosen to closely match the required 3.7-pF load.

- Low-power mode 2, VLO test conditions: (6)Current for watchdog timer clocked by ACLK included. RTC disabled (RTCHOLD = 1). Current for brownout and SVS included. CPUOFF = 1, SCGO = 0 SCG1 = 1, OSCOFF = 0 (LPM2),  $f_{XT1} = 0$  Hz,  $f_{ACLK} = f_{VLO}$ ,  $f_{MCLK} = f_{SMCLK} = 0$  MHz

Low-power mode 3, 12-pF crystal excluding SVS test conditions: (7) Current for watchdog timer clocked by ACLK and RTC clocked by XT1 included. Current for brownout included. SVS disabled (SVSHE = 0)

CPUOFF = 1, SCG0 = 1 SCG1 = 1, OSCOFF = 0 (LPM3),

$f_{XT1} = 32768 \text{ Hz}, f_{ACLK} = f_{XT1}, f_{MCLK} = f_{SMCLK} = 0 \text{ MHz}$

Activating additional peripherals increases the current consumption due to active supply current contribution as well as due to additional idle current. See the idle currents specified for the respective peripheral groups. Low-power mode 3, 3.7-pF crystal excluding SVS test conditions:

(8) Current for watchdog timer clocked by ACLK and RTC clocked by XT1 included. Current for brownout included. SVS disabled (SVSHE =

CPUOFF = 1, SCG0 = 1 SCG1 = 1, OSCOFF = 0 (LPM3),

$f_{XT1} = 32768 \text{ Hz}, f_{ACLK} = f_{XT1}, f_{MCLK} = f_{SMCLK} = 0 \text{ MHz}$

Activating additional peripherals increases the current consumption due to active supply current contribution as well as due to additional idle current. See the idle currents specified for the respective peripheral groups.

Low-power mode 3, VLO excluding SVS test conditions: Current for watchdog timer clocked by ACLK included. RTC disabled (RTCHOLD = 1). Current for brownout included. SVS disabled (SVSHE = 0).CPUOFF = 1, SCG0 = 1 SCG1 = 1, OSCOFF = 0 (LPM3),  $f_{XT1} = 0$  Hz,  $f_{ACLK} = f_{VLO}$ ,  $f_{MCLK} = f_{SMCLK} = 0$  MHz Activating additional peripherals increases the current consumption due to active supply current contribution as well as due to additional

idle current. See the idle currents specified for the respective peripheral groups.

(10) Low-power mode 3, VLO excluding SVS test conditions: Current for watchdog timer clocked by ACLK included. RTC disabled (RTCHOLD = 1). RAM disabled (RCCTL0 = 5A55h). Current for brownout included. ŠVS disabled (SVSHE = 0). CPUOFF = 1, SCG0 = 1, SCG1 = 1, OSCOFF = 0 (LPM3),  $f_{XT1} = 0$  Hz,  $f_{ACLK} = f_{VLO}$ ,  $f_{MCLK} = f_{SMCLK} = 0$  MHz

Activating additional peripherals increases the current consumption due to active supply current contribution as well as due to additional idle current. See the idle currents specified for the respective peripheral groups.

www.ti.com

# Low-Power Mode (LPM2, LPM3, LPM4) Supply Currents (Into V<sub>cc</sub>) Excluding External Current *(continued)*

over recommended ranges of supply voltage and operating junction temperature (unless otherwise noted)<sup>(1)</sup>

|                          |                                                                                                                    |                 | TEMPERATURE (T <sub>J</sub> ) |     |       |     |      |     |      |     |      |

|--------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------|-----|-------|-----|------|-----|------|-----|------|

|                          | PARAMETER                                                                                                          | V <sub>cc</sub> | –55°                          | C   | 25°C  | ;   | 60°C | ;   | 95°C | ;   | UNIT |

|                          |                                                                                                                    |                 | TYP                           | MAX | ТҮР   | MAX | TYP  | MAX | TYP  | MAX |      |

|                          | Low-power mode 4, includes                                                                                         | 2.2 V           | 0.4                           |     | 0.5   |     | 0.9  |     | 2.3  |     |      |

| I <sub>LPM4,SVS</sub>    | SVS <sup>(11)</sup>                                                                                                | 3.0 V           | 0.4                           |     | 0.5   | 0.8 | 0.9  |     | 2.3  | 6.2 | μA   |

|                          | Low-power mode 4, excludes                                                                                         | 2.2 V           | 0.2                           |     | 0.3   |     | 0.7  |     | 2.0  |     |      |

| I <sub>LPM4</sub>        | SVS <sup>(12)</sup>                                                                                                | 3.0 V           | 0.2                           |     | 0.3   | 0.6 | 0.7  |     | 2.0  | 6.0 | μA   |

|                          | Low-power mode 4, excludes                                                                                         | 2.2 V           | 0.2                           |     | 0.3   |     | 0.7  |     | 1.9  |     |      |

| LPM4,RAMoff              | SVS, RAM powered-down completely <sup>(13)</sup>                                                                   | 3.0 V           | 0.2                           |     | 0.3   | 0.6 | 0.7  |     | 1.9  | 5.1 | μA   |

| I <sub>IDLE,GroupA</sub> | Additional idle current if one or<br>more modules from Group A<br>(see Table 5-3) are activated in<br>LPM3 or LPM4 | 3.0V            |                               |     | 0.02  |     |      |     | 1.18 | 2.6 | μΑ   |

| I <sub>IDLE,GroupB</sub> | Additional idle current if one or<br>more modules from Group B<br>(see Table 5-3) are activated in<br>LPM3 or LPM4 | 3.0V            |                               |     | 0.02  |     |      |     | 1.15 | 2.6 | μΑ   |

| I <sub>IDLE,GroupC</sub> | Additional idle current if one or<br>more modules from Group C<br>(see Table 5-3) are activated in<br>LPM3 or LPM4 | 3.0V            |                               |     | 0.02  |     |      |     | 1.5  | 2.8 | μΑ   |

| I <sub>IDLE,GroupD</sub> | Additional idle current if one or<br>more modules from Group D<br>(see Table 5-3) are activated in<br>LPM3 or LPM4 | 3.0V            |                               |     | 0.015 |     |      |     | 1.4  | 2.4 | μΑ   |

(11) Low-power mode 4 including SVS test conditions:

Current for brownout and SVS included (SVSHE = 1). CPUOFF = 1, SCG0 = 1 SCG1 = 1, OSCOFF = 1 (LPM4),

$f_{XT1} = 0$  Hz,  $f_{ACLK} = 0$  Hz,  $f_{MCLK} = f_{SMCLK} = 0$  MHz

Activating additional peripheral increases the current consumption due to active supply current contribution as well as due to additional idle current. See the idle currents specified for the respective peripheral groups.

(12) Low-power mode 4 excluding SVS test conditions: Current for brownout included. SVS disabled (SVSHE = 0). CPUOFF = 1, SCG0 = 1 SCG1 = 1, OSCOFF = 1 (LPM4),

$f_{XT1} = 0 \text{ Hz}, f_{ACLK} = 0 \text{ Hz}, f_{MCLK} = f_{SMCLK} = 0 \text{ MHz}$

Activating additional peripherals increases the current consumption due to active supply current contribution as well as due to additional idle current. See the idle currents specified for the respective peripheral groups.

(13) Low-power mode 4 excluding SVS test conditions:

Current for brownout included. SVS disabled (SVSHE = 0). RAM disabled (RCCTL0 = 5A55h).

CPUOFF = 1, SCG0 = 1 SCG1 = 1, OSCOFF = 1 (LPM4),

$f_{XT1} = 0$  Hz,  $f_{ACLK} = 0$  Hz,  $f_{MCLK} = f_{SMCLK} = 0$  MHz

Activating additional peripherals increases the current consumption due to active supply current contribution as well as due to additional idle current. See the idle currents specified for the respective peripheral groups.

SLASEC9-APRIL 2017

www.ti.com

# 4.8 Low-Power Mode With LCD Supply Currents (Into V<sub>cc</sub>) Excluding External Current

over recommended ranges of supply voltage and operating junction temperature (unless otherwise noted)

|                                             | 0 11 3                                                                                                                                                          |                 |       |                               |      |     |      |     |      |     |      |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------|-------------------------------|------|-----|------|-----|------|-----|------|

|                                             |                                                                                                                                                                 |                 |       | TEMPERATURE (T <sub>J</sub> ) |      |     |      |     |      |     |      |

|                                             | PARAMETER                                                                                                                                                       | V <sub>cc</sub> | –55°( | C                             | 25°C | :   | 60°C | ;   | 95°C | ;   | UNIT |

|                                             |                                                                                                                                                                 |                 | ТҮР   | MAX                           | TYP  | MAX | TYP  | MAX | TYP  | MAX |      |

| I <sub>LPM3,XT12</sub><br>LCD,<br>ext. bias | Low-power mode 3 (LPM3)<br>current,12-pF crystal, LCD 4-<br>mux mode, external biasing,<br>excludes SVS <sup>(1)</sup> <sup>(2)</sup>                           | 3.0 V           | 0.7   |                               | 0.9  |     | 1.5  |     | 3.1  |     | μA   |

| I <sub>LPM3,XT12</sub><br>LCD,<br>int. bias | Low-power mode 3 (LPM3)<br>current, 12-pF crystal, LCD 4-<br>mux mode, internal biasing,<br>charge pump disabled,<br>excludes SVS <sup>(1)</sup> <sup>(3)</sup> | 3.0 V           | 2.0   |                               | 2.2  | 2.9 | 2.8  |     | 4.4  | 9.3 | μA   |

|                                             | Low-power mode 3 (LPM3)                                                                                                                                         | 2.2 V           | 5.0   |                               | 5.2  |     | 5.8  |     | 7.4  |     |      |

| I <sub>LPM3,XT12</sub><br>LCD,CP            | current,12-pF crystal, LCD 4-<br>mux mode, internal biasing,<br>charge pump enabled, 1/3 bias,<br>excludes SVS <sup>(1)</sup> <sup>(4)</sup>                    | 3.0 V           | 4.5   |                               | 4.7  |     | 5.3  |     | 6.9  |     | μA   |

(1) Current for watchdog timer clocked by ACLK and RTC clocked by XT1 included. Current for brownout included. SVS disabled (SVSHE = 0).

CPUOFF = 1, SCG0 = 1 SCG1 = 1, OSCOFF = 0 (LPM3),

$f_{XT1} = 32768 \text{ Hz}, f_{ACLK} = f_{XT1}, f_{MCLK} = f_{SMCLK} = 0 \text{ MHz}$

Activating additional peripherals increases the current consumption due to active supply current contribution as well as due to additional idle current - idle current of Group containing LCD module already included. See the idle currents specified for the respective peripheral groups.

(2) LCDMx = 11 (4-mux mode), LCDREXT = 1, LCDEXTBIAS = 1 (external biasing), LCD2B = 0 (1/3 bias), LCDCPEN = 0 (charge pump disabled), LCDSSEL = 0, LCDPREx = 101, LCDDIVx = 00011 (f<sub>LCD</sub> = 32768 Hz / 32 / 4 = 256 Hz) Current through external resistors not included (voltage levels are supplied by test equipment).

Even segments S0, S2, ... = 0, odd segments S1, S3, ... = 1. No LCD panel load.

- (3) LCDMx = 11 (4-mux mode), LCDREXT = 0, LCDEXTBIAS = 0 (internal biasing), LCD2B = 0 (1/3 bias), LCDCPEN = 0 (charge pump disabled), LCDSSEL = 0, LCDPREx = 101, LCDDIVx = 00011 (f<sub>LCD</sub> = 32768 Hz / 32 / 4 = 256 Hz) Even segments S0, S2, ...=0, odd segments S1, S3, ... = 1. No LCD panel load.

- (4) LCDMx = 11 (4-mux mode), LCDREXT = 0, LCDEXTBIAS = 0 (internal biasing), LCD2B = 0 (1/3 bias), LCDCPEN = 1 (charge pump enabled), VLCDx = 1000 (V<sub>LCD</sub> = 3 V typical), LCDSSEL = 0, LCDPREx = 101, LCDDIVx = 00011 (f<sub>LCD</sub> = 32768 Hz / 32 / 4 = 256 Hz) Even segments S0, S2, ...=0, odd segments S1, S3, ... = 1. No LCD panel load. C<sub>LCDCAP</sub> = 10 μF

#### 4.9 Low-Power Mode LPMx.5 Supply Currents (Into V<sub>cc</sub>) Excluding External Current

over recommended ranges of supply voltage and operating junction temperature (unless otherwise noted)<sup>(1)</sup>

|              | PARAMETER                                    | V               | –55° | С   | 25°C | ;   | 60°C | >   | 95°C | ;   | UNIT |

|--------------|----------------------------------------------|-----------------|------|-----|------|-----|------|-----|------|-----|------|